結(jié) 構(gòu) 建 模

本章講述Verilog HDL中的結(jié)構(gòu)建模方式。結(jié)構(gòu)建模方式用以下三種實(shí)例語(yǔ)句描述:

? Gate實(shí)例語(yǔ)句

? UDP實(shí)例語(yǔ)句

? Module實(shí)例語(yǔ)句

第5章和第6章已經(jīng)討論了門(mén)級(jí)建模方式和U D P建模方式,本章講述模塊實(shí)例語(yǔ)句。

9.1 模塊

Verilog HDL中,基本單元定義成模塊形式,如下所示 :

m o d u l e m o d u l e _ n a m e(p o r t _ l i s t) ;

D e c l a r a t i o n s _ a n d _ S t a t e m e n t s

e n d m o d u l e

端口隊(duì)列p o rt _ l i s t列出了該模塊通過(guò)哪些端口與外部模塊通信。

9.2 端口

模塊的端口可以是輸入端口、輸出端口或雙向端口。缺省的端口類(lèi)型為線網(wǎng)類(lèi)型(即wire類(lèi)型)。但是,端口可被顯式地指定為線網(wǎng)。輸出或輸入輸出端口能夠被重新聲明為reg型寄存器。無(wú)論是在線網(wǎng)說(shuō)明還是寄存器說(shuō)明中,線網(wǎng)或寄存器必須與端口說(shuō)明中指定的長(zhǎng)度相同。下面是一些端口說(shuō)明實(shí)例。

m o d u l e M i c r o (PC, Instr, NextAddr );

/ /端口說(shuō)明

i n p u t [3:1] P C;

o u t p u t [1:8] I n s t r;

i n o u t [16:1] N e x t A d d r;

/ /重新說(shuō)明端口類(lèi)型:

w i r e [16:1] N e x t A d d r; //該說(shuō)明是可選的,但如果指定了,就必須與它的端口說(shuō)明保持相同長(zhǎng)度。

r e g [1:8] I n s t r;

/ /I n s t r已被重新說(shuō)明為r e g類(lèi)型,因此它能在always 語(yǔ)句或在i n i t i a l語(yǔ)句中賦值。

。 . 。

e n d m o d u l e

9.3 模塊實(shí)例語(yǔ)句

一個(gè)模塊能夠在另外一個(gè)模塊中被引用,這樣就建立了描述的層次。模塊實(shí)例語(yǔ)句形式

如下:

module_name instance_name (p o r t _ a s s o c i a t i o n s) ;

信號(hào)端口可以通過(guò)位置或名稱關(guān)聯(lián);但是關(guān)聯(lián)方式不能夠混合使用。端口關(guān)聯(lián)形式如下:

p o r t _ e x p r / /通過(guò)位置。

.P o r t N a m e (p o r t _ e x p r) / /通過(guò)名稱。

p o rt _ e x p r可以是以下的任何類(lèi)型:

1) 標(biāo)識(shí)符(r e g或n e t)

2) 位選擇

3) 部分選擇

4) 上述類(lèi)型的合并

5) 表達(dá)式(只適用于輸入端口)

在位置關(guān)聯(lián)中,端口表達(dá)式按指定的順序與模塊中的端口關(guān)聯(lián)。在通過(guò)名稱實(shí)現(xiàn)的關(guān)聯(lián)中,模塊端口和端口表達(dá)式的關(guān)聯(lián)被顯式地指定,因此端口的關(guān)聯(lián)順序并不重要。下例使用兩個(gè)半加器模塊構(gòu)造全加器;邏輯圖如圖 9 - 1所示。

在第一個(gè)模塊實(shí)例語(yǔ)句中, H A是模塊的名字 ,h 1是實(shí)例名稱,并且端口按位置關(guān)聯(lián),即

信號(hào)P與模塊(H A)的端口A連接,信號(hào)Q與端口B連接,S 1與S連接,C 1與模塊端口C連接。在第二個(gè)實(shí)例中,端口按名稱關(guān)聯(lián),即模塊( H A)和端口表達(dá)式間的連接是顯示地定義

的。下例是使用不同端口表達(dá)式形式的模塊實(shí)例語(yǔ)句。

Micro M1 (U d I n[3:0], {WrN, RdN}, S t a t u s[0], S t a t u s[ 1 ] ,

& U d O u t [0:7], T x D a t a) ;

這個(gè)實(shí)例語(yǔ)句表示端口表達(dá)式可以是標(biāo)識(shí)符( T x D a t a)、位選擇(S t a t u s[ 0 ]) 、 部分位選擇(U d I n[ 3 : 0 ])、合并({Wr N,R d N})或一個(gè)表達(dá)式(& u d O u t[ 0 : 7 ]);表達(dá)式只能夠連接到輸入端口。

9.3.1 懸空端口

在實(shí)例語(yǔ)句中,懸空端口可通過(guò)將端口表達(dá)式表示為空白來(lái)指定為懸空端口,例如:

DFF d1 ( .Q(Q S), .Q b a r(), .D a t a( D ) ,

.P r e s e t(), .C l o c k(CK)); //名稱對(duì)應(yīng)方式。

DFF d2 (QS, , D, , CK ) ; / /位置對(duì)應(yīng)方式。

/ /輸出端口Q b a r懸空。

/ /輸入端口P r e s e t打開(kāi),其值設(shè)定為z。

在這兩個(gè)實(shí)例語(yǔ)句中,端口Q b a r和P re s e t懸空。

模塊的輸入端懸空,值為高阻態(tài)z。模塊的輸出端口懸空,表示該輸出端口廢棄不用。

9.3.2 不同的端口長(zhǎng)度

當(dāng)端口和局部端口表達(dá)式的長(zhǎng)度不同時(shí),端口通過(guò)無(wú)符號(hào)數(shù)的右對(duì)齊或截?cái)喾绞竭M(jìn)行匹

配。例如:

在對(duì)C h i l d模塊的實(shí)例中, B d l[ 2 ]連接到P b a[ 0 ],B d l[1] 連接到P b a[ 1 ],余下的輸入端口P b a[ 5 ]、P b a[ 4 ]和P b a[ 3 ]懸空,因此為高阻態(tài) z。與之相似,M p r[ 6 ]連接到P p y[ 0 ],M p r[ 5 ]連接到P p y[ 1 ],M p r[4] 連接到P p y[ 2 ]。參見(jiàn)圖9 - 2。

9.3.3 模塊參數(shù)值

當(dāng)某個(gè)模塊在另一個(gè)模塊內(nèi)被引用時(shí),高層模塊能夠改變低層模塊的參數(shù)值。模塊參數(shù)值的改變可采用下述兩種方式:

1) 參數(shù)定義語(yǔ)句(d e f p a r a m);

2) 帶參數(shù)值的模塊引用。

1. 參數(shù)定義語(yǔ)句

參數(shù)定義語(yǔ)句形式如下:

d e f p a r a m hier_path_name1 = v a l u e 1,

hier_path_name2 = v a l u e 2, 。..;

較低層模塊中的層次路徑名參數(shù)可以使用如下語(yǔ)句顯式定義(層次路徑名在下一章中講述)。下面是一個(gè)例。模塊FA和H A已在本節(jié)前面描述過(guò)。

2. 帶參數(shù)值的模塊引用

在這種方法中,模塊實(shí)例語(yǔ)句自身包含有新的參數(shù)值。下面的例子在前幾節(jié)中也出現(xiàn)過(guò),本例中采用帶參數(shù)的模塊引用方式。

模塊實(shí)例語(yǔ)句中參數(shù)值的順序必須與較低層被引用的模塊中說(shuō)明的參數(shù)順序匹配。在模塊TO P 3中,A N D _ D E L AY已被設(shè)置為5,X O R _ D E L AY已被設(shè)置為2。

模塊TO P 3和TO P 4解釋說(shuō)明了帶參數(shù)的模塊引用只能用于將參數(shù)值向下傳遞一個(gè)層次(例如,O R _ D E L AY),但是參數(shù)定義語(yǔ)句能夠用于替換層次中任意一層的參數(shù)值。

應(yīng)注意到:在帶參數(shù)的模塊引用中,參數(shù)的指定方式與門(mén)級(jí)實(shí)例語(yǔ)句中時(shí)延的定義方式相似;但由于對(duì)復(fù)雜模塊的引用時(shí),其實(shí)例語(yǔ)句不能像對(duì)門(mén)實(shí)例語(yǔ)句那樣指定時(shí)延,故此處不會(huì)導(dǎo)致混淆。參數(shù)值還可以表示長(zhǎng)度。下面是通用的 M×N乘法器建模的實(shí)例。

第1個(gè)值8指定了參數(shù)E M的新值,第2個(gè)值6指定了參數(shù)E N的新值。

9.4 外部端口

在迄今為止所見(jiàn)到的模塊定義中,端口表列舉出了模塊外部可見(jiàn)的端口。例如,

A r b、C t r l、M e m _ B l k和B y t e為模塊端口。這些端口同時(shí)也是外部端口,即在實(shí)例中,當(dāng)采用名稱關(guān)聯(lián)方式時(shí),外部端口名稱用于指定相互連接。下面是模塊 S c r a m _ A的實(shí)例。

Scram_A SX( .B y t e(B 1) , .M e m _ B l k(M 1) , .C t r l(C 1) , .A r b(A 1) ) ;

在模塊S c r a m _ A中,外部端口名稱隱式地指定。Verilog HDL中提供顯式方式指定外部端

口名稱。這可以通過(guò)按如下形式指定一個(gè)端口來(lái)完成:

.e x t e r n a l _ p o r t _ n a m e(i n t e r n a l _ p o r t _ n a m e)

下面是同一個(gè)例子,只不過(guò)是顯式地指定外部端口。

模塊S c r a m _ B在此實(shí)例中指定的外部端口是 D a t a、C o n t ro l、M e m _ Wo rd和A d d r。端口表顯式地表明了外部端口和內(nèi)部端口之間的連接。注意外部端口無(wú)需聲明,但是模塊的內(nèi)部端口卻必須聲明。外部端口在模塊內(nèi)不可見(jiàn),但是卻要在模塊實(shí)例語(yǔ)句中使用,而內(nèi)部端口因?yàn)樵谀K中可見(jiàn),所以必須在模塊中說(shuō)明。在模塊實(shí)例語(yǔ)句中,外部端口的使用如下所示:

Scram_B S1 ( .A d d r(A 1) , .D a t a(D 1) , .C o n t r o l(C 1) ,

.M e m _ W o r d(M 1) ) ;

在模塊定義的端口表中,這兩種概念不能混淆,即在模塊定義中所有端口必須指定顯式的端口名稱,或者沒(méi)有一個(gè)端口帶有顯式的端口名稱。如果模塊端口通過(guò)位置連接,則模塊實(shí)例語(yǔ)句中不能使用外部端口名稱。

內(nèi)部端口名稱可以是標(biāo)識(shí)符,也可以是下述類(lèi)型的表達(dá)式:

? 位選擇;

? 部分選擇;

? 位選擇、部分選擇和標(biāo)識(shí)符的合并。

例如,

在S c r a m _ C的模塊定義中,端口表包括部分選擇( A r b[ 0 : 2 ])、標(biāo)識(shí)符( C t r l)、合并({M e m _ B l k[ 0 ],M e m _ B l k[ 1 ] } )和位選擇(B y t e[ 3 ])。在內(nèi)部端口是位選擇、部分選擇或合并的情況下,沒(méi)有隱式地指定外部端口名。因此,在這樣的模塊實(shí)例語(yǔ)句中,模塊端口必須通過(guò)位置關(guān)聯(lián)相互連接。例如,

Scram_C SYA (L 1[ 4 : 6 ] ,C L , M M Y[ 1 : 0 ] ,B T) ;

在這個(gè)實(shí)例語(yǔ)句中,端口通過(guò)位置關(guān)聯(lián)相連接,因此 L 1[ 4∶6 ]連接到A r b[ 0∶2 ],C L連接

到C t r l,M M Y[ 1 ]連接到M e m _ B l k[ 0 ] ,M M Y[ 0 ]連接到M e m _ B l k[ 1 ],B T連接到B y t e[ 3 ]。

若使用端口名稱關(guān)聯(lián)(即當(dāng)內(nèi)部端口不是標(biāo)識(shí)符時(shí)),必須對(duì)模塊中的端口指定外部端口名。如下面的S c r a m _ D模塊定義所示。

在S c r a m _ D模塊實(shí)例語(yǔ)句中,端口既能夠使用位置連接,也能夠使用名稱連接,但是不能混合使用。下例的模塊實(shí)例語(yǔ)句端口通過(guò)名稱連接。

Scram_D SZ ( .D a t a(L 1[ 4 : 6 ] , .C o n t r o l(C L) ,

.M e m _ W o r d(M M Y[ 1 : 0 ],.A d d r(B T) ) ;

模塊中可以只有外部端口而沒(méi)有內(nèi)部端口。即模塊在引用中其外部端口可以懸空,不與內(nèi)部信號(hào)相連。例如:

模塊S c r a m _ E 有兩個(gè)外部端口D a t a和A d d r,這兩個(gè)端口在使用時(shí)被懸空。

一個(gè)內(nèi)部端口是否能與多個(gè)外部端口連接?Verilog HDL允許這樣連接。例如,

內(nèi)部端口C o n d O u t 與兩個(gè)外部端口B和C連接,所以C o n d O u t的值在B和C上都出現(xiàn)。

9.5 舉例

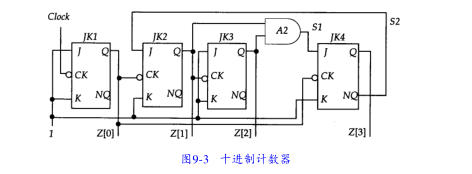

下例采用結(jié)構(gòu)模型描述十進(jìn)制計(jì)數(shù)器。十進(jìn)制計(jì)數(shù)器的邏輯圖如圖 9 - 3所示。

注意常數(shù)作為輸入端口信號(hào)的用法,以及懸空端口。

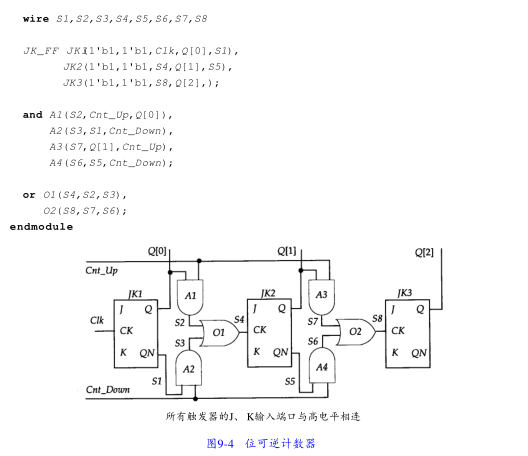

下面是另一個(gè)例子,3位可逆計(jì)數(shù)器的邏輯結(jié)構(gòu)如圖9 - 4所示,其結(jié)構(gòu)描述如下:

責(zé)任編輯:lq6

-

UDP

+關(guān)注

關(guān)注

0文章

327瀏覽量

34007 -

端口

+關(guān)注

關(guān)注

4文章

983瀏覽量

32123 -

Verilog HDL

+關(guān)注

關(guān)注

17文章

126瀏覽量

50447 -

可逆計(jì)數(shù)器

+關(guān)注

關(guān)注

0文章

2瀏覽量

6778

原文標(biāo)題:Verilog入門(mén)-結(jié)構(gòu)建模

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

VirtualLab Fusion案例:傅科刀口測(cè)試的建模

Verilog 與 ASIC 設(shè)計(jì)的關(guān)系 Verilog 代碼優(yōu)化技巧

Verilog與VHDL的比較 Verilog HDL編程技巧

數(shù)字系統(tǒng)設(shè)計(jì)與Verilog HDL

Verilog硬件描述語(yǔ)言參考手冊(cè)

Verilog HDL的基礎(chǔ)知識(shí)

Verilog HDL中的結(jié)構(gòu)建模方式細(xì)述

Verilog HDL中的結(jié)構(gòu)建模方式細(xì)述

評(píng)論