01我們習(xí)以為常的IIC通常是什么樣子?

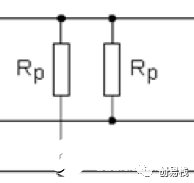

在我們研發(fā)/應(yīng)用工程師眼中,IIC的形象通常是如圖這樣的吧?(你們說是不是?)

是的,對于理想的硬件調(diào)程序,這個層面已經(jīng)基本夠用。(我是已經(jīng)get到了)

02IIC還可以是這樣的

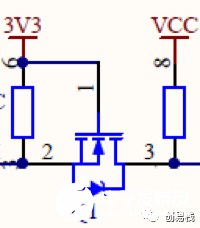

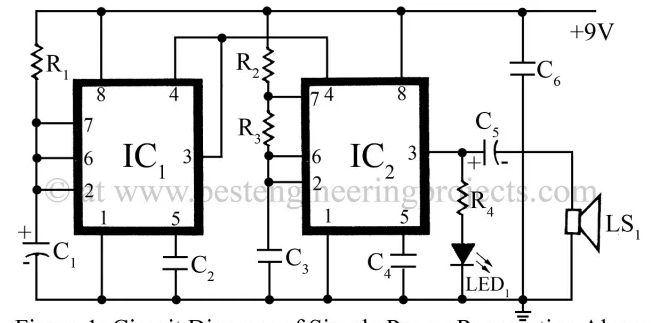

簡單實用的IIC電平匹配電路,原理很簡單、也很巧妙。

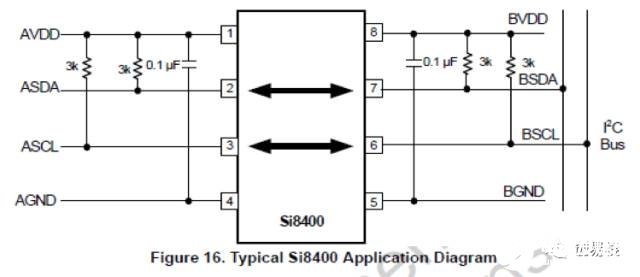

Si8400芯片,做UART或者IIC隔離是很不錯的。做隔離也有實際意義的:

比如涉及強電的板子,需要隔離后的UART口打印調(diào)試信息,方便debug;電容式觸摸按鍵調(diào)試中,某些產(chǎn)品采用隔離的IIC接口(如Azoteq,Cypress等芯片大部分采用IIC)調(diào)試能得到更準(zhǔn)確的數(shù)據(jù)(原理上涉及到人體大地等構(gòu)成的寄生電容,挺有意思,可以看創(chuàng)易棧的觸摸按鍵相關(guān)內(nèi)容)。

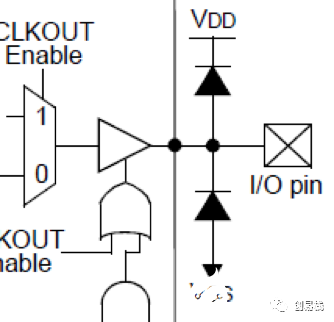

有朋友會問,我見過5V芯片和3V芯片,直接把IIC接在一起的,不需要做電壓匹配呀?

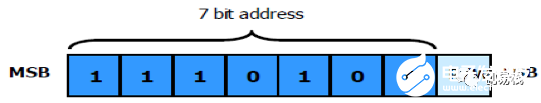

這個不建議用。需要仔細(xì)看數(shù)據(jù)手冊的:一般來說3V芯片的I/O都有如圖的保護結(jié)構(gòu),導(dǎo)致SCL、SDA信號高電平被限制在3V+0.3V,5V芯片經(jīng)常不能正確識別的。

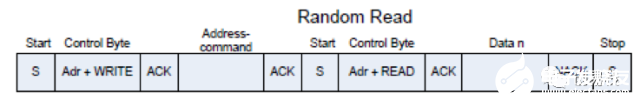

03支持雙電壓的高速IIC接口

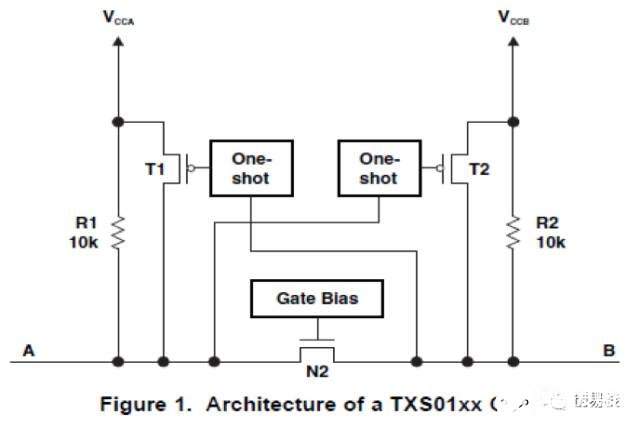

TI的TXS0102帶OE功能的高速IIC接口芯片。

這個有什么好處呢?

當(dāng)然有,除了支持電平匹配;從它的MOS結(jié)構(gòu)也可以看出,對SCL和SDA的上升邊緣有個加速過程,速度可以支持到2Mbps喔。

04觸碰IIC的核心

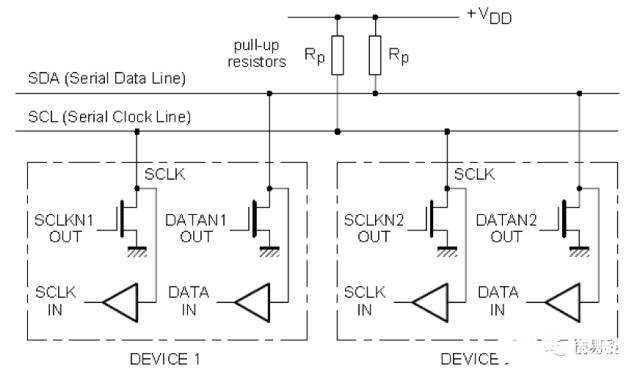

每一個IIC總線器件內(nèi)部的SDA、SCL引腳電路結(jié)構(gòu)都是一樣的,引腳的輸出驅(qū)動與輸入緩沖連在一起。其中輸出為漏極開路的場效應(yīng)管、輸入緩沖為一只高輸入阻抗的同相器[1]。這種電路具有兩個特點:

①由于SDA、SCL為漏極開路結(jié)構(gòu),借助于外部的上拉電阻實現(xiàn)了信號的“線與”邏輯;

②引腳在輸出信號的同時還將引腳上的電平進(jìn)行檢測,檢測是否與剛才輸出一致。為 “時鐘拉伸”和“總線仲裁”提供硬件基礎(chǔ)。

I2C總線接口內(nèi)部結(jié)構(gòu)

IIC設(shè)備對總線的操作僅有“把線路拉到地”——輸出邏輯0。基于IIC總線的設(shè)計,線路上不可能出現(xiàn)電平?jīng)_突現(xiàn)象。如果一設(shè)備發(fā)送邏輯0,其他發(fā)送邏輯1,那么線路看到的只有邏輯0。也就是說,如果出現(xiàn)電平?jīng)_突,發(fā)送邏輯0的始終是“贏家”。總線的物理接法允許主設(shè)備往總線寫數(shù)據(jù)的同事讀取數(shù)據(jù)。這樣兩主設(shè)備爭總線的時候“贏家”并不知道競爭的發(fā)生,只有“輸家”發(fā)現(xiàn)了沖突——當(dāng)寫一個邏輯1,卻讀到了0——而退出競爭。

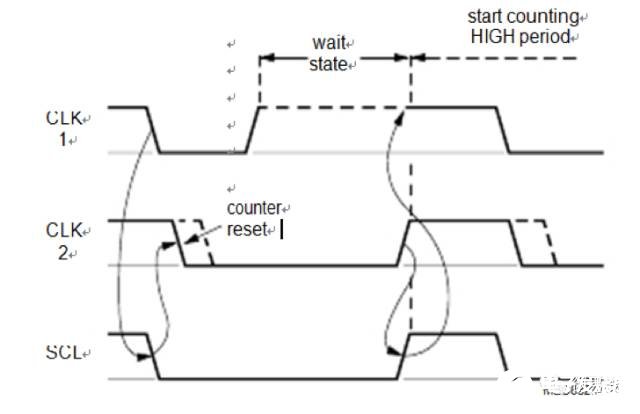

時鐘拉伸(Clock stretching)

如果被控器希望主控器降低傳送速度可以通過將SCL主動拉低延長其低電平時間的方法來通知主控器,當(dāng)主控器在準(zhǔn)備下一次傳送發(fā)現(xiàn)SCL的電平被拉低時就進(jìn)行等待,直至被控器完成操作并釋放SCL線的控制控制權(quán)。這樣以來,主控器實際上受到被控器的時鐘同步控制。可見SCL線上的低電平是由時鐘低電平最長的器件決定;高電平的時間由高電平時間最短的器件決定。這就是時鐘拉伸,它解決了I2C總線的速度同步。

總線仲裁

假設(shè)主控器1要發(fā)送的數(shù)據(jù)DATA1為“101 ……”;主控器2要發(fā)送的數(shù)據(jù)DATA2為“1001 ……”總線被啟動后兩個主控器在每發(fā)送一個數(shù)據(jù)位時都要對自己的輸出電平進(jìn)行檢測,只要檢測的電平與自己發(fā)出的電平一致,他們就會繼續(xù)占用總線。在這種情況下總線還是得不到仲裁。當(dāng)主控器1發(fā)送第3位數(shù)據(jù)“1”時(主控器2發(fā)送“0” ),由于“線與”的結(jié)果SDA上的電平為“0”,這樣當(dāng)主控器1檢測自己的輸出電平時,就會測到一個與自身不相符的“0”電平。這時主控器1只好放棄對總線的控制權(quán);因此主控器2就成為總線的唯一主宰者。

總結(jié)

① 對于整個仲裁過程主控器1和主控器2都不會丟失數(shù)據(jù);

② 各個主控器沒有對總線實施控制的優(yōu)先級別;

③總線控制隨即而定,他們遵循“低電平優(yōu)先”的原則,即誰先發(fā)送低電平誰就會掌握對總線的控制權(quán)。

根據(jù)上面的描述,“時鐘拉伸”與“總線仲裁”可以總結(jié)如下規(guī)律:

①主控器通過檢測SCL上的電平來調(diào)節(jié)與從器件的速度同步問題——時鐘拉伸;

②主控器通過檢測SDA上自身發(fā)送的電平來判斷是否發(fā)生總線“沖突”——總線仲裁。因此,I2C總線的“時鐘同步”與“總線仲裁”是靠器件自身接口的特殊結(jié)構(gòu)得以實現(xiàn)的。

編輯:lyn

-

硬件

+關(guān)注

關(guān)注

11文章

3328瀏覽量

66223 -

IIC

+關(guān)注

關(guān)注

11文章

300瀏覽量

38337 -

IIC接口

+關(guān)注

關(guān)注

0文章

23瀏覽量

11686

發(fā)布評論請先 登錄

相關(guān)推薦

簡單了解SDK與APK的區(qū)別

IIC信號線需要增加上拉電阻,是因為IIC的IO是什么

PCB打樣不簡單:這些特殊工藝你知道嗎?

簡單電源恢復(fù)報警電路說明

熱電阻與熱電偶區(qū)別與測溫原理分析

如何確定芯片的方向 最簡單的芯片原理

【CW32學(xué)習(xí)筆記】IIC接口-主機發(fā)送

你眼中簡單的IIC,其實并不簡單

你眼中簡單的IIC,其實并不簡單

評論