本文詳細(xì)介紹了DM368 視頻前端支持的輸入數(shù)字信號格式。并以MT9D131 和PC VGA 信號為例,將兩者的時序和 DM368 視頻前端配置參數(shù)一一匹配。同時介紹了如何合理配置和使用 VD 中斷,為 DM368 用戶正確采集數(shù)據(jù)提供了參考。本文內(nèi)容也可以給 DM8127、DM385 芯片的用戶在使用視頻攝像并行輸入口采集時提供幫助。

1 前言

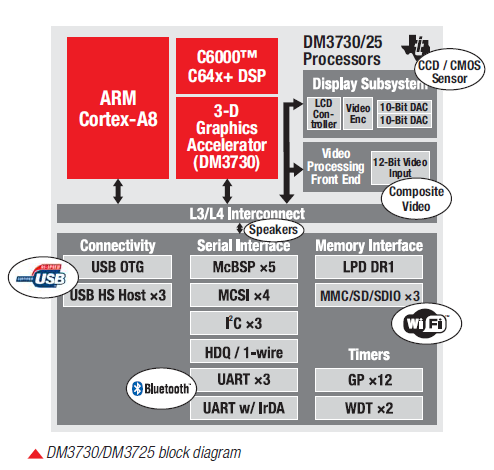

DM368 是TI達(dá)芬奇系列芯片中的一顆,被廣泛的使用在IPNC(IP net camera 網(wǎng)絡(luò)攝像機(jī))的應(yīng)用領(lǐng)域里。對于IPNC 應(yīng)用,首先就需要將視頻信號送入DM368 里面,這就需要使用到DM368 的視頻前端(VPFE - Video Processing Front End)。DM368 的視頻前端主要包含了IPIPEIF(Image Pipe Interface 圖像管道接口),ISIF(Image Signal Interface 圖像信號接口),IPIPE (Image Pipe 圖像管道),Resizer(縮放器)四個部分。

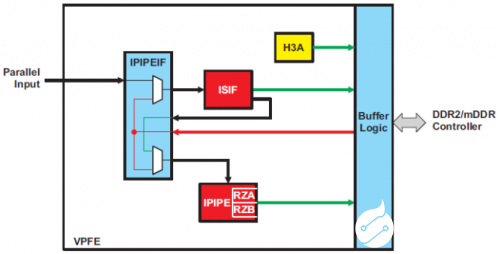

IPIPEIF 功能是數(shù)據(jù)通路連接,以及把數(shù)據(jù)整合成后端模塊接口可以接入的格式/大小。ISIF 是視頻信號的輸入口,可以支持Bayer 格式的RAW 數(shù)據(jù)(原始數(shù)據(jù))或者是YUV 的數(shù)據(jù)的輸入。IPIPE 主要是做ISP 的處理。Resizer 起到了對圖像縮放和圖像存儲格式轉(zhuǎn)換的作用。本文是基于IPIPEIF 將外部并口輸入數(shù)據(jù)送入ISIF 處理的基礎(chǔ)上展開討論。

圖 1. 視頻處理前端

如何將輸入信號和DM368 視頻前端參數(shù)一一對應(yīng)?如何獲取外部的RAW 數(shù)據(jù)以及RAW 轉(zhuǎn)換成的對應(yīng)的YUV 數(shù)據(jù)?如何只采集或者處理圖像中的一部分區(qū)域?如何配置VD 中斷觸發(fā)的時機(jī)?在VD 中斷里面我們應(yīng)該處理什么?希望在閱讀完本文后,你可以找到相應(yīng)的答案。

2 DM368 的前端信號輸入

如果用戶外接傳感器(sensor)輸出RAW 數(shù)據(jù)或者YUV 數(shù)據(jù)到DM368,為了采集到正確的數(shù)據(jù),我們需要了解DM368 的視頻前端是如何解讀信號,以獲得正確的數(shù)據(jù)。如果用戶使用的是FPGA 輸出信號到DM368,那就更需要了解DM368 視頻前端支持的信號格式,正確輸出DM368可以接收的信號。

2.1 輸入信號的物理連接

DM368 視頻前端支持并口的信號輸入,包括PCLK(像素時鐘),8 到16 位數(shù)據(jù)線,HD(行同步)信號,VD(場同步)信號。可以支持最多16 位的Bayer 格式的RAW 數(shù)據(jù)輸入。也可以支持內(nèi)嵌同步或者外部信號同步的8 位或者16 位的YUV422 信號輸入。如果是內(nèi)嵌同步,則不需要接入HD 信號和VD 信號。對于輸入內(nèi)嵌同步的信號,DM368 硬件可以自動解析出數(shù)據(jù)上嵌入的同步信息給芯片內(nèi)部使用。DM368 的PCLK 最高可支持120MHz,可以支持720p60、 1080p30 等分辨率的輸入,也可以支持較大分辨率,例如五百萬、八百萬等分辨率,但幀率是非實時(小于30 幀)的。

DM368 的視頻前端ISIF 可以支持master(主) 模式或者slave (從)模式。所謂master 模式就是PCLK、VD 和HD 由DM368 向外發(fā)出。而slave 模式是外部設(shè)備提供PCLK、VD 和HD 信號給DM368。在實際的應(yīng)用里面絕大部分的情況都使用采slave 模式。

2.2 DM368 視頻前端對輸入信號的解析

2.2.1 ISIF 對信號的解析

無論是master 模式還是slave 模式,DM368 的視頻前端接口ISIF 對于信號的處理是一樣的。

圖 2. 幀圖像格式

圖2 的時序通常認(rèn)為水平同步和垂直同步信號都為高電平有效,需要配置ISIF 的MODESET. HDPOL=MODESET.VDPOL=0。在這種情況下,水平同步信號寬度為HDW (HD pulse width),以像素為單位。垂直同步信號寬度為 VDW (VD pulse width) ,以行數(shù)為單位。 PLLN(Pixels per line)是每行的像素個數(shù),也就是相鄰兩個行同步信號間的像素個數(shù)。LPFR 是Lines per frame 的縮寫,表示每幀數(shù)據(jù)有多少行,也是相鄰兩個場同步信號之間的行數(shù)。在slave 模式下,PLCK/HD/VD 都是外部輸入的,ISIF 寄存器HDW/VDW/PLLN 是不需要配置的。圖2 中的灰色區(qū)域我們叫做有效數(shù)據(jù)區(qū)域,也就是用戶希望獲得的有效數(shù)據(jù)。而斜線陰影區(qū)域就是消隱區(qū)域。消隱區(qū)域在視頻前端處理中也是必不可少的部分,關(guān)于這點(diǎn)我們會在第3 節(jié)詳細(xì)介紹。

如果你使用的是單次(one shot)模式,或者在連續(xù)(continuous)模式下,你需要保存RAW 數(shù)據(jù),那你就需要配置 SPH( Start pixel horizontal 水平方向起始像素),SLV0/1 (Start line vertical - field 0/1 垂直方向奇偶場起始行),LNH( Number of pixels in line 每行像素個數(shù)),LNV (Number of lines vertical 垂直方向行數(shù))。這是為了告訴DM368 你需要把輸入的圖像的哪部分寫到DDR。也就是說你可以選擇只輸出有效數(shù)據(jù)里面的某一部分到DDR。

SPH 告訴硬件在同步信號有效以后從哪個像素開始寫入DDR。請注意這里的HD 信號有效起始點(diǎn)是指同步信號有效的沿,不是從同步信號脈沖結(jié)束后作為計數(shù)像素的起點(diǎn)。例如,如果HD 信號高電平有效,就是HD 上升沿后開始計數(shù),LNH 個PCLK(也就是像素)后將接收到的數(shù)據(jù)寫入DDR。同樣 SLV0/1 告訴硬件從哪行數(shù)據(jù)開始需要寫入 DDR,LNV 決定了寫多少行數(shù)據(jù)到 DDR。所以調(diào)整ISIF 的SPH,SLV0/1, LNH 和LNV 就可以調(diào)整保存到DDR 上的RAW 數(shù)據(jù)在原圖中的位置,以及 RAW 數(shù)據(jù)段大小(長寬)。如果不需要寫入 RAW 到DDR,那就不需要配置 SPH, SLV0/1 ,LNH 和LNV。

圖2 的時序如果配置為同步信號低電平有效也是可以的。但是如果配置為低電平有效,相關(guān)的參數(shù)就發(fā)生了變化。例如水平同步信號寬度就變?yōu)?PPLN-HDW,垂直同步信號寬度為 LPFR- VDW。SPH 和 SLV0/1 都變成了 0。所以在配置 ISIF 相關(guān)寄存器前首先需要把同步信號的極性確定下來。 要采集到正確的數(shù)據(jù),DM368 采樣數(shù)據(jù)時機(jī)必須和傳感器輸出數(shù)據(jù)的時機(jī)匹配。在DM368 上默認(rèn)是PCLK 的下降沿采樣數(shù)據(jù)。用戶可以通過修改SYSTEM module 寄存器VPSS_CLK_CTRL的PCLK_INV[2] 位來改變 PCLK 采樣沿。

2.2.2 IPIPE 和Resizer 對信號的解析和處理

如果ISIF 直接通過IPIPEIF 連接到IPIPE,那所有的圖像數(shù)據(jù),也就是圖2 里的global frame 都會傳輸?shù)絀PIPE。在IPIPE 里面 用戶需要配置SRC_HPS (Horizontal Start Position ),SRC_VPS(Vertical Start Position),SRC_HSZ( Horizontal Processing Size)和SRC_VSZ( Vertical Processing Size),來確認(rèn)global frame 里面的哪一部分需要IPIPE 來處理。

在resizer 的模塊里面,也有SRC_HPS,SRC_VPS,SRC_HSZ 和SRC_VSZ 可以配置resizer處理的圖像的區(qū)域。如果IPIPE 的輸出到resizer 已經(jīng)是需要處理的區(qū)域,那SRC_HPS,SRC_VPS 就可以配置為0,而resizer 的SRC_HSZ,SRC_VSZ 等于IPIPE 的SRC_HSZ,SRC_VSZ。如果ISIF 的輸出是通過IPIPEIF 直接到resizer(沒有經(jīng)過IPIPE),resizer 的SRC_HPS,SRC_VPS 就不能配置為0 了,需要用戶根據(jù)需要處理的圖像合理的配置resizer 的SRC_HPS,SRC_VPS 寄存器。

2.2.3 RAW 數(shù)據(jù)和YUV 數(shù)據(jù)的匹配

在連續(xù)模式下,用戶同時獲得resizer 輸出的YUV 和ISIF 輸出的RAW,時常有用戶發(fā)現(xiàn)自己保存的RAW 數(shù)據(jù)和Resizer 輸出的YUV 數(shù)據(jù)不匹配,有一定的偏移。這種問題的原因是IPIPE,Resizer 里面的SRC_HPS,SRC_VPS,SRC_HSZ 和SRC_VSZ 和ISIF 里面的寫入DDR 時候配置的偏移和大小不匹配。IPIPE/Resizer 和ISIF 的寄存器本身是沒有直接關(guān)系的,這就需要用戶將它們一一對應(yīng),匹配起來。例如ISIF 輸出的數(shù)據(jù)輸入給IPIPE,為了讓RAW 和YUV 匹配,需要ISIF 的SPH 等于IPIPE 的SRC_HPS,ISIF 的SLV0/1 等于IPIPE 的SRC_VPS,ISIF 的LNH 等于IPIPE 的SRC_ HSZ,ISIF 的LNV 等于IPIPE 的SRC_ VSZ。而Resizer 的SRC_HPS,SRC_VPS 需要配置為0,而resizer 的SRC_HSZ,SRC_VSZ 要等于IPIPE 的SRC_HSZ,SRC_VSZ。

在單次模式下,也就是數(shù)據(jù)通路ISIF-》DDR-》IPIPEIF-》IPIPE(Resizer),由于IPIPE 的輸入是DDR 上的RAW 數(shù)據(jù),有效數(shù)據(jù)的獲取已經(jīng)在ISIF 輸出到DDR 配置里面實現(xiàn)了,IPIPE 里面的處理數(shù)據(jù)的起始位置就可以是(0,0)了。

這樣無論是在連續(xù)模式還是在單次模式下,RAW 數(shù)據(jù)和RAW 輸出轉(zhuǎn)換出的YUV 數(shù)據(jù)就可以完全匹配了。

責(zé)任編輯:gt

-

芯片

+關(guān)注

關(guān)注

455文章

50816瀏覽量

423613 -

接口

+關(guān)注

關(guān)注

33文章

8598瀏覽量

151156 -

攝像機(jī)

+關(guān)注

關(guān)注

3文章

1601瀏覽量

60043

發(fā)布評論請先 登錄

相關(guān)推薦

咨詢一下達(dá)芬奇處理器DM6437的問題

《DM368 視頻前端信號采集詳解》- 該文對理解DM8127/DM38x的并口采集也有幫助

通過DM368輸出的RGB信號,編碼成TMDS,輸出DVI端子,這樣可以嗎?

請教大家DM368處理器+tvp5150am1采集不到視頻數(shù)據(jù)的問題?

求助:有關(guān)DM368的視頻采集壓縮后圖像質(zhì)量差的疑問

tvp7002輸入DM368的信號異常后,DM368無法正常捕獲視頻問題

dm368方案

DM368輸出RGB的設(shè)置

DM368信號時序

DM368支持的輸入輸出最大分辨率分別是多少?

DM368視頻前端支持的輸入數(shù)字信號格式有哪幾種?

TI推出全新視頻處理器TMS320DM368

DM37系列達(dá)芬奇視頻處理器的詳細(xì)資料

TI達(dá)芬奇系列芯片DM368在視頻前端信號采集中的應(yīng)用分析

TI達(dá)芬奇系列芯片DM368在視頻前端信號采集中的應(yīng)用分析

評論