1引 言

列車需要傳輸大量的設備控制和旅客服務信息,隨著這些信息的數量和種類不斷地增長,迫切需要一種大容量,高速度的信息傳輸系統。為此,國際電工委員會(IEC)制定了一項用于規范車載設備數據通信的標準——IEC61375(列車通信網標準),即TCN標準,該標準于1999年6月成為國際標準。目前國際上主要的TCN產品供應商是德國西門子和瑞士Duagon公司,國內的株洲電力機車研究所和大連北車集團電力牽引研究所等單位進行了大量的TCN相關研究工作并取得了豐碩的科研成果。

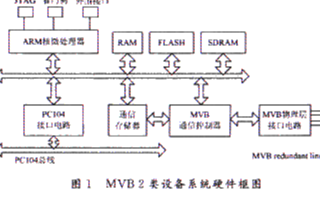

TCN標準推薦在機車上層使用絞線式列車總線WTB,在下層使用多功能車輛總線MVB。MVB總線和機車中的各種電氣設備相連,這些設備按性能可以分為5類,其中二類設備的主要特征是具有消息數據通信的功能。為了實現消息數據通信,需要在實時操作系統的支持下采用軟件編程,利用應用程序接口API等接口來調用網絡協議的各種功能,從而實現消息數據的通信。MVB 2類設備硬件核心采用ARM7內核微處理器NET+50作為主CPU實現系統的總體控制,采用MVBC01芯片作為MVB通信控制器實現鏈路層的數據處理,軟件核心采用嵌入式實時操作系統Nucleus Plus來實現任務管理、中斷管理等上層管理。

2 MVB 2類設備系統硬件設計

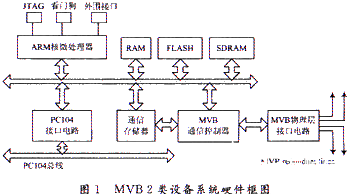

硬件系統設計主要包括應用處理器模塊、通信存儲器模塊、通信控制器模塊、存儲器模塊、PC104接口模塊、物理層接口模塊等幾部分的設計,其中核心模塊是ARM處理器和MVB通信控制器MVBC01。系統硬件設計框圖如圖1所示。

系統硬件各部分電路的功能和設計方法如下:

2.1 應用處理器模塊

應用處理器采用ARM核微處理器NET+50作為核心處理器。NET十50由Netsilicon公司生產,屬于ARM7系列。

[table][/table]NET+50處理器包括一個ARM7TDMI核,32位內部總線,支持所有SRAM,SDRAM,FLASH,E2PROM,有40個可編程I/O接口引腳,16個輸入接口引腳,36個可編程中斷,2個完全獨立的HDLC/UART/SPI串行口以及完整的以太網控制器。

2.2 存儲器模塊

存儲器模塊為ARM處理器NET+50正常工作時提供所需的程序存貯空間,內存空間和數據存儲空間。NET+50集成了內存控制器模塊(Memory Controller Mod-ule),為存儲設備提供無縫連接,系統通過配置內存控制器模塊的控制寄存器和片選CS控制寄存器來實現訪問相應存儲器的信號和邏輯。

本設計中選用大小為16 MB的高速SDRAM為系統提供內存服務,選用大小為512 kB的NVRAM為系統提供數據存儲空間,選用大小為4 MB的FLASH為系統提供程序存儲空間。使用ARM處理器的地址線、數據線以及相應的片選、讀/寫、時鐘線完成對存儲器的尋址。

2.3 通信控制器模塊

通信控制器MVBC是MVB總線上的新一代核心處理器,他獨立于物理層和功能設備,為在總線上的各個設備提供通訊接口和通訊服務,可通過配置應用在符合TCN標準的1,2,3,4類設備中。MVBC把來自于MVB總線的串行化信號轉換為并行的數據字節,也把需發送的字節交由串行化電路發送到傳輸介質上。MVBC可實現數據鏈路層以及一部分傳輸層的數據處理,并通過通訊存儲器來與上層軟件交互。

本系統中MVB通信控制器采用MVBC01 ASIC專用芯片,符合IEC61375-1國際標準。MVBC01專用芯片采用16位數據總線,提供了豐富的接口控制信號,簡化了與各種宿主CPU以及通信存儲器的接口設計,支持MVB協議中鏈路層及以下的功能。

2.4 通信存儲器模塊

通信存儲器地址空間保存MVBC01的所有數據和信息,既可以被MVBC01訪問又可以被ARM處理器訪問。本系統中采用兩片512 kB大小的SRAM cy62148擴展成1 MB的尋址空間。通信存儲器的尋址空間劃分為4部分,分別為Logical AddreSS Space(LA),Device AddressSpace(DA),Service Area(1 kB)和Miscellany。

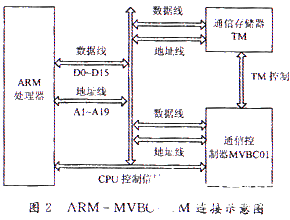

通信存儲器分別通過數據線,地址線和ARM處理器以及MVBC01相連,從而實現數據交換和地址尋址,ARM處理器、MVBC01和通信存儲器的連接示意圖如圖2所示。

MVBC01內部集成Traffic Memory Controller(TMC)模塊,負責控制通信存儲器的訪問模式,TMC與仲裁控制器和邏輯地址密切相關。TMC模塊負責控制3種存儲器訪問模式,分別是:ARM CPU訪問通信存儲器;ARM CPU訪問MVBC內部寄存器;MVBC01訪問通信存儲器。TMC模塊還對ARM處理器和MVBC同時訪問通信存儲器所產生的訪問沖突做出仲裁。

2.5 MVB物理層接口電路模塊

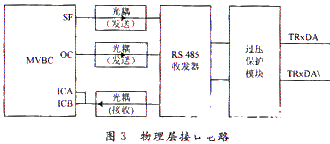

物理層接口電路模塊的設計如圖3所示。物理層接口采用電氣短距離介質ESD+接口,系統信號通道使用光耦實現主系統與外界得電隔離以提高系統可靠性,使用RS 485芯片作為收發器,并使用過壓保護模塊來防止瞬問過壓對器件的損壞。

圖3所示的MVBC端口ICA(MVB Input Data Chan-nel A)和ICB(MVB Input Data Channel B)分別為MVB輸入數據通道A和輸入數據通道B,來自物理層收發器的MVB信號由此端口送入MVB通信控制器MVBC01中;MVBC端口OC(MVB Output Data Channel)是MVB數據輸出端口,數據經由此端口將發送至物理層收發器;MVBC端口SF(Send Frame)為輸出端口,輸出信號可作為物理層的使能信號,該信號有效時表示一個報文正在通過MVBC端口OC(MVB Output Data Channel)輸出。

2.6 其他

在MVB設備正常運行時,可以通過RS 485/RS 232通信接口進行程序的監控和調試。系統可以通過跳線選擇RS 485/RS 232接口是工作在RS 485還是RS 232下。

其他還有諸如看門狗、JTAG接口、時鐘、電源、PC104接口等模塊,本文不再詳述。

3 系統軟件設計

3.1 系統軟件體系結構

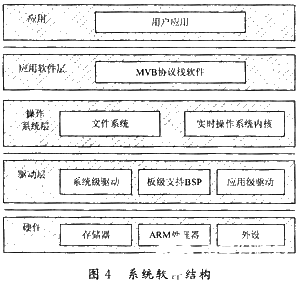

MVB 2類設備軟件體系采用典型的嵌入式軟件體系結構,包括驅動層、操作系統層、應用軟件層,其中操作系統層是軟件體系的核心。系統的軟件結構如圖4所示。

系統軟件結構各部分功能如下:

3.1.1 驅動層

驅動層是直接和硬件相聯系的一層,他對操作系統和應用提供所需的驅動支持。該層主要包括3種類型的程序:板級支持BSP、系統級驅動和應用級驅動。

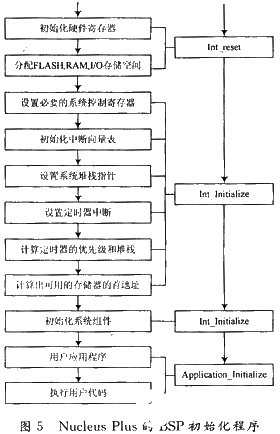

板級支持BSP 在用戶的應用程序啟動之前,完成對系統的初始化必須有專門的一段啟動代碼,即板級支持BSP。板級支持BSP介于物理硬件和實時操作系統之間,在系統上電后,初始化系統的硬件環境,包括初始化ARM處理器、初始化中斷控制器、初始化存儲器、初始化堆棧等。NucleusPlus操作系統的BSP初始化程序流程如圖5所示。

系統級驅動 與系統軟件相關的驅動,這類驅動是操作系統和中間件等系統軟件所需的驅動程序,他們的開發要按照系統軟件的要求進行。

應用級驅動 與應用程序相關的驅動,和操作系統無關,由應用決定。

3.1.2 操作系統層

操作系統層足嵌入式軟件的核心,是系統的軟件支持平臺。主要包括實時操作系統內核、文件系統、電源管理、嵌入式GUI系統、嵌入式網絡系統。其中嵌入式內核是基礎和必備的部分,主要完成任務調度、內存管理、任務間通信、任務的同步與互斥、中斷管理、定時器等功能。本系統采用Nucleus Plus嵌入式操作系統,能完全滿足MVB對于實時性、可靠性、完整性和有效性的要求。NucleusPlus采用了軟件組件的方法,每個組件具有單一而明確的目的,包括任務控制管理、內存控制管理、定時器管理、中斷、系統診斷、I/O驅動管理等16個組件。

3.1.3 應用軟件層

應用軟件層主要由多個相對獨立的應用任務組成,每個應用完成一個特定的工作,這里主要包括MVB協議棧軟件。MVB協議棧軟件在實時操作系統內核的支持下,通過MVB驅動模塊完成MVB網絡數據通信任務。用戶應用可以利用MVB協議棧的接口函數訪問需要的數據集,并利用收到或者發送的數據進行相應的控制或其他數據處理工作。

3.2 實時協議

每個網絡都要有與之相應的網絡軟件在其上運行,這些軟件被稱為協議。在互聯網上運行的協議我們稱之為TCP/IP協議,在列車通信網上運行的類似TCP/IP的協議我們稱之為實時協議(Real Time Protocol,RTP),實時協議為一個應用與另一個應用在列車通信網上的通信提供協議和服務。

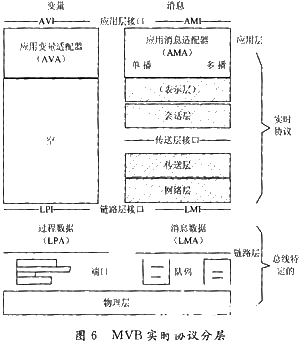

實時協議分層結構如圖6所示。由圖中的分層結構可知MVB實時協議包括過程變量通訊和消息數據通訊兩部分。由圖可知變量的協議和服務包括過程數據鏈路層接口(LPI)和變量的應用層接口(AVI)。消息協議和服務包括消息數據鏈路層接口(LMI)、網絡層、傳送層、會話層、應用層接口(AMI)。其中鏈路層接口又稱為低層接口,他規定來自總線的服務,應用層接口又稱為高層接口,他規定提供給應用的應用層接口。

3.3 消息通信機制及其實現

MVB 2類設備的主要特征是實現消息數據的發送和接收。消息通信中實時協議是由信使執行的,他是作為獨立的進程與應用并行運行。實時協議的網絡層、傳輸層、會話層、表示層是由信使來執行并實現的,信使與應用層有一個消息應用層接口(AMI),通過這個接口應用可以調用信使的服務。同時信使與鏈路層也有一個接口:消息鏈路層接口(LMI),鏈路層通過這個接口向信使提供服務。在編程實現消息通信時,只需要使用消息應用層接口。

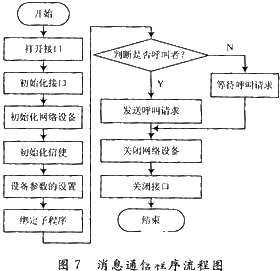

用戶開發程序來實現消息通信,就是使用消息應用層接口中的接口函數來調用信使的各項功能,實現消息通信的應用程序就是按照這個順序編寫和執行的。消息數據的實現程序的流程如圖7所示。

4 結 語

使用符合TCN標準的產品是開發下一代新式列車的重要發展趨勢,本文通過對IEC61375-1列車通訊網絡標準的研究,提出了MVB 2類設備軟硬件的設計方案并完成了系統硬件各功能模塊設計和上層軟件的部分設計,對MVB實時協議RTP和消息通信的機制也做了深入的研究,并給出了消息通信的編程實現方法。通過對基于ARM處理器的MVB 2類設備的深入研究和功能設計實現,不但為以后開發更高類別的MVB設備積累了經驗,而且為進一步自主開發其他符合TCN標準的MVB產品提供了借鑒。

責任編輯:gt

-

處理器

+關注

關注

68文章

19286瀏覽量

229852 -

控制器

+關注

關注

112文章

16361瀏覽量

178071 -

存儲器

+關注

關注

38文章

7492瀏覽量

163842

發布評論請先 登錄

相關推薦

處理器及微處理器系統

dsp芯片和通用微處理器有什么區別

什么是總線微處理器

ARM微處理器介紹

ARM微處理器的應用領域及其特點

采用NET+50和MVBC01芯片實現MVB 2類設備系統的設計

基于微處理器NET+50和MVBC01芯片實現MVB 2類設備系統的設計

基于微處理器NET+50和MVBC01芯片實現MVB 2類設備系統的設計

評論