隨著半導體工藝的迅速發展,嵌入式處理器和DSP的設計越來越復雜,其開發調試工作也日趨重要,因此處理器平臺提供強大的調試系統已成為設計中必不可少的一部分。

嵌入式處理器調試系統使用硬件仿真器將調試軟件與目標芯片接連起來。仿真器與PC機之間通過標準的計算機通信接口(以太網、USB、串口等)進行通信;仿真器與目標芯片之間通過符合IEEEll49.1標準的JTAG(Joint Test Action Group)信號進行數據傳輸。隨著處理器和仿真器主頻的不斷提升,傳統的JTAG接口設計以其缺乏對JTAG信號傳輸進行必要的時序匹配,而無法確保仿真器和目標芯片對JTAG信號進行穩定可靠的接收,因此不能滿足高性能嵌入式系統的要求。

在此,提出一種雙向同步自適應時鐘技術,在仿真器與目標處理器之間穩定可靠地實現了跨時鐘域JTAG信號的雙向時序匹配,并在此基礎上設計了一種TCK時鐘信號產生算法,從而解決了調試系統軟/硬件協同驗證中JTAG信號交互時的時序匹配問題。

1 自適應時鐘技術

1.1 基本概念

自適應時鐘(Adaptive Clocking)是一種信號同步技術,其基本原理來源于異步電路設計中的自動調時(SelfTimed)技術,即采用類似應答機制來實現兩個不同時鐘域系統間信號的可靠傳輸,如圖l所示。

圖l中的發送與接收系統均工作在各自獨立的時鐘域下,并對異步輸入信號進行采樣同步。發送系統(Transmit System)以時鐘clk_t為基準,向接收系統(Receive System)發送數據data_t。接收系統將信號clk_t采樣同步后產生clk_r,并作為應答信號反饋給發送系統,發送系統接收到clk_r信號,就認為接收系統已經完成了數據接收或處理,可以繼續發送新的時鐘和數據。此外,如果接收系統也需要向發送系統傳送數據data_r,則以clk_r為基準,便于發送系統采用同樣的機制接收。

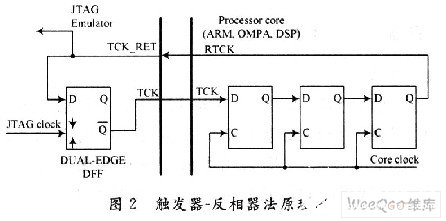

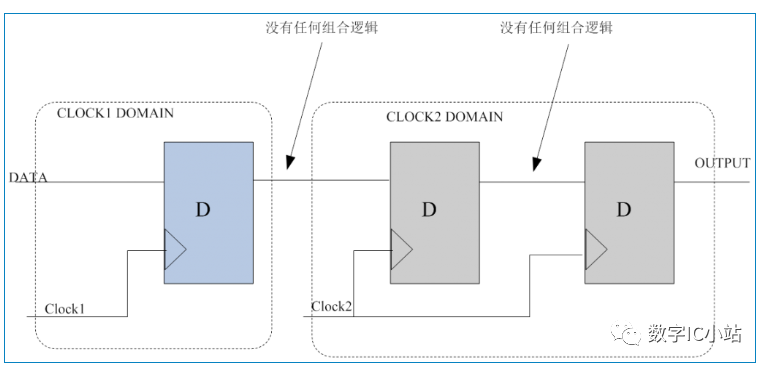

自適應時鐘機制通常采用多級同步器實現,一般由幾個D觸發器構成,如圖2所示。同步器將時鐘信號TCK同步到內核時鐘域。同步器的級數Ns通常與具體的器件相關,一般取值為3或者4。TCK_RET來自最后一級D觸發器的輸出,作為TCK的“應答”信號,反饋給調試系統。

TCK信號頻率的理論最大值可以根據內核時鐘頻率和Ns的值,由下式簡單計算得到:

![]()

自適應時鐘協議是一種通過目標系統來控制TCK速率的機制,這種機制的優點在于它能夠把所有的信號傳輸延遲(包括JTAG電纜引入的延時)都考慮在內,從而避免了由于傳輸延遲帶來的接收數據損壞,有效提高系統性能。

自適應時鐘的另一個優點是可以使仿真器工作在最優的TCK時鐘頻率下。如果仿真器支持可變的TCK頻率,但沒有使用自適應時鐘技術,用戶就必須通過實驗來設置TCK的最高工作頻率和穩定工作頻率。

自適應時鐘的第三個優點是如果芯片內核時鐘也是可變的,那么TCK_RET信號也會在工作時隨之變化,從而保證傳輸數據能夠隨時被仿真器正確同步并采樣。

1.2 研究背景

目前自適應時鐘技術主要用于嵌入式處理器芯片的在線仿真器(In-Circuit Emulator,ICE),簡稱仿真器。仿真器可以為開發人員提供嵌入式處理器的實時調試和性能微調功能,該系統通過符合IEEE1149.1標準的JTAG接口與芯片內部邏輯進行數據交換。

ARM公司最先在其嵌入式處理器的仿真器EmbeddedICE-RT中采用了自適應時鐘技術。最近,TI公司也在其0MAP系列嵌入式處理器的仿真器Blackhawk JTAG Emulator中采用了自適應時鐘技術。它們的自適應時鐘都基于觸發器-反相器法,如圖2所示。在采樣TCK_RET信號時,使用一個雙邊沿D觸發器(D-type Flip-Flop,DFF),這樣可以避免最終產生的TCK時頻率被降低一半。

觸發器-反向器法自適應時鐘技術僅對TCK信號進行同步,并沒有對TCK_RET信號同步,因此TCK信號容易產生不定態輸出,從而導致整個系統失效。此外,TCK信號的產生模式沒法由仿真器控制,因而靈活性差,適用范圍窄,并且在沒有JTAG信號傳輸時TCK信號無法關斷,這不僅增加了系統功耗,而且也增加了板級JTAG信號間的干擾。

筆者參與了國內一款高性能DSP芯片的研發工作,同時還負責該芯片的調試系統設計,基于自適應時鐘的基本原理,提出了雙向同步自適應時鐘技術。該時鐘技術具有如下優點:

(1)對TCK和TCK_RET分別進行同步,確保JTAG信號雙向通信的可靠性和穩定性;

(2)TCK信號由硬件算法產生,可以根據應用需要靈活調整信號特征,從而解決了芯片設計中軟/硬件協同驗證的時序匹配問題;

(3)在沒有JTAG通信的間隙能夠主動關閉TCK信號,降低系統功耗,減小板級的信號干擾;

(4)由于仿真器時鐘域和處理器時鐘域之間的異步關系,產生TCK時鐘信號時會引入抖動(Jitter)。該抖動對系統是有益的,它會對TCK信號引入擴頻調節,從而降低電磁干擾(Electro Magnetic Interference,EMl),提高系統的電磁兼容性(Electro Magnetic Compatibmty,EMC)。

2 雙向同步自適應時鐘技術

隨著嵌入式處理器性能的增強,仿真器需要處理的在線調試功能也隨之增強,因此仿真器本身也需要工作在比較高的時鐘頻率下,從而能夠在有限的時間內處理足夠多的調試信息。通常使用JTAG時鐘信號TCK的頻率相對比較低,在1~20 MHz之間,已經遠遠無法滿足仿真器的工作需要。雙向同步自適應時鐘機制能夠保證仿真器和處理器都工作在各自的高頻時鐘下,同時還能夠實現可靠的JTAG信號傳輸。

2.1 原理

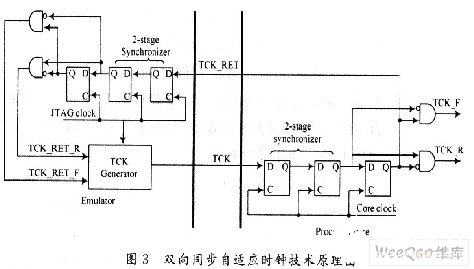

雙向自適應時鐘技術的原理如圖3所示。

仿真器工作在JTAG clock時鐘域,其頻率為fJTAG;所有由仿真器發送給處理器內核的JTAG信號都由該時鐘域的邏輯產生,并與TCK對齊,TCK的頻率為fTCK。處理器內核工作在Core clock時鐘域,其頻率為fCore;JTAG clock,TCK和Core clock這三組時鐘信號之間通常滿足下述基本關系:

由于TCK和TCK_RET信號在兩個異步時鐘域之間傳輸,為了消除跨時鐘域信號傳輸可能帶來的不定態導致系統失效,處理器內核和仿真器都需要分別對這兩個信號進行同步和采樣,即雙向同步。同步器采用2級D觸發器級聯構成,這種結構可以保證系統在108s(大約3年)內失效的次數少于1次,從而解決絕大部分跨時鐘域信號的不定態問題。如果在特殊情況下需要進一步提高系統的穩定性,可以繼續增加D觸發器的級聯數目,但是這樣做會增加系統的延遲,因此需要在性能和穩定性之間進行權衡。

TCK信號經過Core clock時鐘同步之后產生TCK_RET信號,反饋給仿真器,從而實現自適應時鐘技術。同時,由處理器內核向仿真器發送的JTAG信號(例如TDO)與TCK_RET信號對齊。TCK_R和TCK_F可作為Core clock時鐘域的門控信號,分別在TCK的上升沿或者下降沿使能處理器內核對JTAG信號進行采樣或處理。

TCK_RET信號被JTAG clock時鐘同步。TCK_RET_R表示采樣到TCK_RET的上升沿,TCK_RET_F表示采樣到TCK_RET的下降沿。這兩個信號送給TCK時鐘產生邏輯,用來根據當前TCKRET信號的接收情況產生下一個TCK信號及相關的JTAG控制和數據信號。

2.2 性能分析

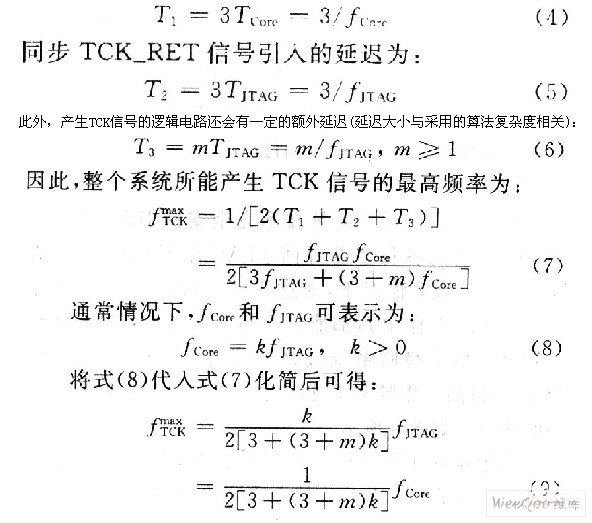

雙向同步技術引入了兩個同步器,分別用來確保TCK和TCK_RET信號能夠被異步時鐘正確采樣,因此各自增加了一定的系統延遲。同步TCK信號引入的延遲為:

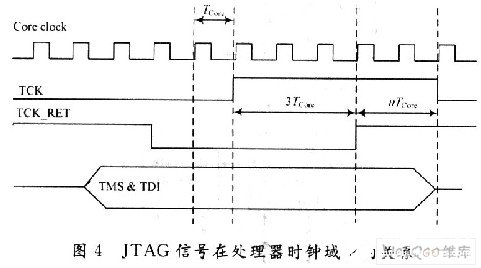

要保證圖3中Core clock時鐘域邏輯電路能夠在TCK_RET信號上升沿采樣到穩定的數據,JTAG信號必須滿足圖4中的關系。

在DSP設計中,fCore=500 MHz,fJTAG=100 MHz,并假設m=1,代入式(9)計算可得TCK信號的最高頻率大約為10.9 MHz。

2.3 多芯片級聯結構

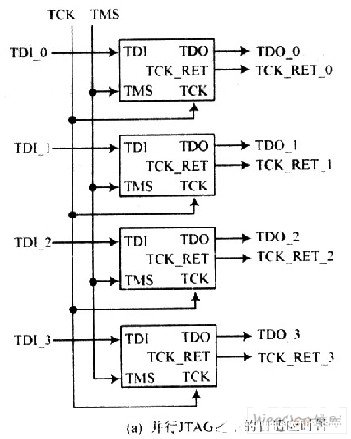

雙向同步自適應時鐘技術完全支持IEEEll49.1協議中定義的各種多芯片間JTAG信號板級互聯結構。多芯片級聯情況下,通過式(9)或式(13),根據每一塊芯片的工作主頻都能計算得到一個對應的TCK頻率值。整個級聯系統最終使用的JTAG時鐘信號TCK的最高工作頻率不能超過所有TCK頻率值中最小的那個。如圖5所示。

采用并行互聯結構的JTAG鏈路,多芯片自適應時鐘連接方式與單芯片連接方式一致,每塊芯片都提供一路被自身時鐘域所同步的自適應時鐘TCK_RET,如圖5(a)所示。

對于采用串行菊花鏈結構的JTAG鏈路,自適應時鐘TCK_RET僅來自于鏈路上最接近TDO輸出端一側的那塊芯片,其他芯片不提供自適應時鐘,如圖5(b)所示。

對于串/并混合連接的多芯片JTAG鏈路,自適應時鐘的連接是上述兩種連接方式的混合,如圖5(c)所示。

多芯片系統的JTAG連接方式一般都采用串行菊花鏈結構,從而確保其JTAG鏈路與仿真器接口與單芯片情況下一致,并能夠簡化系統設計。

3 自適應時鐘技術在芯片驗證中的應用

隨著嵌入式處理器設計的規模越來越大,復雜度越來越高,功能驗證已經成為設計過程中的首要瓶頸。為了提高驗證速度,通常采用專門的硬件加速器,筆者參與的高性能DSP設計項目采用了Cadence公司XtremeⅢ硬件加速器,以加速設計功能的驗證。XtremeⅢ是基于FPGA的硬件模擬器,它是專門為運行模擬(Simulation)而特別設計的計算機。硬件模擬器只能驗證邏輯功能,而不能驗證時序性質,因為來自FPGA網絡或者處理器的時延與系統設計過程中的時延無關。使用硬件模擬器時,主要瓶頸是硬件模擬器與主機之間的交互(又稱系統調用)。因此,在軟/硬件協同驗證中。真實的硬件系統在與基于硬件模擬器的系統發生信號交互時,時序匹配成為最大的難題。

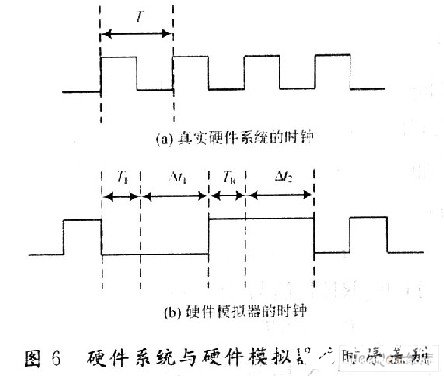

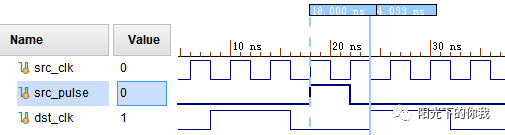

圖6說明了硬件模擬器的時鐘與真實硬件系統時鐘間的差別。真實硬件系統產生的是絕對時鐘信號,它的周期是一個固定值T,如圖6(a)所示。硬件模擬器與軟件模擬器類似,只有相對時鐘概念。它在被模擬系統的時鐘上升沿和下降沿處分別計算系統中所有的事件,如圖6(b)所示。對于特定的設計,無系統調用時,虛擬時鐘信號周期Ts=TR+TF基本上是常值,其中,TR為上升沿計算所有事件所需的時間;TF為下降沿計算所有事件所需的時間會產生;當發生系統調用時(比如仿真時的系統函數調用等),額外的延時△t(△t=△t1+△t2),使得當前周期增大為Ts+△t。因此硬件模擬器中的時鐘信號周期是無規律變化的,而且受系統調用頻度以及系統調用復雜度(即△t的大小)的影響。

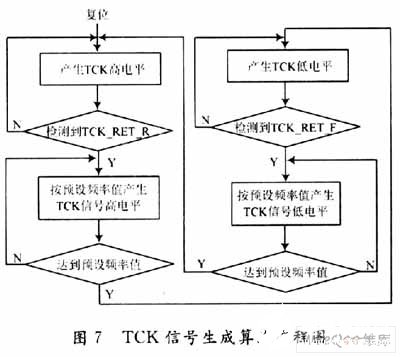

嵌入式處理器的調試系統需要采用系統級的軟/硬件協同驗證,包括軟件開發和調試環境、仿真器系統、處理器系統三部分。在該DSP設計項目中,軟件環境(運行在PC機上)和仿真器系統(基于FPGA開發板)都采用真實系統,而DSP則在XtremeⅢ模擬器中實現。仿真器與DSP之間通過JTAG信號進行通信。仿真器采用圖3所示的雙向同步自適應時鐘技術,仿真器發送給DSP的TCK信號特征與圖6(a)相同,而DSP反饋給仿真器的同步時鐘TCK_RET信號特征與圖6(b)相同。因此,在TCK Generator中設計圖7所示的算法,從而完全解決了真實硬件系統與硬件模擬器之間的JTAG信號傳輸時序匹配問題。實驗中,設定TCK的工作頻率為40 kHz。未采用雙向自適應同步時鐘技術時,仿真器與xtremeⅢ硬件模擬器之間的JTAG信號傳輸經常發生TCK_RET時鐘沿丟失(等效時鐘頻率約為20 kHz),導致仿真器無法正確采樣TDO數據,如圖8(a)所示。采用雙向自適應時鐘后,盡管整個驗證系統中TCK時鐘信號的實際工作頻率約為20 kHz,但持續不間斷工作72 h以上未發現JTAG信號傳輸錯誤,從而證明系統能夠正常工作,如圖8(b)所示。

4 結語

為解決高性能嵌入式處理器或DSP與仿真器之間JTAG信號傳輸穩定性問題,提出了一種雙向同步自適應時鐘技術。該技術在同步電路中引入了異步電路的應答機制,巧妙解決了由于嵌入式處理器或DSP(尤其是針對低功耗設計的處理器,它的工作主頻會隨著負載變化而變化)本身主頻變化導致的JTAG信號傳輸失效。此外,該技術還為軟、硬件協同驗證中真實系統與硬件模擬器之間信號傳輸提供了可靠的解決方案。在隨后的工作中,將繼續研究自適應時鐘技術在各種系統跨時鐘域信號傳輸中的應用。從而進一步拓展該技術的適用范圍。

責任編輯:gt

-

處理器

+關注

關注

68文章

19382瀏覽量

230481 -

半導體

+關注

關注

334文章

27571瀏覽量

220479 -

嵌入式

+關注

關注

5087文章

19153瀏覽量

306426

發布評論請先 登錄

相關推薦

基于雙向同步自適應時鐘技術實現跨時鐘域信號傳輸系統的設計

基于雙向同步自適應時鐘技術實現跨時鐘域信號傳輸系統的設計

評論