許多通信、儀器儀表和信號采集系統需要同時通過多個模數轉換器(ADC)對模擬輸入信號進行采樣。由于這些輸入信號各自有不同的延遲,所以必須對輸入的采樣數據做同步處理。為滿足低電壓數字信號(LVDS)和并行輸出ADC的需要,延遲不一致的問題對系統設計人員而言歷來是一個難題。

JESD204B提供了一個方法通過一個或多個差分信號發送高速串行數據,比如發送ADC的輸出。JESD204B規范本身具有實現通道間粗調對齊的功能。數據分割為幀,并持續發送至接收器。通過使用系統參考事件信號(SYSREF),JESD204B Subclass 1接口支持多個串行通道鏈路或多個ADC的數據對齊至SYSREF,以便同步發射器和接收器的內部幀時鐘。

這使得采用JESD204B鏈路的設備具有確定延遲。但是,為了讓采樣同步達到徹底的時序收斂,仍然有許多挑戰等待系統設計人員去解決,如PCB布局考慮、時鐘匹配和產生SYSREF以滿足時序、SYSREF的周期性以及數字FIFO延遲的要求。

設計師必須決定設備時鐘和SYSREF信號如何生成、以及如何在系統中分配。理想狀態下,設備時鐘和SYSREF應具有相同的擺幅和電平偏移以防止在器件引腳端引入固有的時延。SYSREF既可作為系統啟動時候所需的單次觸發,也可作為任意時刻需要同步時即可發生的重復信號。需要將時鐘和SYSREF信號的最大偏斜納入考慮范圍,并仔細布局PCB,以滿足整個電路板、連接器、背板和多種元件對于建立和保持時間的要求。最后,應將JESD204B發射器和接收器內部的數字FIFO以及信號跨時鐘域傳輸所造成的固有時延計算在內并在后臺數據處理中消除。

系統時鐘可由晶振、VCO和時鐘發生或時鐘分配芯片產生。雖然特定的系統性能將決定對時鐘的需求,但必須使用多個同步ADC來產生與輸入時鐘源同步的SYSREF信號。這使得時鐘源的 選擇成為重要的考慮因素,因為要能夠通過已知時鐘邊沿在特定的時間點上鎖存這一系統參考事件。若SYSREF信號和時鐘未鎖相,則無法達到這樣的效果。

可使用FPGA為系統提供SYSREF事件。然而,除非FPGA也同步至發送到ADC的主時鐘,否則FPGA發出的SYSREF信號很難跟主時鐘對齊相位。另一種方法是由時鐘發生或時鐘分配芯片提供 SYSREF信號,可通過發送至整個系統的信號相位同步至多個時鐘。采用此種方法,則SYSREF時間根據系統需要,既可以是啟動時的一次性事件,也可以是重復信號。

只要確定性延遲在整個系統的ADC和FPGA內保持恒定,則可能并不需要額外的SYSREF脈沖,除非為了幫助產生特定的系統數據。因此,用于時鐘對齊的周期性SYSREF脈沖可忽略或過濾掉,直到同步丟失。可只標識SYSREF發生過,但不重置JESD204B鏈路。

為了初始化ADC通道確定的起始點,系統工程師必須要能滿足所有分布在系統中的SYSREF的時序要求。這意味著必須滿足和時鐘相關的建立和保持時間。只要能夠滿足到達第一個所需 時鐘的建立時間要求,使用跨越多個時鐘周期、相對較長的SYSREF脈沖可用于滿足保持時間的需要。必須格外注意PCB的布局,保證系統中時鐘和SYSREF布線長度匹配,以便使偏斜盡可能小。這可能是獲得通道間同步采樣處理結果的最困難的部分。隨著ADC編碼時鐘速率的增加以及多電路板系統越發復雜,這一過程還將變得更困難。

系統工程師必須確定知道每個器件上的在電路板元件之間以及連接器上的SYSREF至時鐘的偏斜。任何殘余的器件間數字和時鐘偏斜延遲都必須在FPGA或ASIC內有效歸零。后臺處理可能改變ADC的采樣順序并進行任何必要的重對齊,以便為數據的進一步同步處理作準備。在后臺FPGA或ASIC中,可通過延遲最快的數據采樣和發射器延遲,使其與最慢的數據采樣對齊,以完成器件間采樣偏斜的校正。

對于復雜的系統,這可能需要用到多個FPGA或ASIC,每個器件都需要了解其器件間總采樣延遲,以便用于最終的對齊。通過在JESD204B接收器中采用合適的緩沖器延遲來應對每個特定的發射器延遲,器件間的采樣偏斜便可在整個系統中與已知確定值對齊。

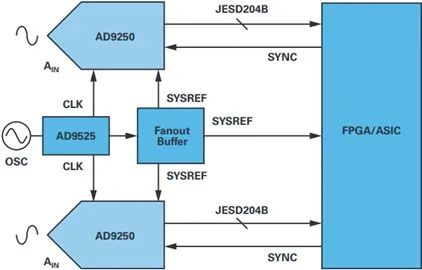

AD9250是ADI的一款250 MSPS、14位、雙通道ADC,可在subclass1的實施中支持JESD204B接口。該子類支持采用SYSREF事件信號的ADC采樣同步。AD9525是一款低抖動時鐘發生器,不僅提供7個高達3.1 GHz的時鐘輸出,還可根據用戶配置同步SYSREF輸出信號。這兩款產品與ADI的可選扇出緩沖器產品組合使用,可精確同步與對齊多個發送至FPGA或ASIC處理的ADC數據。

圖1. AD9250、AD9525和FPGA示意圖。

編輯:jq

-

pcb

+關注

關注

4319文章

23099瀏覽量

397923 -

adc

+關注

關注

98文章

6498瀏覽量

544662 -

lvds

+關注

關注

2文章

1043瀏覽量

65817

原文標題:【世說設計】如何使用JESD204B同步多個ADC?這里有個方法~

文章出處:【微信號:Excelpoint_CN,微信公眾號:Excelpoint_CN】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Altera JESD204B IP核和TI DAC37J84硬件檢查報告

TI ADS42JB69系列JESD204B ADC與Altera FPGA的互操作性

adc32j22、dac37j82的jesd204b是不是只能通過測試RBD=1~K來確定最優的RBD值?

調試ADS52J90板卡JESD204B接口遇到的問題求解

ADS54J60與JESD204B建立鏈路成功,但有效數據全為0,為什么?

使用JESD204B接口,線速率怎么計算?

ADC16DX370 JESD204B串行鏈路的均衡優化

從JESD204B升級到JESD204C時的系統設計注意事項

采用JESD204B的LMK5C33216超低抖動時鐘同步器數據表

抓住JESD204B接口功能的關鍵問題

悄悄告訴你們如何使用JESD204B同步多個ADC!

悄悄告訴你們如何使用JESD204B同步多個ADC!

評論