探索異構平臺的設計方法和概念

賽靈思 Versal ACAP 硬件、IP 和平臺開發方法論是旨在幫助精簡 Versal 器件設計進程的一整套最佳實踐。Versal ACAP從設計之初即采用正確方法并盡早關注設計目標(包括 IP 選擇和配置、塊連接、RTL、時鐘、I/O 接口和 PCB 管腳分配)至關重要。在每個設計階段中正確定義和驗證設計有助于減少后續實現階段的時序收斂、性能收斂和功耗問題。

鑒于設計的規模與復雜性,因此必須通過執行特定步驟與設計任務才能確保設計每個階段都能成功完成。本指南基于最佳時間對操作步驟進行了規范,幫助開發者以盡可能最快且最高效的方式實現期望的設計目標。

Versal ACAP支持包括Vivado IP intergrator、Vitis HLS、RTL等方式創建設計。

Vivado IP integrator 支持使用 SmartConnect IP 和 NoC 將多個 IP 連接在一起以創建塊設計 (.bd) 或 IP 子系統。通過使用 IP integrator,即可將 IP 拖放到設計畫布上,以單一線路連接 AXI 接口,設置端口和接口端口布局以將 IP 子 系統連接到頂層設計。這些 IP 塊設計還可作為源設計加以封裝 并在其它設計中復用。

本指南中詳細介紹了開發者通過以上方式創建設計的基本流程和注意事項。

如何完美適配 Vitis 環境?

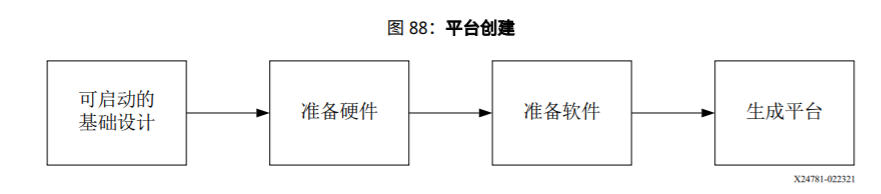

平臺是設計的起點,Vitis 統一軟件平臺憑借“打破軟硬件語言壁壘,提升開發效率”的優勢,廣受開發者青睞。本指南對如何適配 Vitis 環境提供了詳細的指導。

獲取基礎平臺源代碼

同時,如果開發者希望從頭開始創建自定義 Vitis 嵌入式平臺,本指南亦提供了詳細的指導。

編輯:lyn

-

pcb

+關注

關注

4324文章

23148瀏覽量

399050 -

IP

+關注

關注

5文章

1715瀏覽量

149770 -

RTL

+關注

關注

1文章

385瀏覽量

59894

原文標題:用戶指南 | 探索 Versal ACAP 設計方法論

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

異構計算的概念、核心、優勢、挑戰及考慮因素

人工智能應用中的異構集成技術

【一文看懂】什么是異構計算?

異構集成封裝類型詳解

新華三發布多元異構算力平臺H3C UniServer G7

汽車異構硬件平臺開發如何進行靜態代碼分析

淺談國產異構雙核RISC-V+FPGA處理器AG32VF407的優勢和應用場景

AvaotaA1全志T527開發板AMP異構計算簡介

無問芯穹發布千卡規模異構芯片混訓平臺

遷移學習的基本概念和實現方法

鯤泰新聞|神州鯤泰創新智算之旅北京站開幕,發布全新智算架構和液冷整機柜產品應對 “多云、異構、綠色

【大語言模型:原理與工程實踐】探索《大語言模型原理與工程實踐》2.0

多核異構通信框架(RPMsg-Lite)

探索異構平臺的設計方法和概念

探索異構平臺的設計方法和概念

評論