數字信號處理就是用一些數學算法對數字信號進行分析、變換、綜合、估值和識別。作為數字信號處理核心和標志的數字信號處理器(DSP)芯片自問世以來得到了快速的發展,廣泛應用于通信系統、圖形/圖像處理、雷達聲納、醫學信號處理等實時信號處理領域。隨著人們對實時信號處理要求的不斷提高和大規模集成電路技術的迅速發展,數字信號處理器也發生著日新月異的變革。美國AD公司,繼16 b定點ADSP21xx和32 b浮點ADSP21xxx系列之后推出的ADSP Tiger SHARC系列處理器,是基于AD2106x的下一代高性能芯片。本文著重介紹Tig er SHARC系列中TS101S芯片的性能及結構特點,并將其應用在雷達信號處理系統設計中。

1 Tiger SHARC DSP

Tiger SHARC DSP是一款高性能的靜態超標量數字信號處理器,該處理器專為大的信號處理和通信任務而在結構上進行了優化。由于該處理器將非常寬的存儲帶寬和雙運算模塊結合在一起,從而建立了數字信號處理器性能的新標準。Tiger SHARC 靜態超標量結構使DSP 每周期能夠執行多達4 條指令、24 個16 b定點運算和6個浮點運算。該Tiger SHARC DSP 器件在3條相互獨立的128 b寬度的內部數據總線中,每條可連接3個2 Mb 內部存儲器 中的1個,并可提供4個字的數據、指令及I/O訪問和12 GB/s的內部存儲器帶寬。運行在250 MHz時,ADSPTS101S 的內核指令周期為4 ns,同時可以提供20億次 的40 b MAC運算或者500萬次80 b MAC運算。

Tiger SHARC DSP器件的主要性能如下:

(1)最高運行速度為300 MHz,指令周期為3.3 ns。

(2)帶有6 Mb片內SRAM,分為了3個2 Mb的存儲塊M0,M1和M2,每一個存儲塊都能夠 單獨存儲程序、數據或同時存儲程序和數據。

(3)帶有雙運算模塊,每個運算塊有1個64 b ALU,1個乘法器,1個64 b移位器和1個 由32個寄存器構成的寄存器組,可執行定點和浮點的算術邏輯等通用運算。

(4)3條內部地址/數據總線,每條總線都連接到3個內部存儲器塊中的1個。3條總線都 是128 b寬,可以在任一周期使用任一條總線傳送多達4條指令或4個對齊的數據。這樣TS10 1S內核可以在任一周期并行訪問3個存儲塊,1個取指令,2個訪問數據。

(5)4個鏈路口支持點對點的高帶寬數據傳送,可通過單個鏈接口以250 Mb/s 的速率進行 數據傳輸。4個鏈路口為處理器與處理器之間的通訊提供了一個良好的途徑,總吞吐量多達 1 Gb/s。

(6)多處理器特性,當單個DSP芯片組成的系統不能滿足處理要求時,TS101S通過外部口或鏈路口與其他TS101S相連構成多處理器系統。TS101S的外部總線支持多達8個DSP外加Host處理器的并行總線連接。在構成多處理器系統時,處理器之間無論是采用共享總線方式,還是采用鏈路口互連方式,都不需任何外加控制,實現無縫連接,在并行總線上可以80 0 Mb/s的速率進行數據傳輸。

(7)有DMA和SDRAM控制器,擁有14個DMA通道,提供了在處理器核不干預條件下的零 開銷數據傳輸,SDRAM的地址、數據引腳可以與Tiger SHARC的直接相連,另外,Tiger SHAR C提供專用的尋址空間支持SDRAM。

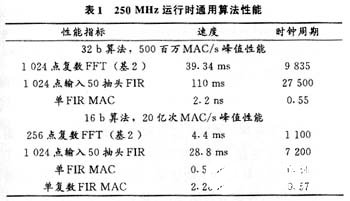

TS101S的主要性能指標如表1所示。

2 信號處理系統的實現

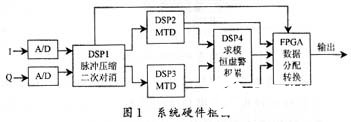

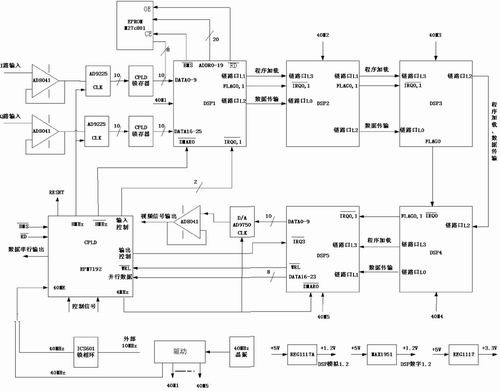

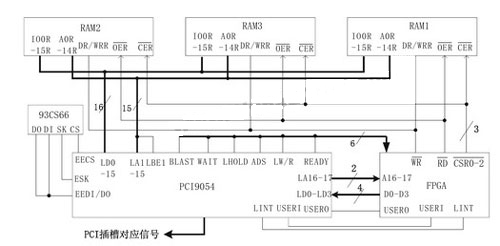

圖1所示是一個雷達信號處理系統的硬件框圖。為了簡化系統硬件,減少DSP片間連線,該系統的4個DSP以松耦合的鏈路方式進行連接,并共用一片FPGA。

首先由DSP1通過外部DMA方式讀入中頻解調后的I、Q路數據,并由DSP1對讀入數據進行脈沖壓縮(匹配濾波),脈沖壓縮后進行二次對消,以消除固定雜波。設計總距離單元數為2000,需做2 048點復數FFT,當2 048點復數FFT完成后,還必須和預先存儲好的匹配濾波器 系數H(k)相乘,一般需要做2 048個復數乘法,相乘結果還需做2 048點復數IFFT以獲得 脈沖壓縮結果。Tiger SHARC DSP做2 048點復數FFT和IFFT大約需要200 μs(工作在250 MHz ),利用Tiger SHARC DSP的雙運算塊和單指令多數據(SIMD)特點同時進行兩個距離單元的復 數乘法,完成2 048個復數乘法僅需25 μs。二次對消對于每個距離單元都需要做2次減法和1次加法,2 000個距離單元的二次對消大約需要50 μs。DSP完成上述運算大約要300 μs。

DSP2和DSP3完成動目標檢測功能。在使用窄帶多譜勒濾波器組時,為了降低旁瓣可在系統 中采用滑窗加權FFT的方法,在距離單元數為2 000時大約需要640 μs處理時間,用2片DSP 并行處理即可實現。

求模采用近似算法,每個距離單元只用做1次比較和1次加法。恒虛警處理先進行選大單 元平均運算,再對被檢單元進行比較判決,從而降低

虛警率。積累采用簡單累加求平均的方 式完成。以上3種運算由DSP4實現。

FPGA在電路中起輔助作用,在數據量較大的情況下進行數據寄存和分配,同時也能擔負DS P4的工作,如果需要的話還能進行數據的并/串轉換工作。

3 Tiger SHARC DSP的使用

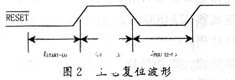

為保證Tiger SHARC DSP能正常工作,上電復位信號的設計非常重要。上電復位波形要求 如圖2所示,但應注意tSTARTLO在供電穩定之后必須至少大于1 ms,tPULSE1HI必須大于50個系統時鐘周期,同時小于100個系統時鐘周期,tPULSE2LO必須大于100個系統時鐘周期,在DSP上電后,如需正常復位,其低電平持續時間必須大于100個系統時鐘周期。

Tiger SHARC DSP有3個電源,其中數字3.3 V為I/O供電,數字1.2 V為DSP內核供電,模擬1.2 V為內部鎖相環和倍頻電路供電。Tiger SHARC DSP要求數字3.3 V和1.2 V應同時上電。若無法嚴格同步,則應保證內核電源1.2 V先上電,I/O電源3.3 V后上電。本系統在數字3.3 V輸入端并聯了一個大電容,而在數字1.2 V輸入端并聯了一個小電容,其目的就是為了保證3.3 V充電時間大于1.2 V充電時間,以便很好地解決電源供電的先后問題。

Tiger SHARC DSP內核最大電流為1.277 A,該電流是DSP進行單指令多數據(SIMD) 方式下,4個16 b定點字乘加與2個4字讀取并行操作以及進行由外部口到內部存儲器DMA操作所需的電流。實際上,DSP 內核電流大小還和內核工作頻率有關,因此,供給DSP 內核電流可根據不同的并行處理任務和內核工作頻率來確定,最大內核功耗為1.534 W。外部口的功耗(對VDDIO)主要是輸出引腳(例如數據線的某個位由高到低,或由低到高)轉換的功 率消耗,而且該功耗與系統無關,一般為0.45 W。由此可估算出該信號處理系統的功耗大 約為10 W。

4 結語

本文介紹了多片Tiger SHARC DSP在雷達信號處理系統中的應用,該系統充分利用了TS101 S高速的運算能力及數據吞吐量,對不同的距離單元段進行并行處理。文中分析了系統的運 算量、所需時間以及完成算法所需的DSP數,并且討論了DSP應用過程中需注意的幾個問題, 具有很強的實用性。該系統外接計算機總線,預留鏈路口,按信號處理通用板的模式設計, 也就是說,當單板資源不夠時,通過增加板子的數量就可成倍地增加信號處理能力,這對于 各種新型號雷達的開發研制起到了事半功倍的作用,大大縮短了研發周期,具有廣泛的 應用價值。

責任編輯:gt

-

處理器

+關注

關注

68文章

19286瀏覽量

229842 -

dsp

+關注

關注

553文章

7998瀏覽量

348927 -

雷達

+關注

關注

50文章

2936瀏覽量

117532

發布評論請先 登錄

相關推薦

哪位有ADSP TS101S 芯片的Cadence原理圖封裝啊 跪求 ..

一種基于TS101的SAR回波信號模擬器設計

如何采用ADSP-TS101實現高速信號處理系統的設計?

ICS554在軟件高頻雷達上的接口實現

基于DSP和DSP/BIOS的實時雷達信號采集與處理系統

基于ADSP-TS101S的多芯片數字信號處理系統的實現方案

采用ADSP-TS201S芯片的圖像采集處理系統設計

多片TS101S的加載引導設計分析及實現

基于TS101的圖像采集和處理系統設計

采用FPGA與高性能DSP芯片的雷達信號處理系統設計

基于TS101S芯片實現雷達信號處理系統的應用設計

基于TS101S芯片實現雷達信號處理系統的應用設計

評論