引言:本文我們介紹GTX/GTH收發器時鐘架構應用,該文內容對進行PCIe和XAUI開發的FPGA邏輯設計人員具有實際參考價值,具體介紹:

PCIe參考時鐘設計

XAUI參考時鐘設計

1.PCIe參考時鐘設計

1.1參考輸入時鐘

GTX/GTH收發器使用參考時鐘產生內部比特時鐘用于發送和接收數據。收發器使用PCIe模式時,推薦的參考時鐘為100MHz,參考時鐘也可以選擇125MHz或者250MHz。

參考輸入時鐘經過IBUFDS_GTE2原句驅動GTX/GTH收發器參考時鐘。如果TX buffer旁路,TXOUTCLKSEL必須選擇GTX/GTH收發器的參考時鐘作為TXOUTCLK源時鐘。該參考時鐘在電源上電后必須保持穩定和自由運行。

對于異步時鐘應用,最差的頻率偏移必須保持在±600ppm或者±300ppm。GTX/GTH收發器內部產生的25MHz時鐘來自參考時鐘分頻,用于同步器和定時器以及各種GTX/GTH收發器操作,如復位、電源管理、速率改變、OOB等。

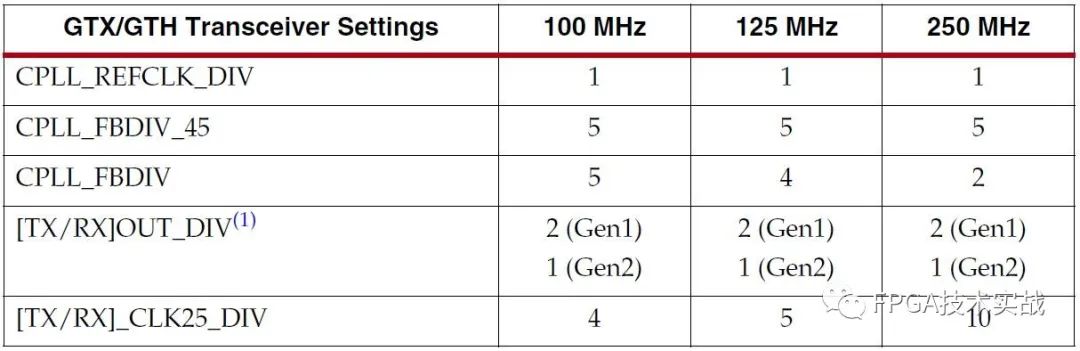

PCIe參考時鐘推薦的CPLL分頻器和時鐘設置如圖1所示。

圖1、PCIe參考時鐘推薦的CPLL分頻器和時鐘設置

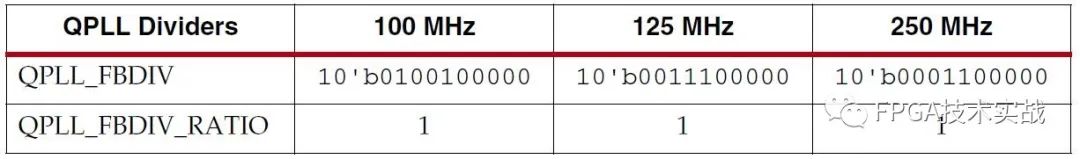

對于PCIe Gen3應用,QPLL必須使用,圖2顯示了推薦的QPLL配置。

圖2、推薦的QPLL設置

1.2 并行時鐘(PCLK)

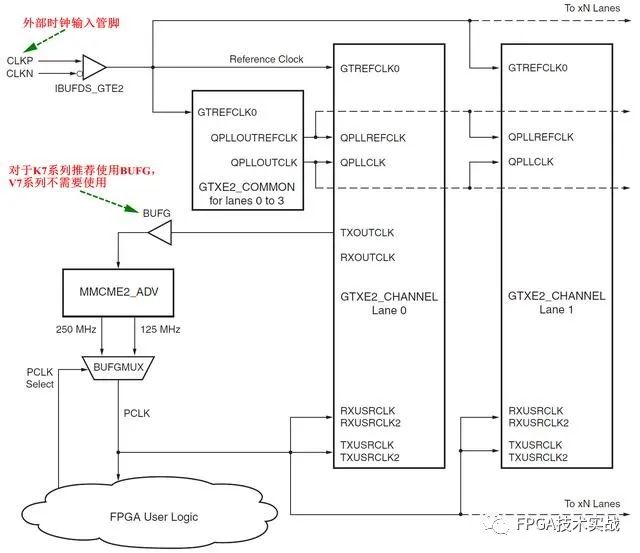

在PCIe模式中,PCLK是FPGA邏輯接口,用來同步并行接口數據傳輸。在Gen1應用中推薦的PCLK時鐘為125MHz,在Gen2和Gen3中推薦的PCLK為250MHz。通常一個MMCME2_ADV通過參考輸入時鐘產生125MHz和250MHz時鐘。當MMCME2_ADV使用時,用戶可以通過BUFGMUX選擇想要的時鐘。推薦PCIe模式中內部和外部數據位寬相同,此時[TX/RX]USRCLK和[TX/RX]USRCLK2時鐘頻率相同。

在Gen1、Gen2和Gen3中,推薦TX buffer旁路,此時TXOUTCLKSEL必須GTX/GTH收發器參考時鐘通過TXOUTCLK端口后作為TXUSRCLK2的源時鐘。為了最小化TX lane和lane之間偏移,所有lane的TXUSRCLK和TXUSRCLK2必須來源相同的時鐘源。

在Gen1、Gen2和Gen3中,推薦使用RX buffer。當RX buffer應用在同步時鐘應用中,GTX/GTH收發器參考時鐘為RXUSRCLK和RXUSRCLK2的源時鐘。圖3顯示了PCIe同步時鐘應用架構。

圖3、PCIe同步時鐘架構舉例

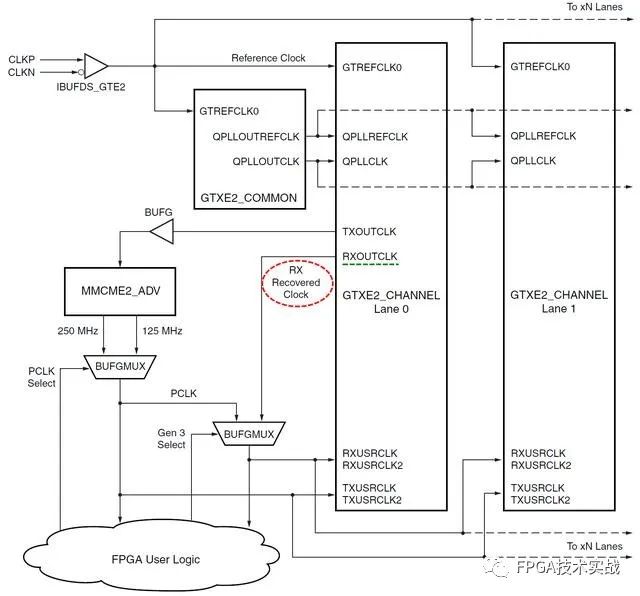

當RX buffer用在異步時鐘應用中,RX恢復時鐘來自主Lane0,作為RXUSRCLK和RXUSRCLK2時鐘源。圖4顯示了PCIe異步時鐘架構,圖中如果使用BUFGMUX原句,則BUFG可以插入PCLK路徑中用于平衡路徑時序。

圖4、PCIe異步時鐘架構舉例

2.XAUI時鐘設計

2.1 參考輸入時鐘

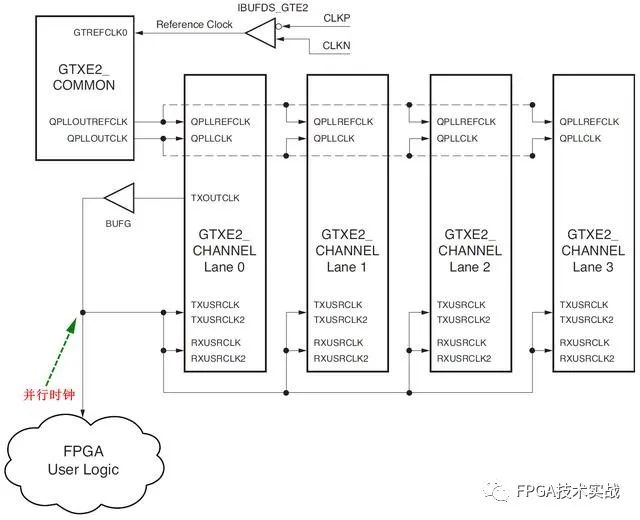

對于XAUI應用,使用單一156.25MHz參考時鐘。如圖5所示,參考輸入時鐘通過IBUFDS_GTE2驅動GTXE2_COMMON。

圖4、XAUI時鐘架構舉例

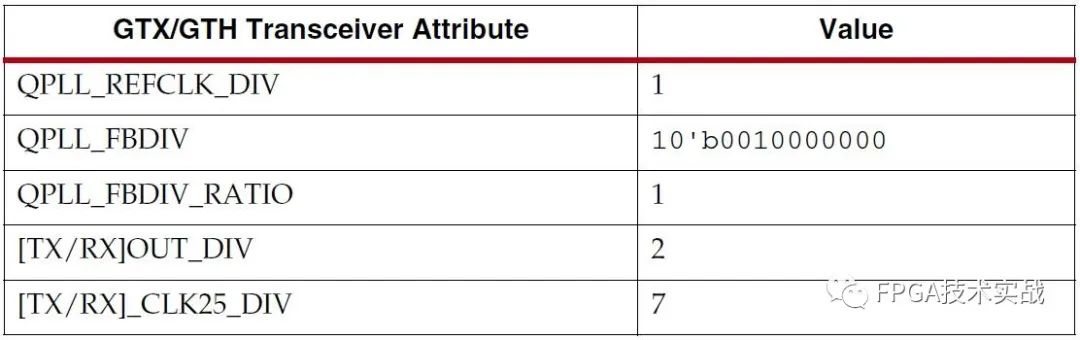

圖5中QPLL推薦的時鐘配置如圖6所示。

圖6、QPLL推薦的時鐘配置

2.2 并行時鐘

在XAUI操作模式中,GTX/GTH收發器內部數據位寬和FPGA接口位寬為2字節位寬,此時,[TX/RX]USRCLK和[TX/RX]USRCLK2頻率相同,即都為156.25MHz。

對于XAUI應用,推薦TX buffer旁路,此時TXOUTCLKSEL設置為3‘b011,使用GTX/GTH收發器參考時鐘作為TXUSRCLK和TXUSRCLK2時鐘源。

原文標題:PCIe和XAUI協議時鐘架構應用實例

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603389 -

PCIe

+關注

關注

15文章

1239瀏覽量

82655

原文標題:PCIe和XAUI協議時鐘架構應用實例

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

影響光纖收發器性能的三大因素

射頻收發器就是基帶嗎

光纖收發器怎么判斷好壞

光纖收發器pwr是什么意思

光纖收發器怎么判斷好壞

光纖收發器的作用、使用方法及應用

光纖收發器怎么區分發射端和接收端

恩智浦MCU解讀 MCX A系列微處理器之時鐘架構

GTX/GTH收發器時鐘架構應用介紹

GTX/GTH收發器時鐘架構應用介紹

評論