引言

近年來,實(shí)時(shí)信號(hào)處理的要求越來越高,所用系統(tǒng)要求具有處理大量數(shù)據(jù)的能力,這就要求系統(tǒng)硬件要達(dá)到很高的運(yùn)算速度,并且軟件處理程序也要盡可能優(yōu)化,以保證系統(tǒng)的實(shí)時(shí)性。本文基于FPGA和ADSP-TS101S所實(shí)現(xiàn)的一種高速數(shù)據(jù)并行處理系統(tǒng),可以進(jìn)行實(shí)時(shí)連續(xù)波和脈沖波的處理,并將連續(xù)波的頻譜和脈沖波脈沖幅度信息、脈前時(shí)刻、脈寬及載頻打包輸出。整個(gè)系統(tǒng)的輸出延時(shí)被控制在1ms之內(nèi)。

系統(tǒng)任務(wù)及系統(tǒng)結(jié)構(gòu)

系統(tǒng)任務(wù)

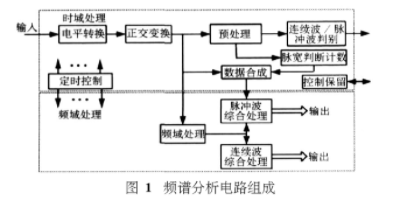

系統(tǒng)頻譜分析電路組成結(jié)構(gòu)如圖1所示。

前端輸入為高頻寬帶模擬信號(hào)經(jīng)過數(shù)字化采樣后得到的數(shù)字信號(hào)。系統(tǒng)主要完成的任務(wù)是對(duì)該數(shù)字信號(hào)進(jìn)行實(shí)時(shí)處理,并識(shí)別出高頻寬帶模擬信號(hào)為連續(xù)波還是脈沖波。如為連續(xù)波,系統(tǒng)計(jì)算出它的頻率,并輸出其頻譜;如為脈沖波,系統(tǒng)計(jì)算出它的脈沖寬度和脈載頻,并把載頻與時(shí)域中的脈沖前沿時(shí)刻信息、寬度信息及幅度信息對(duì)應(yīng)起來,傳送給后面的系統(tǒng)進(jìn)行處理。

系統(tǒng)先對(duì)輸入的數(shù)字信號(hào)進(jìn)行電平轉(zhuǎn)換,然后進(jìn)行正交變換。接下來開始對(duì)信號(hào)進(jìn)行頻域處理,并以1.92μs為最小時(shí)段輸出其頻譜,同時(shí)進(jìn)行預(yù)處理和連續(xù)波/脈沖波判別。對(duì)連續(xù)波,將各小時(shí)段的信號(hào)頻譜進(jìn)行綜合處理后輸出其頻譜。對(duì)脈沖波,確定其脈沖前延時(shí)刻和脈沖后延時(shí)刻,從而確定其脈沖寬度,接著將脈沖幅度、后延時(shí)刻及寬度進(jìn)行數(shù)據(jù)合成,之后再結(jié)合各個(gè)小時(shí)段的頻譜進(jìn)行綜合處理,最終將脈沖幅度信息、脈沖前延時(shí)刻、寬度及載頻打包輸出。

系統(tǒng)結(jié)構(gòu)

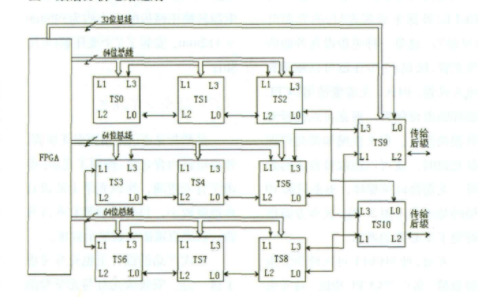

該信號(hào)并行處理系統(tǒng)結(jié)構(gòu)框圖如圖2所示。

該系統(tǒng)主要由1片F(xiàn)PGA和11片TS101系列的DSP構(gòu)成。FPGA首先將16位高速ADC采集進(jìn)來的數(shù)據(jù)預(yù)處理后拼接成64位,使數(shù)據(jù)總線上的數(shù)據(jù)傳輸速率降低為輸入速率的1/4,然后通過數(shù)據(jù)總線依次送給TS0~TS8,同時(shí)產(chǎn)生TS0~TS9的控制信號(hào)DMAR和IRQ來控制每片DSP讀取數(shù)據(jù)總線上的數(shù)據(jù)。

由圖2可以看出,TS0、TS1、TS2(第1組)和TS3、FS4、TS5(第2組)以及TS6、TS7、TS8(第3組)在結(jié)構(gòu)上為完全相同的三部分,且所進(jìn)行的工作也完全相同,都需將處理完的數(shù)據(jù)通過鏈路口送給TS9和TS10。接著由TS9和TS10進(jìn)行綜合比較,最后再通過鏈路口將處理結(jié)果送給后級(jí)板,并將結(jié)果分為3組,可進(jìn)行相同的處理。每片TS101S只有4個(gè)鏈路口,因此TS9和TS10只能提供3個(gè)鏈路口給TS0~FS8,TS0的數(shù)據(jù)通過TS2的鏈路口中轉(zhuǎn)給TS9和TS10,TS1的數(shù)據(jù)也通過TS2的鏈路口中轉(zhuǎn)給TS9和TS10,其它兩組與第1組處理方法相同。

在1.92μs內(nèi),TS0~TS8將接收到的一幀64×64位數(shù)據(jù)拆分?jǐn)U展成256×32位浮點(diǎn)數(shù),然后對(duì)數(shù)據(jù)進(jìn)行32位浮點(diǎn)FFT(快速傅立葉變換)運(yùn)算,接著求模平滑,將得到的頻域數(shù)據(jù)發(fā)送給TS9和TS10進(jìn)行綜合處理。TS9負(fù)責(zé)完成脈沖波綜合處理任務(wù),TS10負(fù)責(zé)完成連續(xù)波綜合處理任務(wù)。最后,TS9和TS10將數(shù)據(jù)通過鏈路口送往后級(jí)進(jìn)行處理。

信號(hào)處理軟件實(shí)現(xiàn)

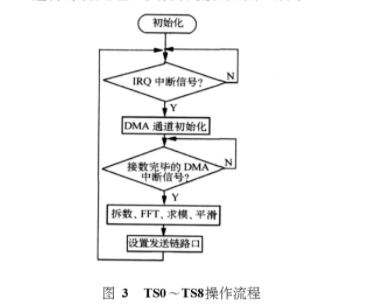

在整個(gè)并行分析系統(tǒng)中,TS0~TS8需要各片DSP在時(shí)序上達(dá)到高度統(tǒng)一,每片DSP都應(yīng)盡量簡化流程,節(jié)約時(shí)間開銷。TS0~TS8的主要任務(wù)是將接收到的數(shù)據(jù)進(jìn)行FFT運(yùn)算,并最終將各個(gè)小段信號(hào)的頻譜發(fā)送到TS9和TS10進(jìn)行綜合處理。其操作流程如圖3。

這里,DSP首先進(jìn)行初始化設(shè)置,設(shè)置完畢進(jìn)入等待,直到接收到FPGA發(fā)出的信號(hào),DSP跳出等待,進(jìn)入IRQ中斷服務(wù)子程序。在IRQ中斷服務(wù)子程序中,進(jìn)行DMA通道初始化,準(zhǔn)備從總線上接數(shù),設(shè)置完畢DSP前臺(tái)進(jìn)入等待。DSP后臺(tái)接數(shù)操作每接到一個(gè)FPGA發(fā)出的信號(hào),就完成接一個(gè)數(shù)。當(dāng)接滿64個(gè)64位數(shù)時(shí),發(fā)出DMA中斷,并使DSP跳出等待,進(jìn)入DMA中斷服務(wù)子程序。在DMA中斷服務(wù)子程序中,進(jìn)行拆數(shù)、FFT、求平方和、平滑等運(yùn)算,待所有運(yùn)算完畢,DSP開始設(shè)置鏈路口,將平滑后的結(jié)果,即128個(gè)32位的數(shù)傳給每組的最后一片,最后一片發(fā)往TS9和TS10。

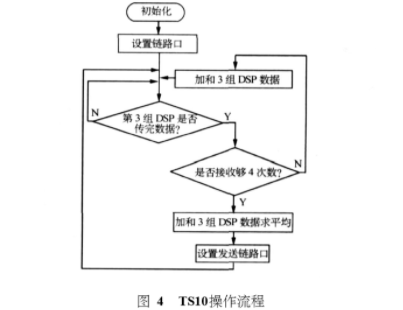

連續(xù)波信號(hào)需要在FFT變換后再做平滑處理,然后依次輸出各頻率點(diǎn)的幅度值,從而獲取連續(xù)波信號(hào)的頻譜信息。具體而言,就是TS0~TS8分成3組,每組3片;每組DSP中,前兩片的鏈路口分別與第3片的鏈路口相連,然后通過第3片的鏈路口將其運(yùn)算結(jié)果傳送到TS10中;以17.28μs×4=69.12μs為一幀,9片DSP分時(shí)并行完成2.56點(diǎn)FFT運(yùn)算和求模運(yùn)算,TS10將這9片DSP的運(yùn)算結(jié)果在一幀內(nèi)進(jìn)行平滑,完成一幀內(nèi)信號(hào)的頻譜分析,同時(shí)將該幀的譜信息打包處理,最后通過TS10的第4個(gè)鏈路口將包數(shù)據(jù)發(fā)送到后級(jí)處理器。圖4為TS10的處理流程圖。

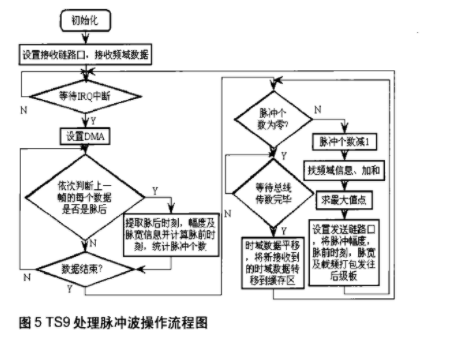

對(duì)于脈沖波綜合處理,其操作流程如圖5所示。

脈沖波綜合處理要同時(shí)輸出該段時(shí)間內(nèi)的時(shí)域脈沖幅度信息、脈沖起始時(shí)間、寬度及載頻信息。上述參數(shù)中,時(shí)域脈沖幅度信息、脈沖起始時(shí)間和脈沖寬度已經(jīng)通過相應(yīng)的DMA中斷送到TS9,TS9通過32位總線中的高24位接收數(shù)據(jù),次高位用于設(shè)置脈后標(biāo)志(即當(dāng)次高位為1時(shí)脈沖結(jié)束,低22位即為脈后時(shí)刻),脈后時(shí)刻前的數(shù)據(jù)為脈沖幅度信息,脈后時(shí)刻后的數(shù)據(jù)信息表示了脈沖寬度,由此可得到脈沖起始時(shí)刻)。

另外,對(duì)于載頻信息,TS0~TS8將FFT結(jié)果送到TS9之中,TS9連續(xù)循環(huán)存儲(chǔ)多幀頻域數(shù)據(jù),由于前9片DSP所得到的信息是按照嚴(yán)格的幀定時(shí)運(yùn)算所得的,所以需要將它們的信息做相應(yīng)的融合合并才能打包輸出。具體融合原則為:

a.當(dāng)在接收到的時(shí)域數(shù)據(jù)中搜索到脈沖結(jié)束標(biāo)志時(shí),計(jì)算出該脈沖的脈前信息,并存儲(chǔ)脈前信息、時(shí)域脈沖幅度信息、脈沖起始時(shí)間及脈沖寬度;

b.在TS0~TS8送來的譜信息中搜索,與存儲(chǔ)的時(shí)域脈沖波信息相結(jié)合確定脈沖波,且將數(shù)個(gè)小段數(shù)據(jù)(1.92μs)內(nèi)的幾個(gè)(最多只加5個(gè))譜信息組合合并,得到相對(duì)完整準(zhǔn)確的脈沖載頻;

c.向后級(jí)發(fā)送數(shù)據(jù)時(shí)發(fā)送脈沖前沿時(shí)刻、時(shí)域幅度信息、脈寬及載頻等信息。

結(jié)語

本文中的高速實(shí)時(shí)信號(hào)并行處理系統(tǒng)已通過測試,系統(tǒng)能夠完成連續(xù)波和脈沖波的處理,對(duì)連續(xù)波計(jì)算出它的頻率并輸出其頻譜,對(duì)脈沖波計(jì)算出它的脈沖寬度和脈沖載頻,并把脈沖載頻與時(shí)域中的脈沖前沿時(shí)刻信息,脈沖寬度信息及脈沖幅度信息很好地對(duì)應(yīng)起來打包輸出。各個(gè)DSP算法程序均已完成,并已通過測試。整個(gè)DSP中程序均使用匯編程序編寫,最大地簡化了運(yùn)算流程,節(jié)約了時(shí)間開銷。

編輯:jq

-

脈沖

+關(guān)注

關(guān)注

20文章

900瀏覽量

96389 -

電平轉(zhuǎn)換

+關(guān)注

關(guān)注

3文章

148瀏覽量

34078 -

連續(xù)波

+關(guān)注

關(guān)注

0文章

10瀏覽量

10367

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

芯有靈犀智創(chuàng)未來,基于中科億海微FPGA實(shí)現(xiàn)圖像處理系統(tǒng)及應(yīng)用——第九屆集創(chuàng)賽中科億海微杯賽題解析

EE-174:ADSP-TS101S TigerSHARC處理器引導(dǎo)加載程序內(nèi)核操作

EE-218:為ADSP-TS201 TigerSHARC處理器編寫高效浮點(diǎn)FFT

EE-217:更新ADSP-TS101S TigerSHARC EZ-KIT Lite固件

EE-176:ADSP-TS101S TigerSHARC處理器硬件設(shè)計(jì)核對(duì)表

EE-205:將代碼從ADSP-TS101S TigerSHARC處理器移植到ADSP-TS201S TigerSHARC處理器的注意事項(xiàng)

EE-169:估算ADSP-TS101S的功耗

EE-182:ADSP-TS201S TigerSHARC處理器散熱設(shè)計(jì)

EE-157:ADSP-TS101上的分支目標(biāo)緩沖器說明

EE-178:ADSP-TS101S TigerSHARC片上SDRAM控制器

EE-170:估算ADSP-TS201S TigerSHARC處理器的功耗

AN-813: ADSP-BF533/ADSP-BF561 Blackfin處理器與高速并行ADC接口

評(píng)論