作者:馬翔;馮正和;陳雅琴

隨著通信技術(shù)的快速發(fā)展,各種新業(yè)務(wù)的層出不窮,無(wú)線通信以其方便、靈活、易于組網(wǎng)等特點(diǎn)獲得了廣泛的應(yīng)用。其中特別是擴(kuò)頻通信技術(shù)由于其抗干擾、抗多徑的突出優(yōu)點(diǎn),獲得了各方的青睞,無(wú)線擴(kuò)頻產(chǎn)品的開(kāi)發(fā)研制已成為國(guó)內(nèi)外通信界的一個(gè)熱點(diǎn)。同時(shí)擴(kuò)頻通信技術(shù)也已經(jīng)超出了無(wú)線通信的領(lǐng)域,在一些“有線 ”的領(lǐng)域內(nèi)得到了充分應(yīng)用,如電力線通信系統(tǒng)等。

HARRIS公司的HSP3824直接序列擴(kuò)頻基帶處理器是其24GHz天線芯片組的一部分,它包含了全雙工或半雙工收發(fā)機(jī)的所有功能。該芯片的最突出特點(diǎn)是靈活,其數(shù)據(jù)率、擴(kuò)頻比、調(diào)制方式以及PN碼等都可以根據(jù)需要而動(dòng)態(tài)調(diào)整,也可以通過(guò)設(shè)置HSP3824內(nèi)部寄存器來(lái)實(shí)現(xiàn)大量的應(yīng)用,為設(shè)計(jì)提供了較大的靈活性。實(shí)踐證明該芯片可靠易用,是開(kāi)發(fā)擴(kuò)頻通信產(chǎn)品的良好選擇。

1 HSP3824主要功能和特點(diǎn)

HSP3824是HARRIS(Intersil)公司開(kāi)發(fā)的用于直接序列擴(kuò)頻通信的基帶處理器。其基本功能是將接收到的基帶數(shù)據(jù)擾碼、調(diào)制、直接序列擴(kuò)頻輸出至中頻調(diào)制。或反之,將中頻解調(diào)后的信號(hào)經(jīng)A/D變換、解擴(kuò)、解調(diào)、解擾后得到基帶數(shù)據(jù)并輸出。

它的主要特點(diǎn)如下[1]:

完全的直接序列擴(kuò)頻基帶處理器(DSSS基帶處理器);

處理增益最高12dB;

可編程PN碼11、13、15、16位可選;

可編程數(shù)據(jù)率,最高達(dá)4Mbps;

適合于PCMCIA板應(yīng)用的TQFP封裝;

調(diào)制方式DBPSK、DQPSK可選;

支持半雙工、全雙工操作;

內(nèi)置A/D轉(zhuǎn)換器;

低功耗,某些模塊在不工作時(shí)可置為SLEEP狀態(tài)。

HSP3824內(nèi)置57個(gè)寄存器,這些寄存器的值決定了它的工作狀態(tài),外部控制器可對(duì)這些寄存器進(jìn)行讀寫(xiě)。通過(guò)正確配置寄存器,可實(shí)現(xiàn)HSP3824的各種功能,且可以動(dòng)態(tài)調(diào)整。

除了基本的發(fā)送、接受模塊之外,HSP3824還包括8位的測(cè)試總線,用于測(cè)試芯片的內(nèi)部信號(hào),實(shí)時(shí)反映芯片的工作情況;輸入信號(hào)強(qiáng)度檢測(cè)和信道空檢測(cè)(CCA)可避免數(shù)據(jù)阻塞,優(yōu)化網(wǎng)絡(luò)傳輸;還可以由外部控制端口設(shè)置為各種功耗模式。

2 HSP3824內(nèi)部結(jié)構(gòu)及使用要點(diǎn)

2.1 內(nèi)部結(jié)構(gòu)及外部接口

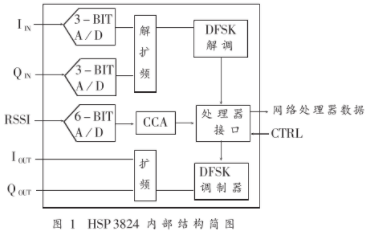

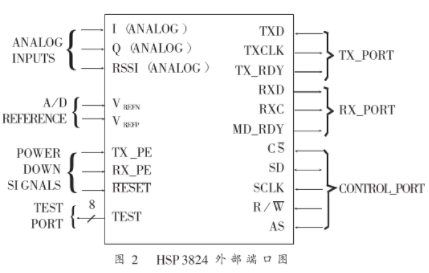

HSP3824可大體上分為三部分:控制、發(fā)送及接收。相應(yīng)地對(duì)外分別提供三個(gè)數(shù)字端口與控制器相連,即控制端口 (CONTROL_PORT)、發(fā)送端口(TX_PORT)及接收端口(RX_PORT),且這三個(gè)端口可分別獨(dú)立工作或同時(shí)工作。此外,還具有一個(gè)測(cè)試端口(TEST_PORT),供外部控制器監(jiān)控HSP3824的工作狀態(tài)。

HSP3824的內(nèi)部結(jié)構(gòu)簡(jiǎn)圖如圖1所示。

IIN:接收到的I路模擬信號(hào);

QIN:接收到的Q路模擬信號(hào);

RSSI:接收信號(hào)強(qiáng)度檢測(cè)(模擬信號(hào));

IOUT:I路輸出擴(kuò)頻基帶數(shù)字信號(hào);

QOUT:路輸出擴(kuò)頻基帶數(shù)字信號(hào);

HSP3824外部端口如圖2所示。除四個(gè)數(shù)字端口外,還有模擬輸入(ANALOG INPUTS)、A/D參考電壓(A/D REFERENCE)及省電模式控制信號(hào)(POWER DOWN SIGNALS)等接口。需要強(qiáng)調(diào)的是每個(gè)數(shù)字端口都有其嚴(yán)格的時(shí)序關(guān)系,只有在滿(mǎn)足時(shí)序的條件下HSP3824才能正常工作。其中尤其是控制端口,是設(shè)置并保證HSP3824良好工作狀態(tài)的關(guān)鍵。

2.2 控制端口時(shí)序圖

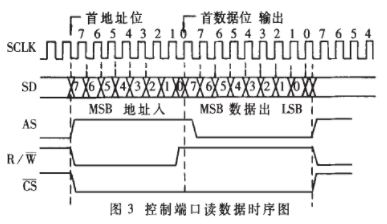

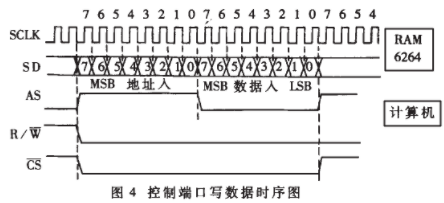

為確保HSP3824按照設(shè)計(jì)者的要求正確工作,關(guān)鍵的一點(diǎn)是實(shí)現(xiàn)HSP3824內(nèi)部控制寄存器的正確讀寫(xiě)。這些內(nèi)部寄存器包括發(fā)送/接收PN 碼長(zhǎng)度寄存器,發(fā)送/接收PN碼字寄存器,調(diào)制/解調(diào)方式寄存器等57個(gè),存儲(chǔ)了HSP3824正常工作所需的全部參數(shù)及一些內(nèi)部狀態(tài)。因此在每次重新上電時(shí),都必須首先由外部控制器通過(guò)HSP3824的控制端口實(shí)現(xiàn)這些寄存器的正確配置,之后才能正常工作。在正常工作時(shí),也可通過(guò)該控制端口讀出內(nèi)部寄存器的值,供控制器分析、監(jiān)控系統(tǒng)運(yùn)行狀態(tài),還可以在需要時(shí)通過(guò)改變寄存器的配置來(lái)調(diào)整HSP3824的工作方式。

要實(shí)現(xiàn)內(nèi)部寄存器的正確讀寫(xiě),必須滿(mǎn)足HSP3824控制端口要求的時(shí)序關(guān)系。其時(shí)序分為讀寫(xiě)兩種,分別如圖3及圖4所示。

其中,各數(shù)據(jù)線的含義及作用如下:

SCLK:數(shù)據(jù)時(shí)鐘,HSP3824在它的上升沿采樣或送出數(shù)據(jù),由它決定了讀寫(xiě)操作的速度。需要引起注意的是SCLK應(yīng)提前SD幾個(gè)周期就準(zhǔn)備好,且SCLK的速度不能大于1/2倍的系統(tǒng)主時(shí)鐘MCLK。

SD:串行輸入/輸出的數(shù)據(jù),包括寄存器的地址和值。在每次讀/寫(xiě)一個(gè)寄存器時(shí),SD的前8位都應(yīng)該是地址,后8位為數(shù)據(jù),且均是低位在前。

AS:區(qū)分?jǐn)?shù)據(jù)線SD上送的信號(hào)是寄存器的地址還是數(shù)值,AS=1表示SD為地址,AS=0表示SD為數(shù)值。

R/:表示對(duì)于HSP3824而言,控制端口進(jìn)行的是讀還是寫(xiě)操作,RS=0為寫(xiě)操作,RS=1為讀操作。

為使能信號(hào),只有在=0時(shí)控制端口才能進(jìn)行讀寫(xiě)。

2.3 應(yīng)注意的關(guān)鍵問(wèn)題及其解決

HSP3824內(nèi)部寄存器的讀寫(xiě)除要求滿(mǎn)足以上條件外,還必須滿(mǎn)足如圖5所示的HSP3824主時(shí)鐘MCLK和數(shù)據(jù)時(shí)鐘SCLK之間的時(shí)序關(guān)系[2]。

從圖中可以看出此條件要求很高,特別是因?yàn)镾CLK是由外部控制器給出,而MCLK是由一個(gè)晶振送給HSP3824的工作時(shí)鐘,兩者之間沒(méi)有任何邏輯上的關(guān)系。因此必須采取一些額外的措施來(lái)解決此問(wèn)題。

在硬件上,可增加如圖6所示的電路。其中DCLK由外部控制器提供,由晶振提供。利用的反相信號(hào)CLK的上升沿(即MCLK的下降沿)觸發(fā)DCLK,輸出SCLK。同時(shí)CLK再經(jīng)過(guò)一級(jí)反相器,得到MCLK。圖中的D觸發(fā)器和反相器都需要選擇快速的74F系列。這樣得到的MCLK和SCLK才能滿(mǎn)足圖5所示的條件。同時(shí),可以在軟件上采取些措施,如每寫(xiě)一個(gè)寄存器之后馬上讀該寄存器,并與預(yù)期值比較,若不符則重新寫(xiě)入,否則繼續(xù)下一個(gè)寄存器的讀寫(xiě)。通過(guò)以上兩方面的措施,可確保寄存器的正確配置。

HSP3824的工作速度由MCLK決定,這個(gè)工作速度可以很高(高達(dá)44MHz)。因此,在確定的工作速度下,必須要求MCLK無(wú)抖動(dòng),特別是無(wú)毛刺,否則HSP3824會(huì)產(chǎn)生誤動(dòng),致使工作狀態(tài)不正常。可通過(guò)在MCLK送入HSP3824之前串接一個(gè)小電阻,對(duì)地并接一個(gè)小電容來(lái)防止毛刺的干擾。

3 利用HSP3824實(shí)現(xiàn)擴(kuò)頻通信的應(yīng)用舉例

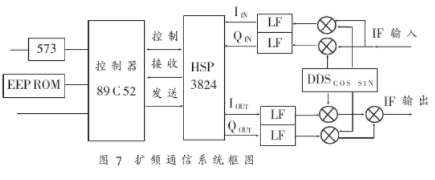

在HARRIS公司研制的24GHz天線芯片組中包括與HSP3824配套使用的中頻調(diào)制解調(diào)器、頻率綜合器、上下變頻器及雙工器等芯片。但其價(jià)格昂貴,不適用于現(xiàn)有的工程項(xiàng)目。故筆者僅利用了HSP3824芯片,自行設(shè)計(jì)了其它相關(guān)電路,實(shí)現(xiàn)擴(kuò)頻通信模塊。其中利用單片機(jī)89C52作為控制器,控制整個(gè)系統(tǒng)工作狀態(tài)及實(shí)現(xiàn)基帶數(shù)據(jù)處理;利用EPROM及D/A變換器構(gòu)成直接數(shù)字頻率綜合器(DDS),實(shí)現(xiàn)中頻調(diào)制解調(diào);其它外圍電路包括地址鎖存器、靜態(tài)RAM、EEPROM及其它輔助電路。系統(tǒng)框圖如圖7所示。

在圖7中,計(jì)算機(jī)完成兩個(gè)功能。其一是模擬以后實(shí)際工程中的數(shù)據(jù)采集單元或控制中心,利用它的RS232接口與89C52通信[3],提供或接受數(shù)據(jù);另一個(gè)功能就是用作將來(lái)在現(xiàn)場(chǎng)調(diào)整一些參數(shù)的設(shè)置,包括擴(kuò)頻碼長(zhǎng)度的選擇、對(duì)應(yīng)的擴(kuò)頻碼、數(shù)據(jù)率、功率等。其中對(duì)擴(kuò)頻碼及其長(zhǎng)度,通信的數(shù)據(jù)率這幾個(gè)參數(shù)的調(diào)整,實(shí)際上是改變HSP3824內(nèi)部寄存器的設(shè)置。其工作流程主要是工作人員通過(guò)計(jì)算機(jī)的人機(jī)界面設(shè)定滿(mǎn)足實(shí)際條件的參數(shù),利用計(jì)算機(jī)的串行通信口遵循RS232C協(xié)議,將命令傳達(dá)至89C52。單片機(jī)利用這些收到的參數(shù)去修改HSP3824內(nèi)部對(duì)應(yīng)的寄存器,同時(shí)將這些參數(shù)存儲(chǔ)在 EEPROM中。之后系統(tǒng)將一直維持這些選定的參數(shù)設(shè)置,直至下一次被修改。

以直接序列擴(kuò)頻通信基帶處理器HSP3824為核心設(shè)計(jì)了擴(kuò)頻通信模塊,并使之工作在較低頻率及數(shù)據(jù)率上,實(shí)踐證明其外圍電路簡(jiǎn)單,性能可靠。同時(shí)也說(shuō)明HSP3824具有廣泛的應(yīng)用領(lǐng)域,其處理的數(shù)據(jù)率可以從低至幾千,到高達(dá)幾十兆;并且對(duì)它的控制簡(jiǎn)單、靈活,可動(dòng)態(tài)調(diào)整若干參數(shù),實(shí)現(xiàn)最有效的應(yīng)用;若結(jié)合其測(cè)試功能及輸入信號(hào)強(qiáng)度檢測(cè)和信道空檢測(cè)功能,可以設(shè)計(jì)出功能更強(qiáng)大、更靈活、可靠的產(chǎn)品。但它也有其固有的缺點(diǎn),主要是擴(kuò)頻碼長(zhǎng)較短,不能獲得較高的擴(kuò)頻增益,限制了系統(tǒng)的抗噪聲及抗多徑效應(yīng)的能力。以上優(yōu)缺點(diǎn)需要設(shè)計(jì)人員綜合考慮,以充分發(fā)揮其功能,設(shè)計(jì)出最佳的產(chǎn)品。

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19286瀏覽量

229854 -

封裝

+關(guān)注

關(guān)注

126文章

7903瀏覽量

142966 -

無(wú)線通信

+關(guān)注

關(guān)注

58文章

4570瀏覽量

143543

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

擴(kuò)頻通信理論基礎(chǔ)+主要介紹bpsk的調(diào)制

擴(kuò)頻通信技術(shù) -電子書(shū)(共六章)

擴(kuò)頻通信技術(shù)教程

擴(kuò)頻通信系統(tǒng)的分類(lèi)及原理

擴(kuò)頻通信系統(tǒng)簡(jiǎn)介

擴(kuò)頻通信技術(shù)及應(yīng)用

擴(kuò)頻通信的優(yōu)點(diǎn)

什么是擴(kuò)頻通信,擴(kuò)頻通信的定義

小波在擴(kuò)頻通信中的應(yīng)用

m序列、Gold序列和正交Gold序列的擴(kuò)頻通信系統(tǒng)仿真研究

基于MATLAB的直接序列擴(kuò)頻通信系統(tǒng)課程設(shè)計(jì)報(bào)告

DDS芯片AD9854及其在擴(kuò)頻通信中的應(yīng)用_胡淑均

擴(kuò)頻通信的基本原理(SystemView仿真)

HSP3824直接序列擴(kuò)頻基帶處理器的功能特點(diǎn)及在擴(kuò)頻通信中應(yīng)用

HSP3824直接序列擴(kuò)頻基帶處理器的功能特點(diǎn)及在擴(kuò)頻通信中應(yīng)用

評(píng)論