航天技術(shù)的發(fā)展,對遙測系統(tǒng)的性能要求越來越高。飛行器復(fù)雜程度的加大、測量參數(shù)種類的增多、數(shù)據(jù)量的增大、測量實(shí)時(shí)性的增強(qiáng)使傳統(tǒng)有限傳輸信道容量的遙測系統(tǒng)面臨巨大挑戰(zhàn)。為此,可以通過采用數(shù)據(jù)壓縮技術(shù),有效地提高信道利用率,減少遙測數(shù)據(jù)的傳輸時(shí)間和存儲空間,增強(qiáng)遙測數(shù)據(jù)的實(shí)時(shí)性和吞吐率。

設(shè)計(jì)的數(shù)據(jù)壓縮器以FPGA為控制單元,用DSP實(shí)現(xiàn)數(shù)據(jù)壓縮,可將6路模擬信號采集并壓縮,再經(jīng)長線發(fā)送至數(shù)據(jù)接收器。實(shí)現(xiàn)硬件模塊化、功能軟件化設(shè)計(jì),依靠FPGA的并行執(zhí)行特性,結(jié)合高速DSP通信,可靠地完成被測信號的采集、壓縮功能。在保證系統(tǒng)可靠性的同時(shí)節(jié)省系統(tǒng)的開發(fā)成本,提高了系統(tǒng)的可重構(gòu)性[1-2]。

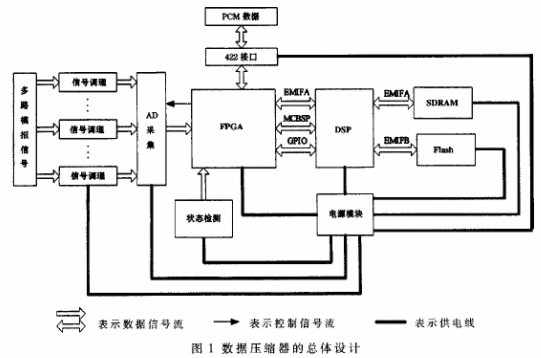

1 數(shù)據(jù)壓縮器的總體設(shè)計(jì)

數(shù)據(jù)壓縮器基于FPGA和DSP的硬件平臺,將待壓縮的6路模擬信號經(jīng)過調(diào)理后輸入給A/D轉(zhuǎn)換器進(jìn)行量化,F(xiàn)PGA將量化結(jié)果寫入其內(nèi)部FIFO(First In First Out)緩存中。DSP通過判斷FIFO的半滿信號讀取數(shù)據(jù),并根據(jù)通道號把數(shù)據(jù)流分配到6個(gè)分組緩存區(qū),當(dāng)其中任一分組緩存區(qū)滿2 KB時(shí),就進(jìn)行一次壓縮,壓縮后的數(shù)據(jù)被存入緩存器中。

當(dāng)緩存器半滿時(shí),DSP將壓縮后的數(shù)據(jù)串行發(fā)送至FPGA,F(xiàn)PGA根據(jù)接口的通信協(xié)議再把壓縮數(shù)據(jù)發(fā)送給數(shù)據(jù)接收器,以保證壓縮數(shù)據(jù)傳輸?shù)膶?shí)時(shí)性。壓縮器的總體設(shè)計(jì)方案如圖1所示[3-5]。

2 硬件及實(shí)現(xiàn)原理

2.1 控制單元的選型

FPGA采用XILINX公司的低成本產(chǎn)品XC3S200AN。其包含豐富的Block RAM資源,可利用IP核建立內(nèi)部FIFO,以便于數(shù)據(jù)緩存。XC3S200AN內(nèi)部含有4 MB大小的Flash,可以存儲FPGA程序。DSP是執(zhí)行數(shù)據(jù)壓縮的核心單元器件,選型時(shí)在考慮處理速度的同時(shí),還要兼顧其與其他設(shè)備的接口匹配能力。選用TI公司的TMS320C6416高性能DSP,其CPU工作主頻達(dá)到600 MHz,內(nèi)含容量為1 MB的RAM內(nèi)存,同時(shí)可通過外部存儲器接口(EMIF)、多通道緩存串口(MCBSP)等外設(shè)接口與FPGA及存儲器連接。

2.2 信號采集電路設(shè)計(jì)

設(shè)計(jì)要實(shí)現(xiàn)對6個(gè)通道的信號進(jìn)行每通道30 kHz、8位分辨率的采樣,相當(dāng)于總采樣率180 kHz。選用TI公司的16位、250 kS/s、6通道同步采樣模數(shù)轉(zhuǎn)換器ADS8365,能夠滿足要求[2]。為了保證模擬信號能被正確量化,先采用運(yùn)算放大器OPA4340對信號進(jìn)行電壓跟隨,再由FPGA控制ADS8365進(jìn)行采樣。

通過在FPGA內(nèi)部建立FIR濾波器IP核對采集到的數(shù)據(jù)進(jìn)行數(shù)字濾波,隨后將其低13位并置3位通道編號發(fā)送給DSP。DSP工作頻率通常能達(dá)到幾百兆赫茲,但FPGA的工作頻率僅為幾十兆赫茲,所以FPGA要將數(shù)據(jù)先緩存在其內(nèi)部FIFO,便于DSP讀取[6-8]。信號調(diào)理電路如圖2所示。

2.3 DSP的通信接口設(shè)計(jì)

DSP從FPGA中讀取采樣數(shù)據(jù)進(jìn)行壓縮,再將壓縮后數(shù)據(jù)發(fā)回FPGA,由FPGA進(jìn)行編碼后發(fā)送到數(shù)據(jù)接收器。由于數(shù)據(jù)壓縮需要較大的處理空間,而DSP內(nèi)部存儲空間有限,為防止在數(shù)據(jù)壓縮期間內(nèi)采樣數(shù)據(jù)和壓縮結(jié)果因不能及時(shí)傳送而丟失,故在數(shù)據(jù)輸入、輸出接口之間設(shè)計(jì)了緩存單元。采樣數(shù)據(jù)輸入緩存可用FPGA內(nèi)部FIFO承擔(dān),考慮到FPGA內(nèi)部RAM資源有限,僅能搭建容量較小的FIFO,而需要的是大容量數(shù)據(jù)輸出緩存單元。

因此,設(shè)計(jì)中DSP的外部存儲采用64 MB容量,能夠緩存1 MB壓縮數(shù)據(jù),64位數(shù)據(jù)寬度的同步動(dòng)態(tài)隨機(jī)存儲器(SDRAM)MT48LC2M32B2TG芯片。DSP在采集數(shù)據(jù)時(shí)的數(shù)據(jù)通信操作較復(fù)雜,如果按照外設(shè)的器件手冊編程實(shí)現(xiàn)對其控制效率太低,而用DSP的外部存儲器接口EMIFA可極大地簡化操作過程,將采集數(shù)據(jù)FIFO映射到EMIFA的CE2空間;

將SDRAM映射到CE0空間,只需設(shè)置DSP的EMIFA相關(guān)寄存器參數(shù)即可實(shí)現(xiàn)數(shù)據(jù)通信。同樣可通過設(shè)置DSP的MCBSP相關(guān)寄存器參數(shù)來完成壓縮后數(shù)據(jù)的發(fā)送[9-11]。連接如圖3所示。

3 邏輯控制

3.1 FPGA邏輯設(shè)計(jì)

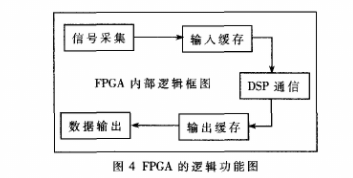

壓縮器中,F(xiàn)PGA作為控制單元,完成6路模擬信號采集的邏輯控制、數(shù)據(jù)傳輸控制以及與DSP的數(shù)據(jù)傳輸。如圖4所示,F(xiàn)PGA邏輯功能可劃分為4個(gè)模塊,分別為信號采集模塊、數(shù)據(jù)輸入緩存模塊、DSP通信模塊和數(shù)據(jù)輸出模塊。其中數(shù)據(jù)輸入、輸出緩存模塊的實(shí)現(xiàn),可通過調(diào)用FPGA的IP核設(shè)置參數(shù)生成相應(yīng)容量的FIFO來完成。

3.2 DSP程序設(shè)計(jì)

DSP程序模塊主要完成模擬信號的壓縮處理。DSP的程序包括模擬數(shù)據(jù)的預(yù)處理、模擬數(shù)據(jù)的壓縮以及與外部存儲器的通信等。DSP程序流程圖如圖5所示[12-14]。

TMS320C6416在上電啟動(dòng)或者復(fù)位后,DSP程序從Flash中加載并啟動(dòng),完成系統(tǒng)的初始化以及各個(gè)參數(shù)的設(shè)置,然后進(jìn)入主函數(shù)、初始化CSL函數(shù)庫、MCBSP、可編程輸入輸出接口(GPIO)等相關(guān)中斷寄存器和內(nèi)部FIFO。當(dāng)TMS320C6416檢測到輸入FIFO半滿信號,DSP從輸入FIFO中讀取模擬信號的量化值,當(dāng)SBUF中有待處理標(biāo)志時(shí),

DSP啟動(dòng)ARC編碼開始數(shù)據(jù)壓縮,ARC編碼將返回壓縮后的數(shù)據(jù)長度,如果壓縮后的數(shù)據(jù)長度比壓縮前的小,DSP將壓縮后數(shù)據(jù)寫入內(nèi)部數(shù)據(jù)發(fā)送緩存器,反之則將壓縮前的數(shù)據(jù)直接寫入。同時(shí)DSP不斷監(jiān)測內(nèi)部緩存的狀態(tài)與外部輸出FIFO中數(shù)據(jù)狀態(tài),當(dāng)內(nèi)部FIFO數(shù)據(jù)量大于512 B,同時(shí)外部FIFO不半滿,DSP從內(nèi)部FIFO取出數(shù)據(jù)啟動(dòng)MSBSP傳輸,將壓縮后的數(shù)據(jù)發(fā)送到FPGA。

3.3 無損壓縮算法及實(shí)現(xiàn)

通過試驗(yàn),比較ARC、WINZIP、WINRAR、字典編碼等常用的數(shù)據(jù)無損壓縮算法的壓縮結(jié)果。在壓縮去除率、壓縮速度以及穩(wěn)定性等各方面綜合分析后,最終采用ARC編碼。ARC編碼采用依次遞推方式,對全序列連續(xù)編碼。ARC算法不是依據(jù)每個(gè)信源符號單獨(dú)映射后編碼,而是將整個(gè)信號符號序列全部映射到實(shí)數(shù)軸上(0,1)區(qū)間內(nèi)的一個(gè)子區(qū)間內(nèi),子區(qū)間長度等于該序列的概率。

當(dāng)整個(gè)序列映射完畢,就可以用一個(gè)概率值表示,可以在子區(qū)間內(nèi)選擇一個(gè)有代表性的介于0和1之間的二進(jìn)制小數(shù)作為實(shí)際的ARC編碼輸出,從而實(shí)現(xiàn)高效編碼。例如,算術(shù)編碼對某條輸入信號序列的輸出為1011001111,它表示小數(shù)0.101100111,即十進(jìn)制數(shù)0.72。在VC中編譯調(diào)試后,再將算法移植到DSP開發(fā)平臺CCS3.3上繼續(xù)編譯直到通過[15-16]。

4 測試結(jié)果

數(shù)據(jù)壓縮器地面測試臺是專門用來對數(shù)據(jù)壓縮器進(jìn)行單元測試的,它可以完全地模擬數(shù)據(jù)壓縮器在實(shí)際環(huán)境下的電氣工作環(huán)境。地面測試臺通過電纜傳輸?shù)綁嚎s器信號輸入接口,壓縮器采集處理完畢,把數(shù)據(jù)通過422接口回傳到地面測試臺,測試臺將接收到的數(shù)據(jù)通過USB接口存儲到計(jì)算機(jī)以便事后分析處理。測試系統(tǒng)結(jié)構(gòu)圖如圖6所示。

對采集到的6組遙測信號利用ARC算法進(jìn)行32 min無損壓縮,測試得到162.8 MB的數(shù)據(jù)。可得壓縮去除率為:

1-162.8 MB/(6×30 kHz×8 bit×32×60 s)=52.9%

壓縮過程中SDRAM的最大占用比例為55%。通過MATLAB工具,對一路壓縮前的原始數(shù)據(jù)和解壓還原后數(shù)據(jù)進(jìn)行頻域分析,圖7和圖8分別為兩者的幅頻特性圖,橫軸為頻率值,縱軸為幅值。實(shí)測噪聲的主要頻率分布在1~2 kHz的范圍內(nèi),解壓后,由于前端濾波器的作用,頻率大于10 kHz的部分基本被濾掉,但數(shù)據(jù)主要成分基本保持下來,能比較真實(shí)地反映數(shù)據(jù)的實(shí)際分布情況。

通過對比,可以看出原始數(shù)據(jù)與解壓后數(shù)據(jù)具有一致性,壓縮器的壓縮性能良好,可以較好地完成數(shù)據(jù)壓縮任務(wù),而且在設(shè)計(jì)指標(biāo)上考慮了一定冗余量,提高了壓縮裝置的可靠性,減輕遙測系統(tǒng)的傳輸帶寬壓力。

為有效降低遙測速變數(shù)據(jù)單信道容量,從而在有限的帶寬中增加更多的測試通道和測試參數(shù),提高帶寬利用率,通過對壓縮機(jī)理的研究、壓縮算法的比較及相關(guān)硬件的設(shè)計(jì),總體上實(shí)現(xiàn)了遙測噪聲數(shù)據(jù)的無損壓縮。通過單元測試,充分驗(yàn)證了所設(shè)計(jì)的遙測噪聲數(shù)據(jù)無損壓縮裝置的正確性與可靠性。數(shù)據(jù)無損壓縮對當(dāng)前許多應(yīng)用領(lǐng)域都產(chǎn)生了深遠(yuǎn)的影響,特別是在航天遙測領(lǐng)域,意義重大。

針對目前的研究情況,進(jìn)一步需改進(jìn)的問題包括:(1)數(shù)據(jù)采集部分可以在現(xiàn)有遙測噪聲數(shù)據(jù)采集的基礎(chǔ)上,結(jié)合FPGA的高性能和AD器件的更新,增加提高數(shù)據(jù)采集路數(shù),提高采集速率和精度。(2)優(yōu)化ARC編碼方式。可以結(jié)合其他的算法,實(shí)現(xiàn)算法自適應(yīng)以增強(qiáng)數(shù)據(jù)處理適應(yīng)能力,進(jìn)一步提高壓縮器性能。(3)推廣技術(shù)的使用范圍,比如應(yīng)用在數(shù)據(jù)采編、存儲等各個(gè)領(lǐng)域,以節(jié)省數(shù)據(jù)存儲容量開銷。

編輯:jq

-

USB接口

+關(guān)注

關(guān)注

9文章

702瀏覽量

55725 -

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7102瀏覽量

89282 -

ARC

+關(guān)注

關(guān)注

0文章

42瀏覽量

16501 -

壓縮器

+關(guān)注

關(guān)注

0文章

26瀏覽量

7814

發(fā)布評論請先 登錄

相關(guān)推薦

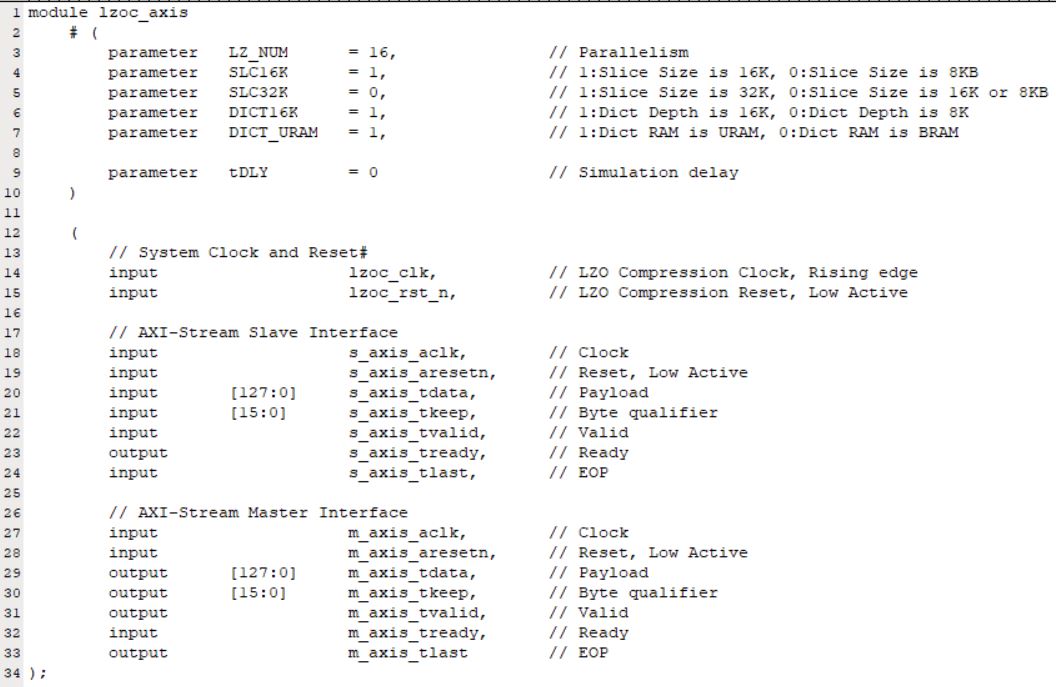

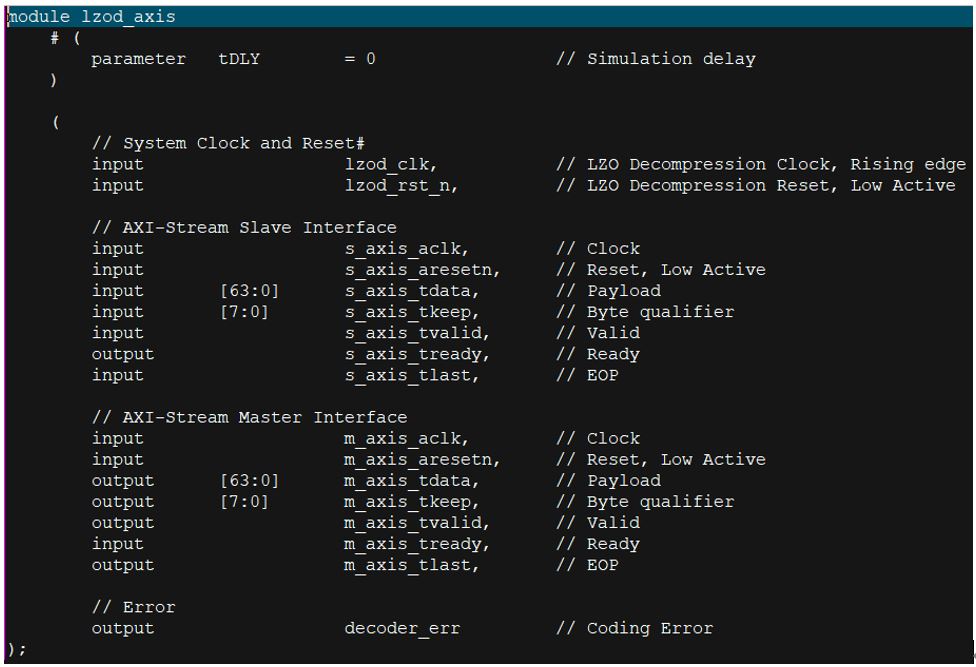

LZO Data Compression,高性能LZO無損數(shù)據(jù)壓縮加速器介紹,F(xiàn)PGA&ASIC

EE-257:面向Blackfin處理器的引導(dǎo)壓縮/解壓縮算法

【BearPi-Pico H3863星閃開發(fā)板體驗(yàn)連載】LZO壓縮算法移植

PolarDB-MySQL引擎層的索引前綴壓縮能力的技術(shù)實(shí)現(xiàn)和效果

壓縮算法的類型和應(yīng)用

Huffman壓縮算法概述和詳細(xì)流程

使用qboot時(shí)選擇了壓縮率更高的zip算法,但是發(fā)現(xiàn)編譯報(bào)錯(cuò),為什么?

ECU刷寫流程之壓縮刷寫技術(shù)解析

華為云GaussDB數(shù)據(jù)庫基礎(chǔ)版發(fā)布:旗艦性能、價(jià)格下降超60%

【RTC程序設(shè)計(jì):實(shí)時(shí)音視頻權(quán)威指南】音視頻的編解碼壓縮技術(shù)

基于門控線性網(wǎng)絡(luò)(GLN)的高壓縮比無損醫(yī)學(xué)圖像壓縮算法

NanoEdge AI的技術(shù)原理、應(yīng)用場景及優(yōu)勢

高性能無損數(shù)據(jù)解壓縮FPGA IP,LZO無損數(shù)據(jù)解壓縮IP

高性能無損數(shù)據(jù)壓縮FPGA IP,LZO無損數(shù)據(jù)壓縮IP

關(guān)于ARC算法的數(shù)據(jù)壓縮技術(shù)和實(shí)現(xiàn)

關(guān)于ARC算法的數(shù)據(jù)壓縮技術(shù)和實(shí)現(xiàn)

評論