FPGA的MultiBoot功能可以支持遠程動態更新bitstream images,實現bitstream images的實時切換。在MultiBoot配置過程中檢測到錯誤時,FPGA可以觸發fallback 功能,以確保可以將已知良好的設計加載到器件中。

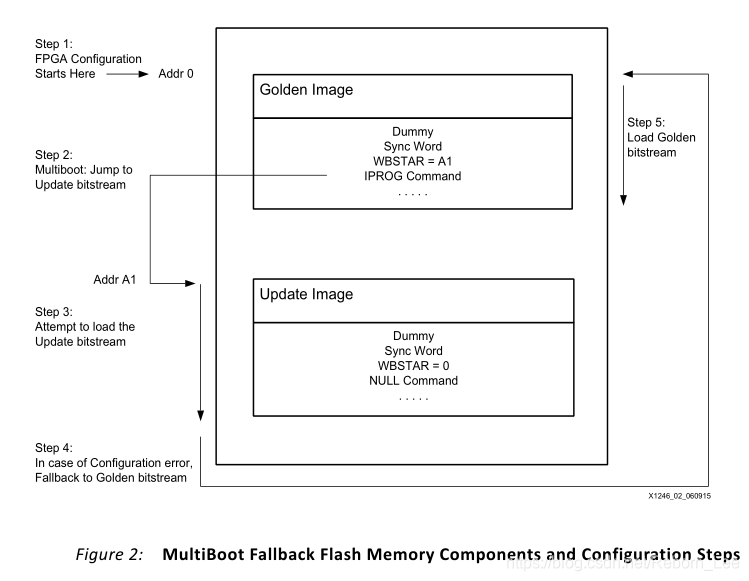

MultiBoot的大致過程如下圖:

MultiBoot的配置文件由兩個比特流文件生成,第一個為備份文件,永遠都不會變,稱為Golden_image,從Flash的0地址存儲。

第二個為更新文件,后面遠程更新,更新的就是這個文件,稱為Update_image,存放在某個地址處,這個地址有熱啟動地址寄存器(WBSTAR)指定。

配置過程大致如下:FPGA從FLASH的0地址處讀取配置,遇到IPROG Command命令時,跳轉到WBSTAR寄存器指定的地址,該地址存放Update_image的地址,此時FPGA嘗試加載該地址處的比特流文件,配置成功的話,就執行該配置的功能。如果遇到配置錯誤,則觸發FallBack,FPGA重新加載Golden_image。

FPGA實現IPROG通常有兩種方式,一種是通過ICAP配置,一種是把相關指令嵌入bit文件中。與通過bit文件實現IPROG相比,通過ICAP更靈活。

在Xilinx FPGA 中ICAP(Internal Configuration Access Port) 指的是內部配置訪問端口,其主要作用是通過內部配置訪問端口(ICAP),用戶可以在FPGA邏輯代碼中直接讀寫FPGA內部配置寄存器(類似SelectMAP),從而實現特定的配置功能,例如Multiboot。

ICAP目前為止有三個版本,包括ICAP,ICAPE2以及ICAPE3。UltraScale系列對應ICAPE3,7系列對應ICAPE2,7系列之前的對應ICAP。

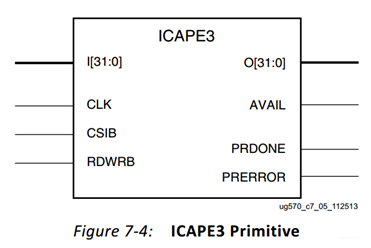

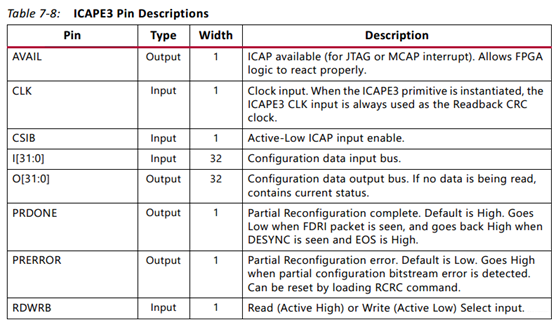

以下以ICAPE3 為例,ICAPE3 的接口如下:

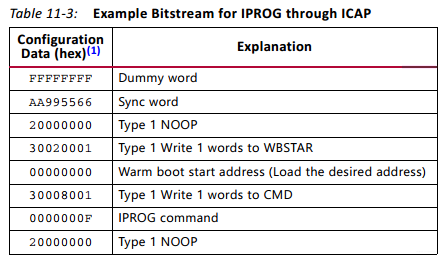

2、IPROG指令

每個UltraScale系列的FPAG包括2個ICAPE3,但實際使用時只能例化并使用一個,默認頂部ICAPE3, 初級玩家采用默認的即可。

IPROG指令的作用跟外部Program_B管腳的作用類似,都是對FPGA芯片進行復位操作,該復位操作對FPGA內部的應用程序進行復位,復位過程中除專用配置管腳和JTAG管腳,其他輸入/輸出管腳均為高阻態,同時IPROG指令不能復位專用重配置邏輯,如WBSTAR寄存器、TIMER寄存器、BSPI寄存器和BOOTSTS寄存器。IPROG指令能夠觸發FPGA開啟初始化流程,同時拉低INIT和Done信號。完成復位操作后,將默認的加載地址用熱啟動地址寄存器(Warm Boot Start Address,WB-STAR)中的新地址替換。

通過ICAP發送IPROG指令實現Multiboot的步驟如下:

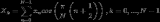

首先寫入同步頭 32’hAA995566, 然后將需要跳轉到的bit文件的起始地址寫入WBSTAR寄存器,最后寫入IPROG(internal PROGRAM_B)指令。

WBSTAR寄存器的格式,根據自己的要為Update_image分配在FLASH的地址,按照下面的格式生成一個32位數據。例如,我為Update_image分配的flash地址為2000000。

(1)對于BPI模式來說,可以通過RS[1:0]來控制具體位流的讀取,也可以通過STAT_ADDR[28:0]地址來控制具體位流的讀取。

(2)對于SPI模式來說,只有STAT_ADDR[23:0]地址來表征FLASH器件的地址,當使用32位地址的SPI(容量大于等于256Mb)時,需要將實際存儲的高24地址賦值給STAT_ADDR[23:0]。因此在位流存儲的起始地址早于255時,這就要求位流中的dummy數目要大于256個,否則就會出現易失部分有效位流讀取,導致加載失敗。為了安全起見,在使用大于等于256Mb的FLASH時,可以適當在位流頭前加入Dummy。

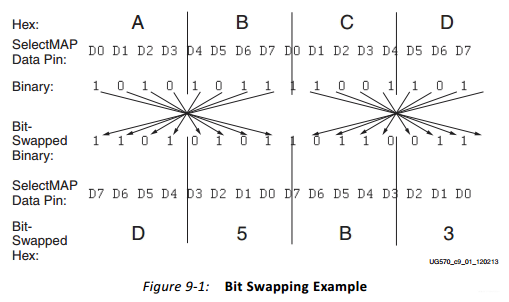

這里需要注意一點,ICAP以及SelectMAP都存在位反轉(Bit Swapping),也就是說,上表中所有的數據需要進行位反轉之后才能接到ICAP的輸入接口,同理,ICAP輸出的值需要進行位反轉后才能與實際的值對應起來,位反轉的示例如下圖。

3、ICAPE3 例化示例

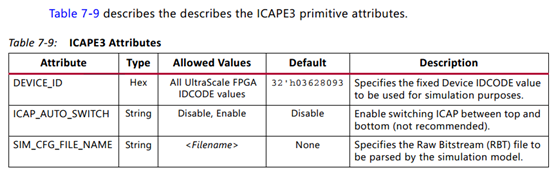

ICAPE3 進行例化,示例如下:

// ICAPE3: Internal Configuration Access Port

// UltraScale

// Xilinx HDL Language Template, version 2019.1

ICAPE3 #(

.DEVICE_ID(32‘h03628093),//pre-programmed Device ID value,used for simulation

// purposes.

.ICAP_AUTO_SWITCH(“DISABLE”),//Enable switch ICAP using sync word

.SIM_CFG_FILE_NAME(“NONE”)//Raw Bitstream (RBT) file,parsed by the simulation

// model

)

ICAPE3_inst (

.AVAIL(AVAIL), // 1-bit output: Availability status of ICAP

.O(O), // 32-bit output: Configuration data output bus

.PRDONE(PRDONE),//1-bit output: Indicates completion of Partial Reconfiguration

.PRERROR(PRERROR),//1-bit output: Indicates Error during Partial Reconfiguration

.CLK(CLK), // 1-bit input: Clock input

.CSIB(CSIB), // 1-bit input: Active-Low ICAP enable

.I(I), // 32-bit input: Configuration data input bus

.RDWRB(RDWRB) // 1-bit input: Read/Write Select input

);

// End of ICAPE3_inst instantiation

其中設備號DEVICE_ID需要查找USER GUIDE手冊,而ICAP原語接口時序跟Select Map接口時序非常相似。SelectMap模式下,FPGA的配置和回讀是通過CSI_B,RDWR_B和CCLK來控制的。

4、程序步驟

在發送IPROG指令之前,將默認的加載地址用熱啟動地址寄存器(Warm Boot Start Address,WB-STAR)中的新地址。

然后對ICAP核進行預配置。重載控制模塊在收到觸發信號后,第一個時鐘周期將ICAP核的RDWRB信號和CSIBCSIB信號置高,第二個周期將RDWRB信號置底,CE信號置高,第三個周期將RDWRB信號置底,CSIB信號也置底。

接著在下面的8個時鐘周期里,將指令隊列中的控制命令逐個發出。

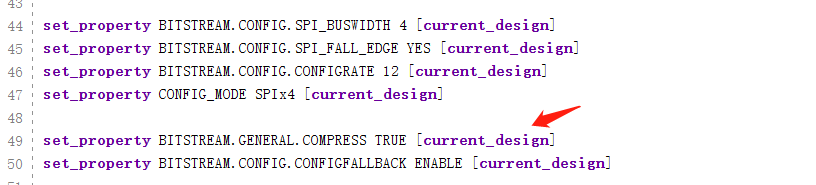

運行工程,生成位流Bit,在約束XDC文件中添加壓縮等命令即可。

固化Mcs生成。Xilinx系列的FPGA需要將后綴名為mcs的內存鏡像文件固化到外部配置存儲器中,FPGA上電后才能自動加載配置文件。一般的mcs文件只包含一個bit流文件,多重啟動的mcs固化文件包含多個bit流文件。在將多個bit流整合到mcs文件的過程中,需要指定每個bit流的起始地址,這樣FPGA專用配置邏輯才能根據地址找到對應的bit流。在程序設計WBSTAR地址時,確定了Golden位流存儲的起始地址為0X00000000,Update位流存儲的起始地址為0X00800000,因此在將Bit整合到Mcs過程中需要指定對應的存儲起始地址,否則就無法加載成功了。

在SPI的flash里燒寫有A和B兩個程序,FPGA上電后,自動加載A程序,根據外部給FPGA指示信號,FPGA自動切換加載B的程序,同時在B程序運行期間,根據外部給FPGA指示信號,FPGA自動切換加載A的程序。

原文標題:FPGA中利用ICAP原語實現Multiboot功能

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603387

原文標題:FPGA中利用ICAP原語實現Multiboot功能

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA 在人工智能中的應用

FPGA在物聯網中的應用前景

如何在FPGA中實現按鍵消抖

FPGA在自動駕駛領域有哪些應用?

FPGA在人工智能中的應用有哪些?

如何在FPGA中實現狀態機

FPGA | Xilinx ISE14.7 LVDS應用

AMD MPSoC器件中啟用SEM IP的策略與方法

在FPGA中如何通過ICAP原語實現Multiboot?

在FPGA中如何通過ICAP原語實現Multiboot?

評論