條件語句的可綜合性

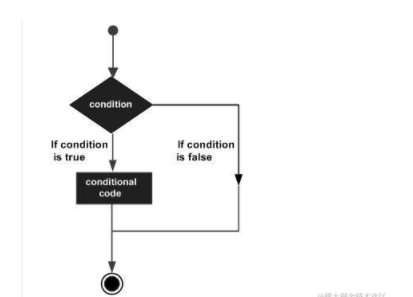

HDL語言的條件語句與算法語言的條件語句,最大的差異在于:

1.不管條件:當前輸入條件沒有對應的描述,則該條件為不管條件(Don’tCare)。對應不管條件的信號稱為不管信號

2.不選條件:多個條件分支中,未獲得當前輸入條件指向的分析,稱為不選條件(Don’tSelect)。對應的信號稱為不選信號。

不管不選發生時,HDL的綜合器,將盡量維持原值,并且得到額外的生成結構。若無法用生成結構維持原值,則直接報錯。根據行為語句的開節點ON/閉節點CN描述;部分條件PC/全部條件FC;以及條件分支的輸出是否具有同名信號(線與WAND)或不同名信號(非線與Not_WAND),綜合器將得到不同的處理結果。

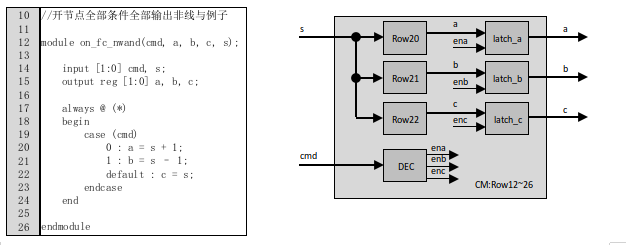

開節點全部條件全部分支非線與描述

此時,全條件描述導致沒有不管條件和不管信號。但全部分支非線與(即每一個條件分支語句輸出不同名信號),將導致不選信號。對于不選條件不選信號,EDA將維持原值。生成結構為鎖存器。

條件譯碼邏輯:

RTL視圖:(QuartusII)

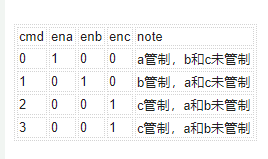

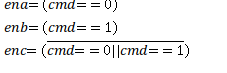

這里的譯碼邏輯為:

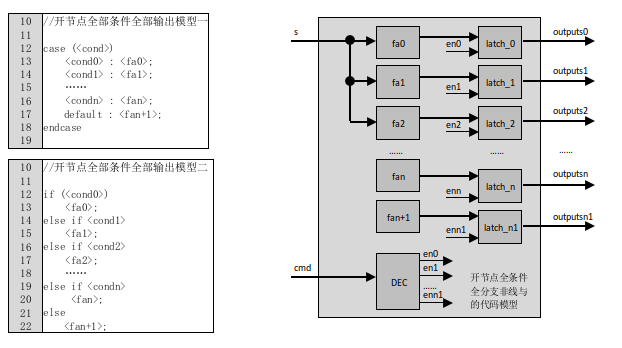

一般性的代碼模型分析:

左側為代碼塊,全條件描述不存在不管條件,全部分支非線與存在不選條件和不選信號,EDA需要為這些不選信號生成鎖存器,用于維持原值。右側為其代碼模型:

結論:開節點全部條件全部輸出非線與的HDL描述,將得到

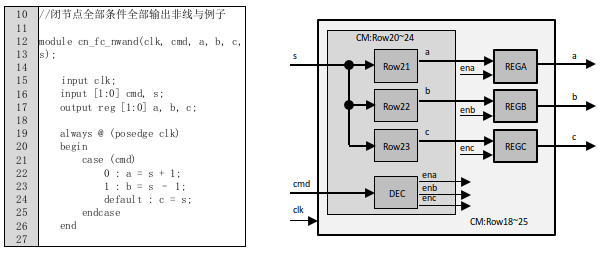

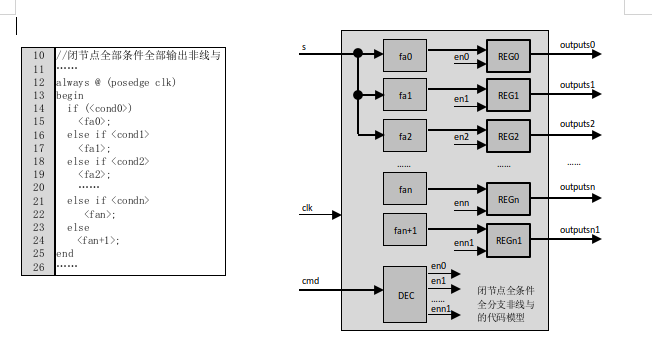

閉節點全部條件全部分支非線與描述

綜合分析:

1.閉節點描述將導致生成寄存器

2.全部條件描述,使得此時不存在不管條件

3.全部分支輸出非線與,將導致不選條件/不選信號。這些不選信號需要維持原值。

4.由于此時已經輸出末端已經得到有記憶的寄存器,因此綜合器此時將使用這些生成寄存器維持原值(不選信號)

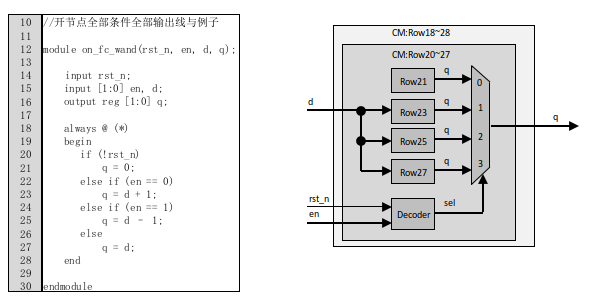

例如:

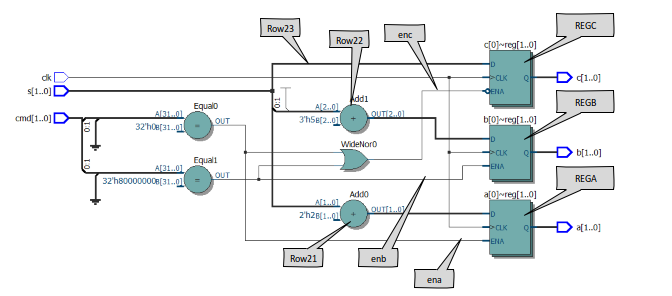

RTL視圖(QuartusII):

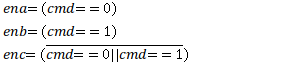

這里譯碼邏輯為:

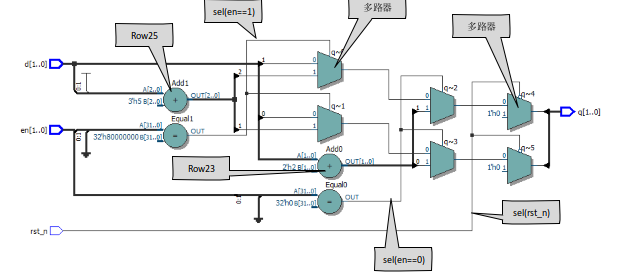

關于使用寄存器維持原值(不選信號/不管信號):

寄存器維持原值需要遵循兩個互相矛盾的綜合原則:

1.優化原則:寄存器使用其使能端維持原值,將導致時鐘信號的路由產生邏輯,或者說時鐘信號被加工,最終導致時鐘偏斜參數的惡化,影響系統的最高速度。因此,綜合器將盡量避免寄存器使用使能端。

2.原創原則:綜合器根據代碼模型分析,和實際的物理實現,必然需要對已經的描述的代碼進行加工和修改,最典型的例子就是生成結構(生成鎖存器,生成寄存器)。但過多的生成結構,將導致最終實現的電路可能與設計者的愿望相悖。因此,綜合器將盡量避免生成結構。

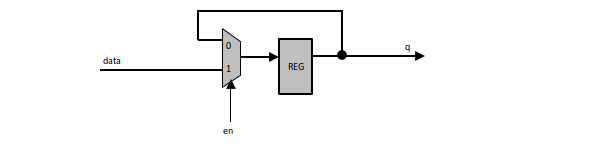

除了使用使能端維持寄存器原值,另一個產生生成結構的方法則是多路器閉環:

一般性的代碼模型分析:

結論:閉節點全部條件全部分支輸出非線與描述,將得到

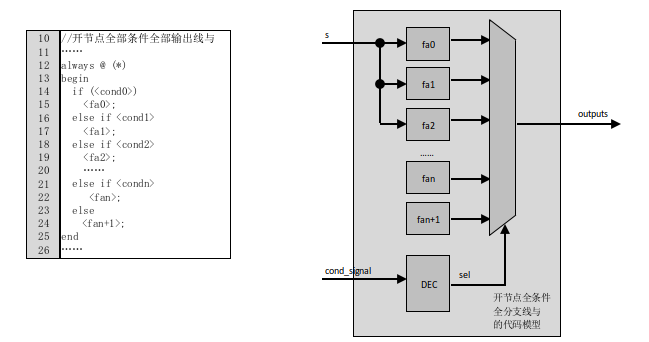

5.3開節點全部條件全部分支線與描述

綜合分析:

1.全部條件避免了不管條件

2.全部分支線與(所以分支輸出同名信號),綜合器為了避免短路,將生產多路器。

注意此時沒有生成鎖存器。

RTL視圖:

一般性代碼模型分析:

結論:開節點全部條件全部輸出線與描述,將得到<多路器輸出>結構。

注意這里沒有鎖存器,雖然有不選信號,但這些不選信號被多路器屏蔽。

編輯:jq

-

寄存器

+關注

關注

31文章

5357瀏覽量

120586 -

HDL

+關注

關注

8文章

327瀏覽量

47407 -

鎖存器

+關注

關注

8文章

906瀏覽量

41542 -

代碼

+關注

關注

30文章

4797瀏覽量

68711

原文標題:FPGA學習:條件語句的可綜合性

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

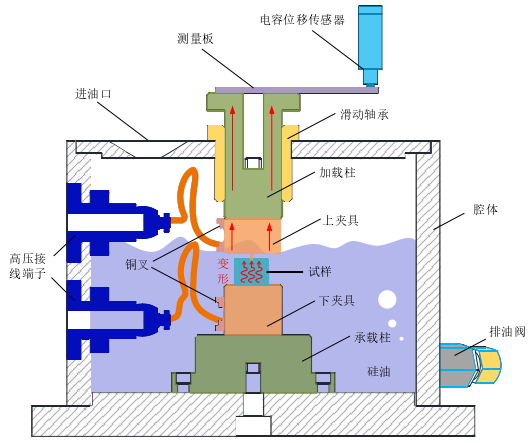

高壓放大器在壓電材料綜合性能測試中的應用

引領電池組綜合性能測試新紀元|比斯特自動化

一次性使用無菌腦積水分流器綜合性測試儀

焊錫膏的綜合性能該如何進行評估?

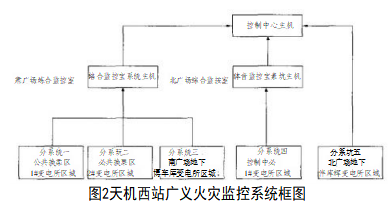

淺談電氣火災監控系統在天津西站綜合交通樞紐中的應用

淺談城市綜合管廊基于物聯網融合通信系統應用分析

淺談綜合管廊監控及安防技術

assign語句和always語句的用法

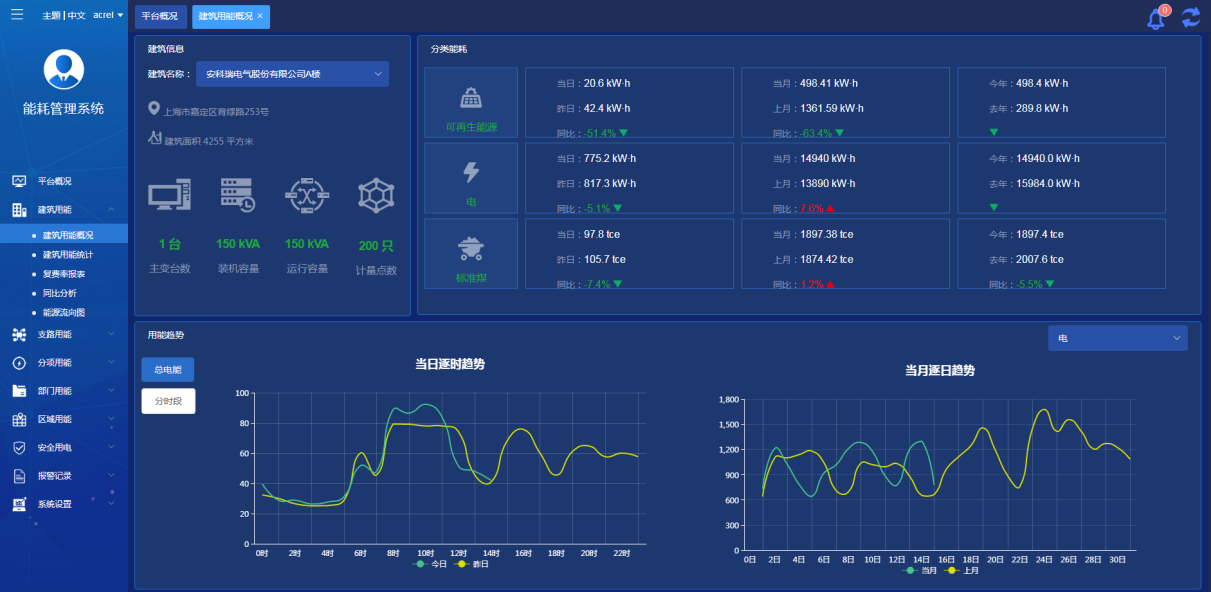

淺談商業綜合建筑能耗分析及節能發展情況

多協議網關BE115是一款多協議轉多上行協議的綜合性轉換網關

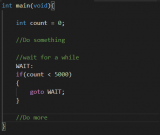

深入探討嵌入式C編程的goto語句

淺談條件語句的可綜合性

淺談條件語句的可綜合性

評論