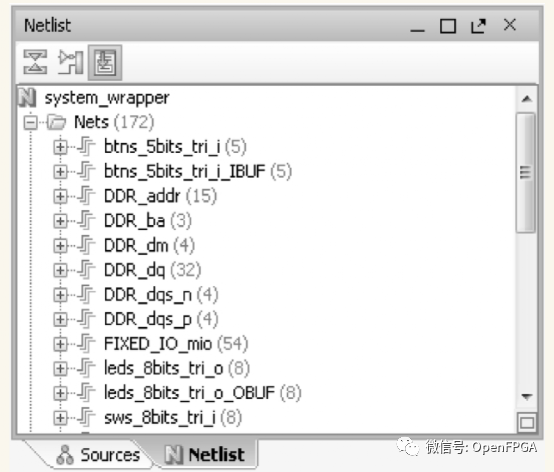

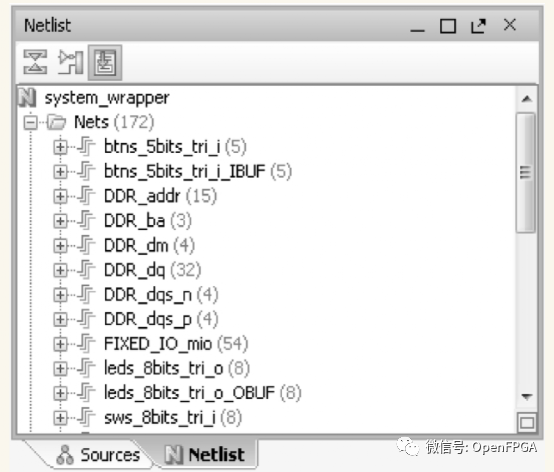

我們都知道FPGA的實現過程分為2步:分析綜合與布局布線后就可以產生目標文件,這兩個步驟中間有個非常重要的文件,那就是-網表。 下圖是Vivado中網表列表示例:

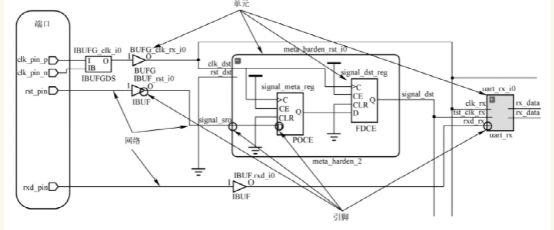

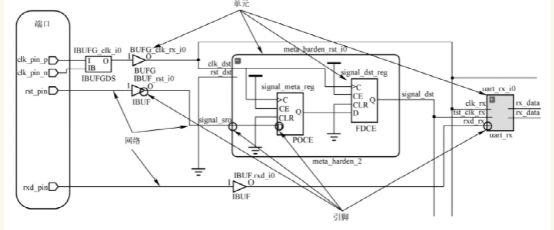

Vivado中網表列表示例 在vivado集成環境中,網表時對設計的描述,如網表由單元(cell)、引腳(pin)、端口(port)和網絡(Net)構成。下圖是一個電路的網表結構:

電路的網表結構

(1)單元是設計單元

1、設計模塊(Verilog HDL)/實體(VHDL)。

2、元件庫中的基本元素(Basic Elements ,BLEs)實例。如LUT、FF、DSP、RAM等。

3、硬件功能的類屬表示。

4、黑盒。

(2)引腳是單元上的連接點

(3)端口是設計的頂層端口

(4)網絡用于實現引腳之間,以及引腳到端口的連接。

編輯:jq

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:【Vivado那些事】Vivado中電路結構的網表描述

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

相關推薦

輸入圖像的內容。 RNN的基本原理 RNN是一種用于處理序列數據的神經網絡,它通過循環結構來處理序列中的每個元素,并保持前一個元素的信息。RNN的主要特點是它能夠處理任意長度的序列,并且能夠捕捉序列中的時間依賴關系。RNN的基本

![的頭像]() 發表于

發表于 11-15 09:58

?311次閱讀

后的約束在之前版本中已存在,那么Vivado會給出警告信息,顯示這些約束會覆蓋之前已有的約束;如果是新增約束,那么就會直接生效。

![的頭像]() 發表于

發表于 10-24 15:08

?378次閱讀

以太網幀(Ethernet Frame)是以太網(Ethernet)協議用于在局域網(LAN)中傳輸數據的基本單位。理解以太網幀的

![的頭像]() 發表于

發表于 10-08 10:00

?1230次閱讀

從綜合角度看,Vivado 2024.1對SystemVerilog和VHDL-2019的一些特性開始支持。先看SystemVerilog。

![的頭像]() 發表于

發表于 09-18 10:34

?979次閱讀

Vivado 2024.1已正式發布,今天我們就來看看新版本帶來了哪些新特性。

![的頭像]() 發表于

發表于 09-18 10:30

?1463次閱讀

生成PCB網表是電路設計過程中的一個重要步驟,它將電路原理圖轉換為PCB布局所需的連接信息。AD(Altium Designer)軟件是一款

![的頭像]() 發表于

發表于 09-02 16:17

?2233次閱讀

時序邏輯電路是數字電路中的一種重要類型,它具有存儲和處理信息的能力。時序邏輯電路的描述方法有很多種,不同的方法適用于不同的設計和分析場景。以

![的頭像]() 發表于

發表于 08-28 11:39

?1560次閱讀

時序邏輯電路是數字電路中的一種重要類型,它具有存儲功能,能夠根據輸入信號和內部狀態的變化來改變其輸出。時序邏輯電路廣泛應用于計算機、通信、控制等領域。本文將介紹時序邏輯

![的頭像]() 發表于

發表于 08-28 11:37

?699次閱讀

鉗形電流表,又稱鉗表,是一種專為電氣線路電流測量設計的計量儀器。其獨特的結構和工作原理使得它能在不斷開電路的情況下,直接測量正在運行的電氣線路的電流大小。本文將從鉗形電流

![的頭像]() 發表于

發表于 05-14 16:14

?3164次閱讀

Verilog與VHDL語法是互通且相互對應的,如何查看二者對同一硬件結構的描述,可以借助EDA工具,如Vivado,打開Vivado后它里面的語言模板后,也可以對比查看Verilog

![的頭像]() 發表于

發表于 04-28 17:47

?2558次閱讀

,用戶可直接在simulink下綜合出網表和約束文件,打包至.dcp文件中,用戶可在vivado下直接加載dcp文件調用模型。

4、直接在viva

發表于 04-17 17:29

由實現組合電路的查找表,實現時序電路的觸發器,以及數據選擇器構成。數據選擇器在存儲單元 M0 的控制下決定直接輸出查找表的值還是輸出 FF 中

發表于 04-03 17:39

以太網的組網結構涉及多個層面和組件。首先,從網絡結構的角度來看,以太網分為物理層、數據鏈路層和高層用戶層。其中,物理層采用特定的通信媒體,如50Ω基帶同軸電纜,實現數據的傳輸。數據鏈路

![的頭像]() 發表于

發表于 03-08 17:19

?3411次閱讀

vivado2017中找不到ZCU102對應的板卡,求解決和分享,應該如何解決

發表于 02-29 17:31

當我使用 DMA 操作時,我需要詳細了解 IDAC 的寄存器,但在相關文檔中找不到這些寄存器的描述,我應該從哪里獲得?

發表于 01-25 06:51

Vivado中電路結構的網表描述

Vivado中電路結構的網表描述

評論