1 引言

PCI,外設組件互連標準(Peripheral Component Interconnection)是一種由Intel公司1991年推出的用于定義局部總線的標準,自規范推出,得到網絡通信,數據采集處理,工業控制等多行業的廣泛應用,并出現PCI-E。CPCI,PXI等多個擴展改良版本。PCI總線支持其即插即用,中斷共享,高速數據傳輸等功能,有著廣闊的市場前景。

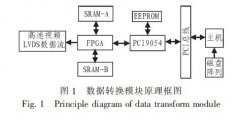

本文介紹了目前使用美國PLX公司生產的協議轉換芯片PCI9054,用verilog HDL在FPGA中產生相應的控制信號.完成對數據的快速讀寫,從而實現了與PCI總線的高速數據通訊。本系統可擴展,適用于其他PCI設備系統,具有實用價值。

2 系統實現

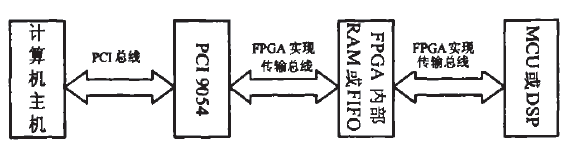

本系統主要由PCI9054與FPGA構成,系統結構圖以及信號連接如圖1所示。可以根據實際需要,利用FPGA的可編程性,實現預定功能,如與單片機,DSP等處理器的不同速率間接高速通信等。協議轉換芯片PCI9054作用就是為本地處理器和主機之間架起一座通信的橋梁。

圖1 系統總體結構

1) PCI9054硬件實現

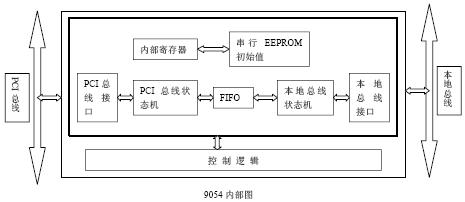

PCI9054是美國PCI公司生產的先進的PCI總線接口芯片,它滿足PCI V2.2協議,支持32位33MHz時鐘PCI總線,特別適用于PCI總線外設產品的開發。PCI9054局部總線有三種工作模式:M模式、C模式和J模式,可方便地與多種微處理器連接。PCI9054的工作方式可利用模式選擇引腳(MODEO,MODE 1)加以選擇。

M模式是專為Motorola公司的MCU設計的工作模式,其主要應用于電信領域。C模式是一種類似于單片機的工作方式,通過片內邏輯控制,將PCI的地址線和數據線分開,很方便地為本地工作時序提供各種工作方式,對于這種工作方式,設計者只需要關注PCI9054的Local端的時序控制時序,就可以很方便的利用PCI9054實現PCI接口電路設計。J模式是地址總線和數據總線沒有分開,嚴格仿效PCI總線的時序,只是為時序控制增加了很多的控制信號。數據傳輸模式有三種:直接主模式,直接主模式就是本地處理器(如伺服控制卡上的DSP)訪問PCI總線上的I/O接口和計算機的內存資源,由本地處理器發起整個數據傳輸。直接從模式,直接從模式就是主機作為主控設備發起對本地總線上資源的訪問.包括對本地處理器的控制和對本地端存儲器的訪問。DMA模式,DMA模式支持PCI總線與本地總線之間的高效突發。

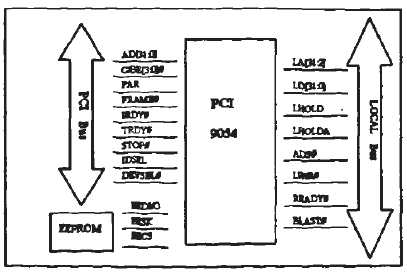

2) PCI9054硬件連接電路(如圖2所示):

圖2 PCI9054硬件連接電路圖

3) PCI9054與PCI插槽信號連接

PCI9054與PCI插槽間的連接信號線,這些信號線包括地址數據復用信號AD[31:0],總線命令信號C/BE[3:0]和PCI協議控制信號PAR,FRAME#,IRDY#,TRDY#,STOP#,IDSEL,DEVSEL#等,電路連接中將彼此對應的信號線連接在一起即可。在PCI總線信號中.除了RST#。INTA#-INTD#之外,其他所有的信號都在始終上升沿被采樣。每個信號都

有相對于時鐘前沿建立和保持時間。在此期間,不允許有信號的跳動。該時間一過,信號的變化就無關緊要了。這種建立和保持時間對于不同的信號其情形是不同的。對于AD[31:0],PAR和IDSEL來說,只有在一定的十種邊沿上才有上述時間的要求。對于LOCK#,IRDY#,TRDY#.FRAME#,DEVSEL#,STOP#,ⅢeQ#,GNT#,SERR#和PERR#這些信號在每個時鐘前沿都有建立和保持時間。對于C/BE[3:0]#在傳輸總線命令是,要在FRAME#第一次建立時對應的時鐘邊沿上遵守建立和保持時間的關系。若傳輸字節使能信號時,要在完成一個地址期或數據期之后的每一個時鐘邊沿保證相應的建立和保持時間。

4) PCI9054與EEPROM接口

各種接口芯片都需要外接串行EEPROM芯片來加載配置數據.對于串行EEPROM芯片,需要根據接口芯片數據手冊中給出的生產廠家及型號選擇。這里選擇FM93LC56。PCI9054提供4個管腳與串行EEPROM相連接,他們分別是EEDI,EEDO,EESK,EECS,對應于FM93LC56的DI,DO,SkCS這四個管腳,這4對管腳直接相連就可以,另外93Lc56的VCC管腳需要接+5V電源,GND接地。因為需要對串行EEPROM進行寫操作,串行EEPROM應處于可編程而且非保護狀態,所以PE接高電平而PRE接低電平。FM93LC56的技術手冊規定兩個管腳上拉和下拉的電阻應為10K左右。

5) PCI9054與LOCAL Bus端連接

LHOLD:申請使用本地總線,輸出信號;LHOLDA:對LHOLD應答,輸入信號;ADS:新的總線訪問有效地址的開始,在總線訪問first clock設置時,輸出信號;BLAST:表示為總線訪問的last transfer,輸出信號;LW/R#:高電平表示讀操作,低電平表示寫操作,輸出信號;LA:地址線;LD:數據線;READY:表示總線上讀數據有效或寫數據完成,用以連接PCI9054等待狀態產生器,輸入信號。

3 VeHiog HDL軟件實現

FPGA內部在PCI9054本地總線LOCAL Bus基礎之上進行設計;FPGA片內RAM或FIFO可以在QUARTUSII環境下利用利用工具MegaWizard Plug_In Manager調用功能模塊生成。單雙口、存儲容量、數據總線的寬度以及同步或異步自行定制。為與MCU或DSP等處理器通信,要設計RAM訪問仲裁模塊。決定某一時刻對RAM訪問的主方;PCI9054支持單周期、突發和DMA傳輸,在FPGA內部要設計本地端總線控制模塊,實現局部總線的狀態控制,同時產生FPGA片內RAM的讀寫時序及地址信號。

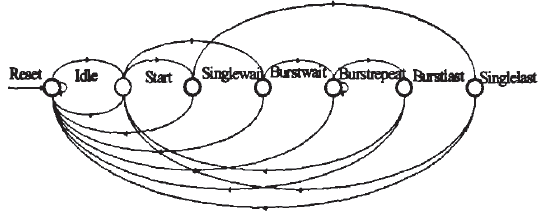

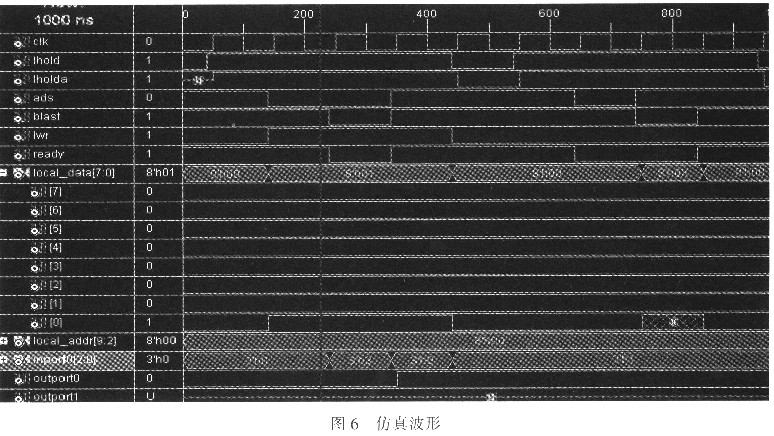

PCI9054支持單周期、突發傳輸和DMA傳輸,因此在狀態機設計中不僅要滿足單周期傳輸的時序。還要兼顧突發和DMA傳輸時序。依據FCl9054的datasheet以及PCI總線協議,其狀態轉換圖如圖3所示:

圖3 PCI9054狀態轉換圖

狀態機是控制單元的主體,接受外部信號以及數據單元產生的信號,產生控制信號序列。狀態機的關鍵是如何把一個實際的時序邏輯關系,抽象成一個時序邏輯函數。根據狀態轉換圖.采用3個always語句.即對應三個進程來完成Moore狀態機。一個用于狀態機的同步時序部分,在本地時鐘clk的上升沿到來時.將nextstate狀態賦給currentstate;個用于描述狀態轉換;另一個用于描述輸出的組合邏輯。在這里重點闡述狀態轉換進程,其Verilog HDL代碼簡略如下所示:

always @ (lads,lblast)

begin case(currentstate)

S0:if(! lads)

nextstate《=S1;

else

nexbtate《=S0;

S1:if(! lblast)

nextstate《=S2;

else

nextstate《=S4;

S2: nextstate《=S3:

S3:if(! lads)

nextstate《=Sl;

else

nextstate《=S0;

S4:nextatate《=S5;

S5:if(blast)

nextstate《=S5;

else

nextstate《=S6;

S6:if(! lads)

nextstate《=S1;

else

nexmmte《=S0;

endcase

end

輸出組合邏輯進程如下所示:

always @(currentstate)

case(currentstate)

SO:begin lready《=1‘b1;

ram_wr《=1’b0:

ram_rd《=1‘b0;

end

。..。..

endcase

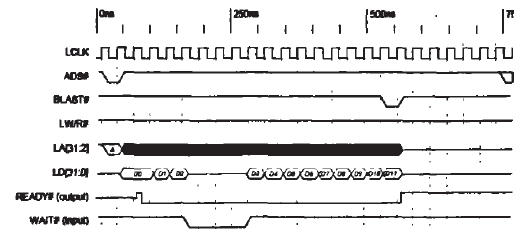

圖4 利用QUARTUSⅡ仿真生成的State Machine圖(可與圖3對應)

圖5 PCI9054 LOCAL Bus單周期傳輸時序圖

4 結論

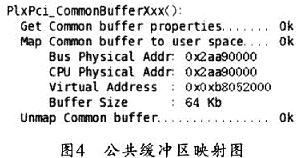

利用DriverStdio開發PCI9054的驅動程序,實現主機對FPGA內部RAM的讀寫,利用示波器檢測ads,blast信號,在8位數據總線的情況下,實現數據傳輸率可以達到26.8Mbyte/s,接近PCI的極限傳輸速率(圖4、5所示)。本設計已經應用,經實際運行,傳輸速度快,數據正確,穩定可靠,經過擴展,同時可應用于其它需要與PCI數據總線接口的設備當中,可縮短PCI設備的開發周期,提高工作效率。

本文創新點:利用PCI9054設計的PCI高速通信接口,采用了FPGA內部RAM間接緩沖技術,可以與DSP,MCU等微處理器高速通信,擴展性強,適用于可應用于其它需要與PCI數據總線接口的設備當中。

責任編輯:gt

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603421 -

芯片

+關注

關注

455文章

50816瀏覽量

423675 -

接口

+關注

關注

33文章

8598瀏覽量

151166

發布評論請先 登錄

相關推薦

PCI總線接口芯片9054及其應用

采用專用接口電路PCI9054實現ARINC429總線接口板設計

基于FPGA和PCI9054的LVDS數據通信卡的設計

基于PCI9054的接口卡

Linux環境下開發PCI9054芯片驅動

基于PCI9054橋路器的數據傳輸的接口邏輯設計

基于PCI9054的數據轉換模塊設計

PCI 總線接口芯片9054及其應用

基于協議轉換芯片PCI9054與FPGA實現PCI通信接口的設計

基于協議轉換芯片PCI9054與FPGA實現PCI通信接口的設計

評論