1 改裝系統簡介

飛機航空電子系統的改裝,就是把功能相對獨立的子系統逐步走向綜合,例如將雷達、慣導、GPS和機載計算機聯合,組成新型航空圖導航系統。通俗點講,就是將那些“傻、大、粗、笨”的儀器儀表,集成為“少而精”的智能儀表,減輕飛行員的操作難度。

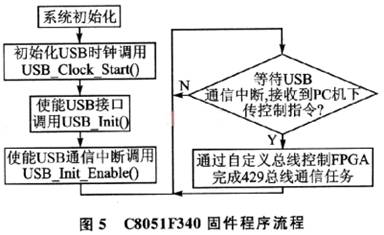

系列多機型改裝時的多功能顯示器,它將原來分散顯示的信息和數據集中在一臺多功能顯示器上。替換掉原來“老死不相往來”的各種導航儀表,不再需要領航員大量記憶枯燥的數據,減少了儀表種類,節省了寶貴的空間,極大減輕了領航員工作強度。圖1中除了地圖視頻采用LVDS外,其它儀表通信都采用ARINC429總線。顯然,解決多通道的ARINC429通信成為本次改裝的瓶頸。

傳統的ARINC429通信設計中,大多采用HARRIS公司的HS3282或Device Engineering公司的DEI1016。但在此則極不經濟,完成多通道429通信,需要多個芯片和更多的布板空間,功耗也線性增加。

特別地,傳統的多通道的429需要更加多的CPU中斷請求線,需要外部復雜的邏輯設計。TS68C429A則是目前解決多通道429通信最為有效的途徑。和傳統的“兩收一發”的芯片相比較,它是“八收三發”,“一片頂四片”。

2 TS68C429A的主要特征

ATMEL公司的TS68C429A是高性能、多通道、低功耗的CMOS型429接口,亦能滿足類似的時分多路串行數據通信。

整個芯片只需單5V工作電源。它具有8路接收、3路發送。所有的接收通道和發送通道都是彼此互獨立,可同時并行工作。8個接收通道之間也是獨立的并行接收,可以直接連接到ARINC429總線,而不需電平轉換。數據字長是標準的32-bit,25-bit的并不支持。

主要特征有如下幾點:

8個獨立的接收通道;3個獨立的發送通道;和所有的TS68K系列的微處理器接口兼容;16-bit數據總線;符合ARINC2429接口,歸零制編碼(Return Zero Code);支持所有的ARINC429數據傳輸率,最高可達2.5Mbit/s,傳統的ARINC429芯片的速率只有2種可選;多標號能力,傳統的芯片要么不檢查標號,要么就接收一個指定的標號;校驗控制(奇校驗、偶校驗、無校驗,中斷能力);RX、TX的數據率可獨立編程;每個發送通道有8個信息單元的FIFO;向量式中斷;可組成菊花鏈中斷;所有的寄存器都是可直接尋址的;具有自測試能力;工作頻率為20MHz;低功耗:400mW。

3 硬件設計

TS68C429A接收和發送通道都成倍增加,但畢竟不是通道的簡單疊加,不是傳統接口的線性擴展,在相關器件選型和設計中需要仔細推敲。

3.1 基本硬件接口

基本硬件接口就是和嵌入式CPU的接口電路。根據ARINC429數據特點,至少要選16-bk數據總線以上的CPU。TS68C429A和所有的TS68K系列的CPU接口兼容,像TS68000、TS68020都可以只需要增加非常簡單的接口邏輯。特別是TS68302完傘可以“無縫連接”。無縫連接就是兩個復雜芯片不需要“粘合邏輯”,對應信號直接相連。

在設計基本電路時需要注意以下幾點:

3.1.1 嵌入式CPU選型。

CPU的數據總線至少應該是16bit的,否則在硬件上要增加字節轉發電路,設計復雜度上升。如果在中斷響應時想迅速判斷中斷源,CPU存中斷響應時應該能夠發出中斷響應(IACK)信號,由TS68C429輸出中斷向量,由CPU回讀后硬件判斷,直接進入對應中斷服務例程,節省軟件響應時間。除TS68K系列外,符合這個要求的還有最廣泛使用在PC機上的X86系列,如Inte180486等。顯然,TS68C429的中斷響應機制,完全類似X86系列中的8259 中斷控制器時序,可以直接無縫連接。值得指出的是,X86系列的中斷請求是高有效,中斷請求信號需要反相。

3.1.2 時鐘

傳統的ARINC429芯片只有一個時鐘,人多數是1MHz,用以控制收發速率。速率有2種選擇,即速率是時鐘的十分之一或八十分之一,亦即100K或12.5K。在這里,TS68C429需要2種時鐘,系統時鐘和ARINC429收發時鐘。系統時鐘CLKSYS用來控制CPU接口時序,應該和CPU時鐘相同,在這里直接使用TS68302的輸出時鐘CLK0。在使用其它型號的CPU時,CLKSYS可以直接和CPU時鐘連接在一起。CLK429使用了定時器輸出TOUT1,用來決定429串行數據傳輸速率。存使用其它型號的CPU時,也可以設計一個獨立的時鐘做CLK429。

3.1.3 高、低字節訪問

處理器對TS68C429每次訪問都應該是16Bit的,除了這里和TS68302的無縫連接,還可以把高字節選通信號(/UDS)和低字節選通信號(/LDS)一起直接接地。CPU一般足字節編址的,所以應該足A9…A1對應TS68C429的A8…A0。

3.1.4 存儲器周期

無論是讀周期還是寫周期,TS68C429都要用/DTACK應答CPU。TS68K系列中的/DTACK,即數據傳輸周期應答(Data Transfer Acknowledge),本質上就是許多CPU的READY信號。如果使用別的型號CPU,READY屬于高有效,需要對/DTACK進行反相。

3.2 中斷菊花鏈電路

對于大多數應用來講,一片TS68C429基本可以滿足多通道429通信要求。當要求更多通道時,TS68C429A可以采用菊花鏈的彤式設計。

菊花鏈(Daisy Chain)是一種阻塞式級聯結構,排在前面的優先級高于其后的所有單元。在任一時刻,高優先級若果發出中斷,就禁止了比它自身優先級低的中斷。共有U1、U2…Un個單元,其中U1具有最高優先級,Un優先級最低。當某一單元需要發出中斷時,首先要判斷前面是否有高優先級的中斷,即判斷傳遞下來的中斷使能信號/IEIxx,當其為低電平時,可以發出,當其為高電平時禁止發出。禁止中斷發出時,要一直等待到前面中斷響應完成后再發出。最極端的情況就是,某些低優先級的中斷單元永遠沒有機會發出中斷,設計菊花鏈電路時,要綜合平衡各通道的數據流量。

4 軟件設計

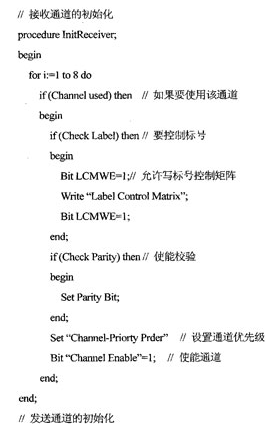

上電復位后,軟件應在正式工作前初始化TS68C429。傳統的芯片只需要要寫一次控制寄存器,但多通道的初始化要復雜一些。

4.1 寄存器映像

在傳統的ARINC429只有一個控制寄存器,由于通道少,每個通道分配專用的選通信號,硬件簡單譯碼即可。在多通道的芯片中,不可能繼續采用這種辦法。整個芯片只有一個總的片選(/CS),然后由地址A8..A0來尋址片內寄存器。系統的初始化,本質就是正確配置這些寄存器。

8個接收通道,每個都有自己的4類專用寄存器區。

4.1.1 接收控制寄存器(receive control register)

這是一個可讀可寫的寄存器,它控制本通道的中斷優先級、校驗、標號、測試模式以及通道使能等配置。如果有2個通道的中斷優先級相同,就有一個永遠發不出中斷。如果設置本通道處于測試模式,則第三發送通道的數據在內部回環到本通道。這個特征是用來做通道自檢的。

4.1.2 間隙寄存器(gap register)

間隙寄存器是一個只寫寄存器。寫入值是以CLK429時鐘周期為單位的計數值,實際是定義了相鄰兩個429數據的最小間隙。在傳統的芯片中,最小間隙是固定的。在這里,必須顯式地設置這個寄存器,決不能隱含使用復位缺省值。

4.1.3 數據緩沖區(message buffer)

數據緩沖區是2個16bit的只讀寄存器,存放接收到的ARINCA29數據。采用中斷接收時,主要就是讀這2個寄存器。高16bit(most significant word,MSW)存放在低地址,低16bit(least significant word,LSW)存放在高地址。讀數據時先讀MSW,再讀LSW。

4.1.4 標號控制矩陣(label Control matrix)

這是一個256×1bit的存儲器區。許多人不理解這個區的含義,不會配置,以致系統不能正確運行。眾所周知,ARINC429規范的低8bit屬于標號區(label),標號代表了數據類型,例如72H代表高度數據,73H代表角速度等。這樣總計有256個標號。標號控制矩陣的某地址設置為“1”,就允許該通道接收對應標號的數據,清除為“0”,就禁止該標號的數據。硬件復位之后全部清“0”,也就是禁止接收一切數據,這就是系統不運行的原因。

3個發送通道,每個都有自己的3個專用寄存器。

4.1.5 頻率寄存器(Frequency Register)

這是一個只寫的寄存器,寫入值是發送速率的除數因子。

發送速率=CLK429/FR除數因子

根據這個公式,用戶可設定選擇的速率。傳統的ARINC429沒有這個功能,只有2種固定的速率。

4.1.6 發送控制寄存器(Transmitter Control Register)

和接收控制寄存器類似,這是一個可讀可寫的寄存器,它控制本通道的中斷優先級、校驗、是否作為測試模式的發送、以及通道使能等配置。其中的發送間隙是控制連續發送的兩個32bit的AKINC429信息之間最小間隙,防止接收方覆蓋溢出。

4.1.7 發送FIFO

FIFO,即“先進先出”(First In First Out),基本元素可以認為是2個16bit的寄存器。軟件必須先寫入MSW,再寫入LSW,這和接收通道順序是一致的。FIFO深度為8個ARINC429信息。存寫入之前,必須驗證FIFO未滿,否則寫入數據被丟棄。在FIFO只要滿隊列的FIFO發送了一個元素,此時FIFO雖然未空,但也未滿,就可以寫入后一個數據。

除了接收通道和發送通道的專用寄存器,還有兒個通用的寄存器,如通道狀態寄存器、中斷屏蔽寄存器,中斷向量基址寄存器等,不再贅述。

4.2 復位初始化

上電復位之后,所有寄存器清“0”,各通道處于禁止狀態,需要軟件顯式初始化。下面給出接收通道和發送通道的初始化流程。

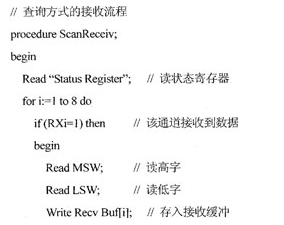

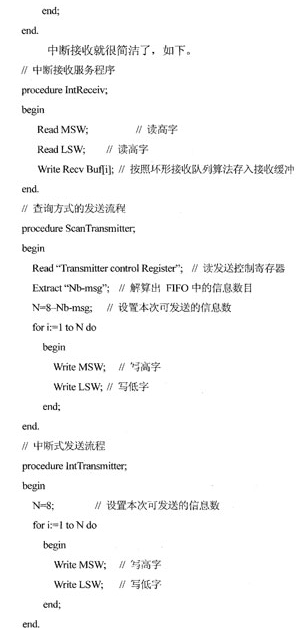

4.3 ARINC429數據的接收與發送

系統工作后,初始化的通道就可以接收發送了。一般的,因為不可預測接收數據何時到達,正式工作后接收采用中斷驅動,發送采用查詢,這樣既可以不丟失數據,又可以掌控發送節奏。查詢接收的辦法,一股使崩在系統初期硬件調試階段。在上篇文章中,介紹了中斷采用環形接收隊列,這個方法非常有效。在此不再贅述環形隊列訪問算法。下而給出查詢/中斷收發流程。

TS68C429集成度高,是改裝原來分散的ARINC429設備的一種合理有效的選擇。我們已將上述設計應用在多個不同種類的航空電子系統中,證明是十分有效的。隨著航空電子系統的更新換代,TS68C429的應用將更加廣泛。

責任編輯:gt

-

CMOS

+關注

關注

58文章

5718瀏覽量

235516 -

顯示器

+關注

關注

21文章

4979瀏覽量

139991 -

接口

+關注

關注

33文章

8601瀏覽量

151168

發布評論請先 登錄

相關推薦

基于USB的ARINC429總線接口模塊設計

基于PC/104設計與實現ARINC429接口模塊

怎么設計便攜式ARINC429總線通信設備?

基于DSP的ARINC429通信板設計

航空用ARINC429總線收發系統設計與實現

基于USB的ARINC429總線接口模塊設計

基于HI-8582的ARINC429總線設計

USB的便攜式ARINC429總線通信設備技術

PCI總線ARINC429通信卡實現方法

一種PCI總線ARINC429通信卡實現方法

如何使用FPGA實現ARINC429接口和總線數據接收

arinc429模塊卡

基于CMOS型429接口TS68C429A實現ARINC429通信的應用設計

基于CMOS型429接口TS68C429A實現ARINC429通信的應用設計

評論