傳統電信網絡是個同步網絡,電信局間和各局內部都要保持同步狀態。因此必須有一個同步分配系統來保證經過線路傳輸的信號仍然可以保持原始的同步關系。在一個 PDH網絡中,從T1或E1線路上恢復出時鐘信號,同步供給單元(SSU)或樓宇綜合定時供給(BITS)是網絡同步中常用的一種方式,它主要是由主時鐘為同步網絡中的下一級設備提供時鐘。BITS主要用于北美地區,在其他地方主要使用SSU。本文利用Dallas Semiconductor公司的DS26502為BITS/SSU應用或者使用T1/E1傳送定時信息的系統提供一個完整的前端解決方案。

網絡同步的基本概念

目前絕大多數電信網絡都是同步網絡,無論是2G的GSM、3G的CDMA還是目前熱門的WiMAX網絡,它們的運營和發展都必須首先解決同步問題。同步是指信號之間的頻率或相位保持某種特定關系,即在相對應的有效時刻內以同一速率出現。對一個電信網絡的所有時鐘進行同步,是為了確保發送和接收節點以同樣的速率對數據進行采樣,防止數據傳輸丟失。一個公用電話交換網絡(PSTN)能夠正常工作需要同時實現比特同步、幀同步和網同步。

網絡的同步以時鐘分層結構為基礎,如圖1所示。頂層是主參考時鐘(PRC)或主參考源(PRS),時鐘精度最高,可以達到10-11。 PRC/PRS可以通過一個銫原子鐘產生,或者通過GPS、GLONASS接收。接下來一層為同步供給單元(SSU)或樓宇綜合定時供給(BITS)。 SSU/BITS具有保持性能,當它失去與PRC/PRS的同步后,可以產生一個短時間內精度高于其固有自由振蕩精度的時鐘。SSU/BITS通常采用由銣時鐘驅動的數字鎖相環(DPLL)來實現,可以是只具有時鐘功能而不進行數據傳輸的獨立產品。第三層是SDH設備時鐘(SEC)或SONET最小時鐘 (SMC)。SEC/SMC也具有保持性能,但其保持和自由振蕩精度性能低于對SSU/BITS的要求。SEC/SMC通常采用由恒溫晶體振蕩器 (OCXO)或溫度控制晶體振蕩器(TCXO)驅動的DPLL來實現,可以是網絡產品的一部分或某塊單板。分層結構中的第二層及以下各層,只要其到 PRC/PRS的路徑不中斷,就可以擁有與PRC/PRS相同的時鐘精度。

圖1 網絡同步時鐘分層結構

目前有兩個主要的標準組織負責制定網絡時鐘要求,Telcordia發布的GR-XXX-CORE主要面向北美地區,而ITU則通過ITU-T G.XXX系列文檔面向全球其他地區。中國已建成的數字同步是建立在PDH環境下,即利用PDH電路傳遞定時信號。隨著傳輸網由PDH向SDH的發展,傳輸所又制定了《SDH網傳送同步網定時的方法》。中國采用2048kb/s和2048kHz兩種信號,做為同步網標準的接口信號。2048kHz信號符合 G.703建議,而2048kb/s則同時符合G.703和G.704建議。

DS26502的基本功能

在早期利用PDH傳送同步時鐘時,由于沒有專用的時鐘恢復器件,通常的做法是利用集成成幀器(FRAMER)的單片T1/E1收發器,例如 DS2155的線路恢復時鐘RCLK,來做為同步的接收。采用這種方案可以完成同步時鐘的傳送,但是它同樣存在一些缺點,因為單片收發器不是專用時鐘恢復芯片,所以首先會有很多管腳閑置,導致資源浪費,設計復雜,在一些無關的處理上造成不必要的功率消耗。此外,在時鐘配置方面由于沒有特別的處理,因此無法實現ANSI/ITU-T關于同步時鐘信號的某些特殊要求。

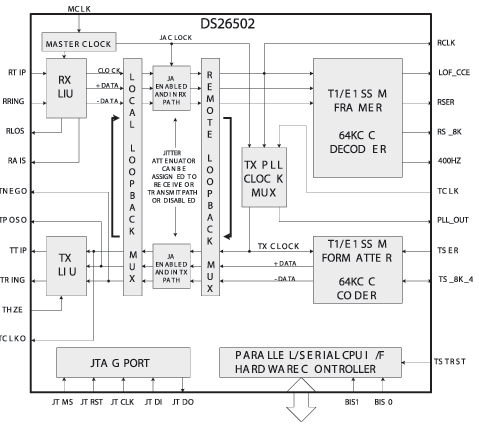

DS26502是Dallas Semiconductor公司推出的SSU/BITS專用時鐘恢復器件,系統結構如圖2所示。它的接收端可以從T1、E1、64kHz復合時鐘 (64KCC)和6312kHz同步定時接口恢復出時鐘,在T1和E1模式下,還能恢復同步狀態消息(SSM)。發送部分可以直接連接到T1、E1或 64KCC復合時鐘同步接口,在T1和E1模式下也能夠提供SSM。在DS26502支持的輸入和輸出同步時鐘頻率內,它能夠實現頻率的任意轉換。另外, DS26502還具有單獨的輸出,用來提供6312kHz時鐘信號。

圖2 DS26502的系統結構

在物理特性方面,DS26502可以通過軟件設置,同時支持長距和短距,無須更改硬件就可以匹配75/100/110/120等不同線路接口;在進行冗余設計時,為了方便進行保護切換,通過器件引腳可以實現發送端輸出的快速關斷;芯片內部的抖動衰減器既可以放在發送側也可以放在接收側,并且具有旁路模式;當線路出現LOS、AIS和LOF等狀態時,有硬件管腳輸出指示,通過連接LED燈可以方便查找發現問題;控制方式多樣,可以通過并行、串行或者硬件控制器端口進行讀寫,采用8位并行控制端口時可以選取Intel或Motorola兩種總線模式,串行方式時采用通用的SPI接口。在協議方面, DS26502符合ANSI關于T1和ITU-T關于E1的所有指標,符合G.703 2048kHz同步接口和64kHz中心化(選項A)和同向定時接口,符合G.703附錄II中64kHz和6312kHz日本同步接口。

DS26502的應用

DS26502有兩種主要的工作模式:軟件模式和硬件模式,它們主要的區別是器件的控制方式不同。軟件模式時,微控制器使用串行或并行總線與圖2中 DS26502內部的控制寄存器連接,由這個外部控制器對DS26502進行初始化、數據讀寫等操作;在硬件模式中,原來的串行或并行通信接口引腳被重新賦予功能,通過這些引腳新的邏輯定義,就能在沒有外圍處理器的情況下直接控制DS26502的內部工作。這是硬件模式的優點之一。實際設計中,是否采用硬件模式要取決于具體應用的特殊要求。設計當中需要重點考慮目標應用是否會用到一些只能在軟件模式下使用的功能,這也是采用硬件模式的一個局限性,有些功能在此模式下無法使用,或者有些功能無法像軟件模式那樣進行設置,比如軟件復位、中斷屏蔽以及狀 態寄存器的讀寫等都無法進行。

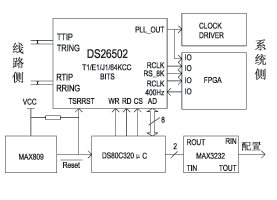

為了充分利用DS26502的特性,在設計中采用軟件方式進行設計,如圖3所示。選取高速八位單片機DS80C320作為主控制器,整板采用MAX809來做復位控制。

圖3 DS26502的應用框圖

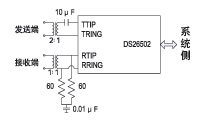

DS26502的線路側設計與標準T1/E1電路設計完全相同,圖4為接口電路。它的LIU接口可以在T1/E1/64KCC/6312kHz網絡間通過軟件切換,無須改動外部設計。這里的64kcc是指符合 G.703的64kHz同步接口,此時64kHz時鐘信號通過編碼內含8kHz和400Hz兩個頻率。LIU的發送和接收完全獨立,這意味著發送端可以與 T1(E1)電路相連,而接收端采用E1(T1)模式。需要注意的是,在G.703規范中關于如何進行6312kHz的脈沖成形并沒有明確規定,所以 6312kHz和其他模式略有不同。接收時,6312kHz與其他模式相同,通過RTIP和RRING進行接收,但發送時它只是TCLKO管腳輸出的一個 0~3.3V的信號,并不通過TTIP和TRING送到線路上輸出,需要由外部濾波器來實現6312kHz的正弦波形。

圖4 DS26502的接口電路

當線路接口需要連接到一個監測端口時,由于E1/T1線路端接電阻和監測端口的隔離電阻分壓的關系,此時線路中存在阻性衰減,所以需要E1/T1接收線路能夠提供不同的接收增益。DS26502針對這種應用,可以提供接收側的監控應用模式,通過設置MM0和MM1兩個寄存器,DS26502可以提供最高32dB的接收增益,補償分壓后信號幅值降低的問題。需要注意的是,這種純阻性的損耗和增益與E1/T1傳輸線路上的電纜損耗特性不同。

DS26502的輸出端就是需要從線路中提取的2M同步時鐘。這個時鐘一路送入FPGA進行處理,這樣可以提高靈活性,方便改變單板的管腳配置,另一路送入時鐘驅動器供本板其他器件使用。DS26502除了可以從線路中提取時鐘外,也可以接收ITU G.703第10部分中規定的2.048MHz的同步方波時鐘。

同步狀態信息SSM(Synchronization Status Message)用于在同步定時鏈路中傳遞定時信號的質量等級,使得SDH網和同步網中的節點時鐘通過對SSM的解讀獲取上游時鐘的信息,對本節點的時鐘進行相應操作(例如跟蹤、倒換或轉入保持),并將該節點同步信息傳遞給下游。它采用4bit編碼,共16種信號,反映不同的質量等級。由于2Mb/s信號傳輸距離長,又有同步狀態信息(SSM)功能,因此在同步網絡中優先采用2Mb/s信號。DS26502可以在T1和E1模式下方便的提取插入SSM信息,同時它支持2Mb/s信號。在E1電路中,Sa位用來發送和接收同步狀態信息,最基本的Sa/Si位讀取方式可以基于CRC4多幀方式,也可以基于雙幀方式,通過DS26502的軟件接口,可以讀寫到接收和發送的Sa/Si位。在T1模式下,DS26502通過BOC控制器直接讀寫同步狀態信息。

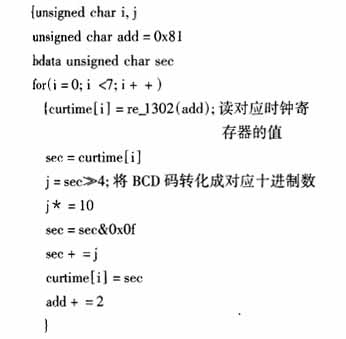

軟件流程

圖3單板的系統初始化和配置如下:DS26502在上電后會馬上自動復位,清除所有可寫的寄存器空間,等待復位完成后,可以通過查詢寄存器檢測器件的ID號。上電復位后LIRST(LIC2.6)寄存器需要從0置為1,來對線路接口電路進行復位,這將初始化時鐘恢復電路的狀態機,對抖動衰減器重新進行中心定位,這一過程大概需要40ms。除了上電復位外,單板可以在任何時候通過拉低TSTRST管腳硬件復位,或者通過模式寄存器中的SFTRST位軟件復位,復位過程 中所有操作將會中斷。復位完成后,系統開始配置時鐘,容許時鐘系統適當調節后,開始對寄存器空間初始化,包括寄存器保留位的寫入。因為復位后系統默認關閉所有中斷,所以需要對中斷控制寄存器中特定的位寫1來打開相應的中斷,因此按照具體應用初始化中斷寄存器,打開不同的中斷位,此時系統就可以正常工作,等待處理中斷和鎖定的各種狀態信息。當出現中斷時,系統首先讀取中斷信息寄存器來判斷是哪個狀態寄存器產生了中斷,然后通過檢查這個狀態寄存器來最終確定真正的中斷源。

結論

本文針對目前同步網絡的現狀,采用BITS接口芯片DS26502設計了一個前端接口電路,實現了ANSI/ITU-T等標準組織關于網絡時鐘的各種要求。

責任編輯:gt

-

芯片

+關注

關注

456文章

50889瀏覽量

424303 -

收發器

+關注

關注

10文章

3435瀏覽量

106047 -

振蕩器

+關注

關注

28文章

3833瀏覽量

139140

發布評論請先 登錄

相關推薦

基于DS3231的高精度時鐘接口設計

DS26504 pdf datasheet(時鐘恢復器件芯片

DS26502的硬件控制模式

DS2155 and DS26502 Software Co

基于FPGA的高速時鐘數據恢復電路的實現

時鐘芯片接口分析與DS1302典型原理電路圖

ds1302是什么接口,DS1302時鐘芯片接口分析詳解

DS26502LN+ - (Maxim Integrated) - 時鐘/計時 - 專用

DS26502L+ - (Maxim Integrated) - 時鐘/計時 - 專用

基于DS26502時鐘恢復芯片實現前端接口電路的應用設計

基于DS26502時鐘恢復芯片實現前端接口電路的應用設計

評論