學習內容

學習關于AXI總線的信號接口的具體要求(包括不同通道之間的關系,握手機制說明等)和AXI4-Lite的相關信息,在文章后半部分對AXI讀寫時序進行了簡要講解,主要針對ARM公司的IHI0022D進行閱讀總結。

Clock and Reset

前面也提到了信號和復位的功能,這里對AXI全局時鐘(ACLK)和復位信號(ARESETn)做進一步的解釋說明。Clock: 每個AXI組件都要使用時鐘信號(ACLK)。

所有的輸入信號都在ACLK的上升沿上采樣。

所有輸出信號的變化必須發生在ACLK上升沿之后。

在主機接口和從機接口上,輸入和輸出信號之間不能有組合路徑。

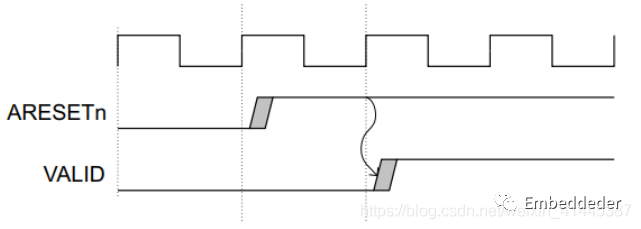

Reset: AXI使用一個單獨的低復位信號(ARESETn)。復位信號可以進行異步復位,但是復位完必須與ACLK的上升沿同步。在復位過程中,要求:

主機接口必須驅動ARVALID、AWVALID、和WVALID為低電平。

從機接口必須驅動RVALID和BVALD 為低電平。

所有其他信號可以為任何值。

在完成復位后,允許master驅動ARVALID,、AWVALID、WVALID為高。但是上升沿信號是在ARESETn是拉高之后而且要在ACLK上升沿。如下圖:

Basic read and write transactions

在基本的讀寫傳輸中,要完成正常的傳輸功能要進行握手并且遵守協議中對每個通道的信號的要求。

握手機制

所有五個通道都使用相同的VALID/READY握手處理來傳輸地址、數據和控制信息。這種雙向握手機制表示主機和從機都可以控制信息在主機和從機之間傳輸的速率。

源端(master)生成VALID信號來指示地址、數據或控制信息何時傳輸可用。目的端(slave)生成READY信號來表示它可以接受該信息。傳輸只發生在VALID和READY信號都為高電平時。 在主機接口和從機接口上,輸入和輸出信號之間不能有組合路徑。

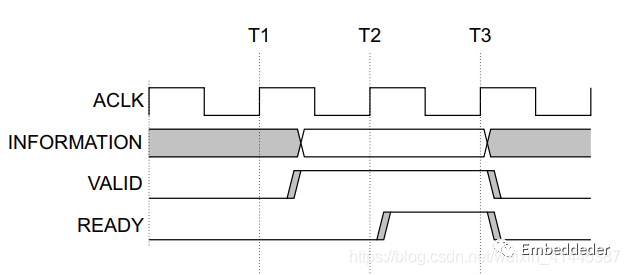

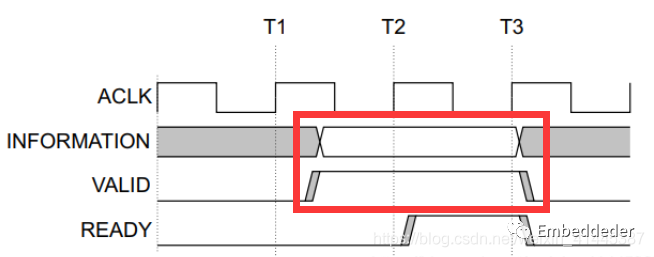

雙向握手協議表示主機和從機都可以控制信息在主機和從機之間傳輸的速率。換句話說也就是在傳輸中VALID和READY,都可以進行等待對方從而完成數據傳輸。如下圖所示,下圖的VALID的上升沿在T1時刻之后完成拉高,在T2時刻VALID信號為高,而READY信號為低,所以要繼續等待READY信號拉高。在T2時刻的上升沿之后,READY拉高,在T3時刻上升沿時,READY和VALID信號都為高,所以數據傳輸發生。也就是下圖的數據傳輸發生在T3時刻。

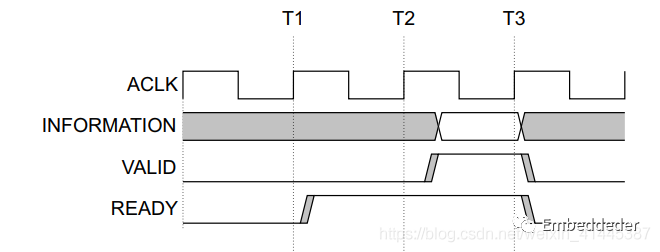

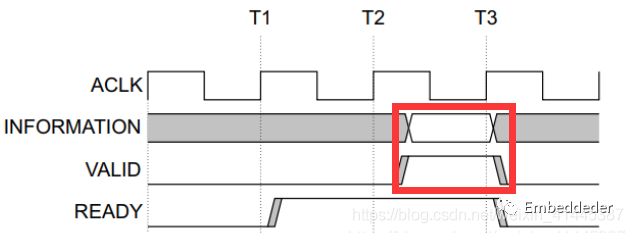

下圖的分析方法同上,在T1時刻READY和VALID信號都為低,不進行數據傳輸;在T2時刻READY和VALID信號分別為高、低,不進行數據傳輸;在T3時刻READY和VALID信號都為高,進行數據傳輸。

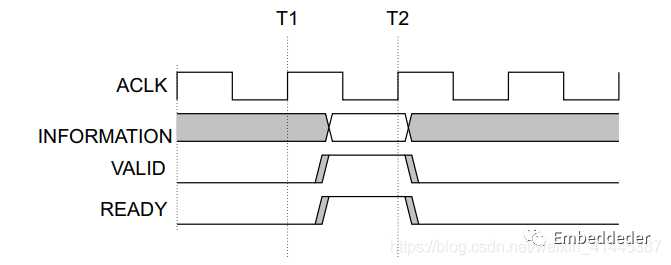

并且,READY和VALID可以同時設置為高進行數據傳輸,如下圖,在T2時刻發生數據傳輸。

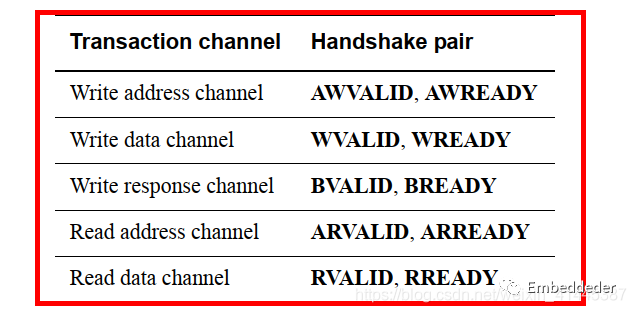

針對不同的信號通道,握手信號加上不同的前綴加以區分,如下表:

對于不同通道的握手信號,AXI協議有具體的建議要求:Write address channel主機可以在地址和控制信息都有效的時候拉高 AWVALID。當AWVALID拉高后要保持不變,直到AWREADY也拉高并且時鐘產生上升沿之后。換句話說,在握手傳輸的時,我們的數據信息和地址信息要保持不變,這樣才能確保傳輸的數據為有效可靠的。也就是AWVALID和信息數據是同步變化的。下面給出兩個示例:

AWREADY的默認狀態可以是高或者低。AXI協議建議的默認狀態為高。當AWREADY為高時,從機能夠接受任何提供給它的有效地址。不建議默認AWREADY狀態為低,因為它強制進行握手傳輸,至少需要兩個時鐘周期,一個周期拉高AWVALID,另一個周期拉高AWREADY。

Read address channel和上面的寫地址通道要求類似,主機可以在地址和控制信息都有效的時候拉高 AWVALID。當AWVALID拉高后要保持不變,直到AWREADY也拉高并且時鐘產生上升沿之后。WREADY的默認狀態可以是高或者低。AXI協議建議的默認狀態為高。當AWREADY為高時,從機能夠接受任何提供給它的有效地址。不建議默認AWREADY狀態為低,因為它強制進行握手傳輸,至少需要兩個時鐘周期,一個周期拉高AWVALID,另一個周期拉高AWREADY。

Write response channel當它驅動有效的寫響應時,從機才能拉高BVALID信號。當BVALID拉高后要保持不變,直到BREADY也拉高并且時鐘產生上升沿之后。BREADY的默認狀態可以是高電平,但前提是在主機總是能夠在一個周期內接受寫響應的情況下。

Write data channel:在寫突發傳輸期間,當主機驅動有效的寫數據時,才需要拉高WVALID信號。當WVALID拉高后要保持不變,直到WREADY也拉高并且時鐘產生上升沿之后。WREADY的默認狀態可以是高電平,但前提是從機總是能在一個周期內接受寫數據。當主機在突發傳輸中進行最后一個數據傳輸時,必須拉高WLAST信號,用于指示傳輸結束。

Read data channel:當它驅動有效的讀數據時,從機才能拉高RVALID信號。當RVALID拉高后要保持不變,直到RREADY也拉高并且時鐘產生上升沿之后。即使從機只有一個讀數據信息,它也必須在響應數據請求時拉高RVALID信號。主機接口使用RREADY信號來表示它接受數據狀態。RREADY的默認狀態可以為高電位,但前提是無論何時啟動讀操作,主機都能立即接受讀數據。當從機在突發傳輸中進行最后一個數據傳輸時,必須拉高RLAST信號,用于指示傳輸結束。

通道之間的關系

AXI協議中需要保持以下關系:

在寫操作中,寫響應必須始終跟隨它是其中一部分的最后一個寫傳輸。

讀取數據必須始終跟在與數據相關的地址后面。

通道握手必須符合在通道握手信號之間的依賴關系。

通道握手信號之間的依賴關系

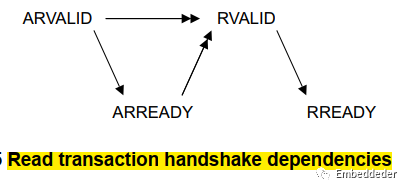

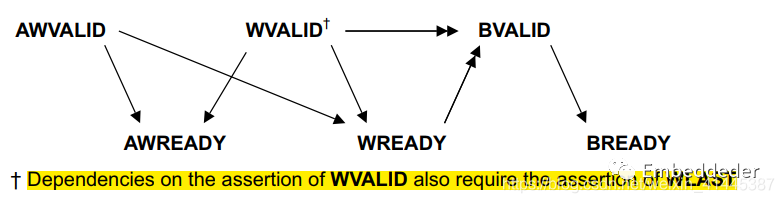

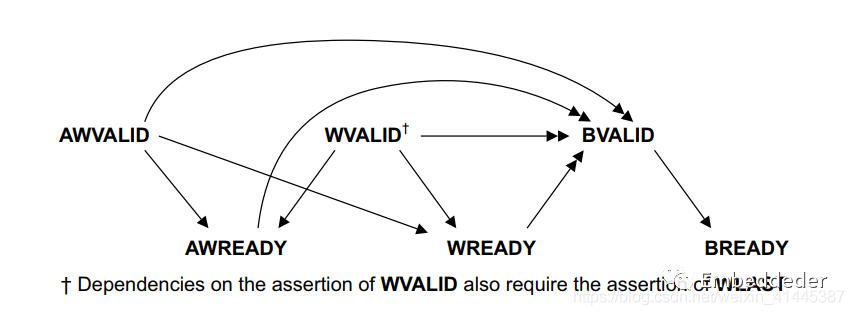

通道握手信號之間的依賴關系,,由下面的流程圖進行描述,這里先進行圖示說明:在依賴關系圖中,單箭頭指向可以在箭頭指向的信號之前或之后拉高信號;雙箭頭指向的信號必須在箭頭指向的信號斷言之后才能拉高。

讀操作依賴關系

上圖顯示讀操作握手信號的依賴關系,在讀操作中:

從機必須等待ARVALID和ARREADY都拉高后,RVALID才能進行拉高指示數據有效。

對于ARVALID和ARREADY的順序,可以任意設置先后順序,從機可以等待ARVALID拉高后,再拉高ARREADY,也可以相反,也可以同時拉高。

對于RVALID和RREADY不用關心順序,主機可以任意設置先后順序。可以先后,可以同時。

寫操作依賴關系

上圖顯示寫操作握手信號的依賴關系,在寫操作中:

主機在拉高AWREADY or WREADY不需要關心從機AWVALID or WVALID先后順序。

從機在BVALID拉高之前,WVALID和WREADY必須被拉高。

從機必須WLAST拉高之后,才能拉高BVALID,因為寫響應(BRESP)在寫操作的最后一次數據傳輸之后,才發出信號。

從機不用關心BVALID和BREADY的先后順序。

寫響應依賴關系

上圖顯示寫響應握手信號的依賴關系,在寫響應中:

單頭箭頭指向可以在箭頭指向的信號之前或之后拉高信號

從機須等待AWVALID、AWREADY、WVALID和WREADY都拉高之后,BVALID才能拉高使能。

從機必須WLAST拉高之后,才能拉高BVALID,因為寫響應(BRESP)在寫操作的最后一次數據傳輸之后,才發出信號。

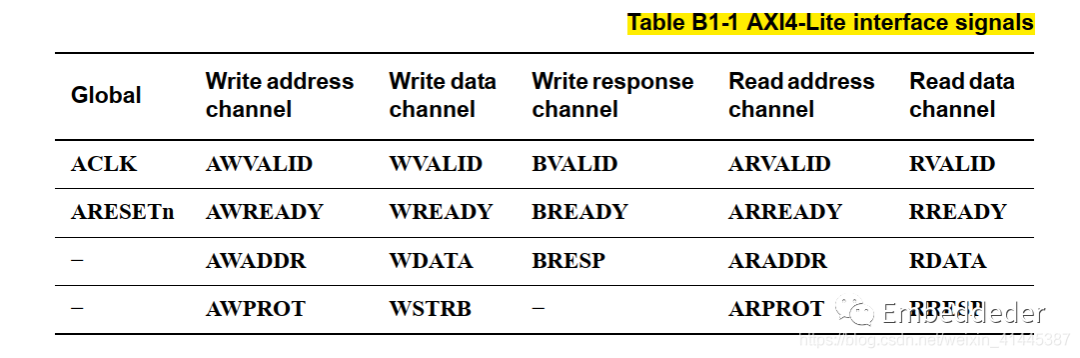

AXI4-Lite協議

AXI4-Lite和AXI4類似,當不需要完整AXI4功能的時,進行一些簡單的控制寄存器的讀寫。AXI4-Lite協議簡單描述如下:

AXI4-Lite協議的所有傳輸的突發長度都是1(相當于不支持突發傳輸)。

所有數據訪問都使用數據總線的全部位寬,支持32位或64位的數據總線寬度。

所有訪問都是不可修改的,不可緩沖的。

不支持獨占訪問。

接口定義

相比前面介紹的AXI4-Full,這里的信號端口就少了很多。但對于相同名字的接口信號含義是相同的,功能相同。

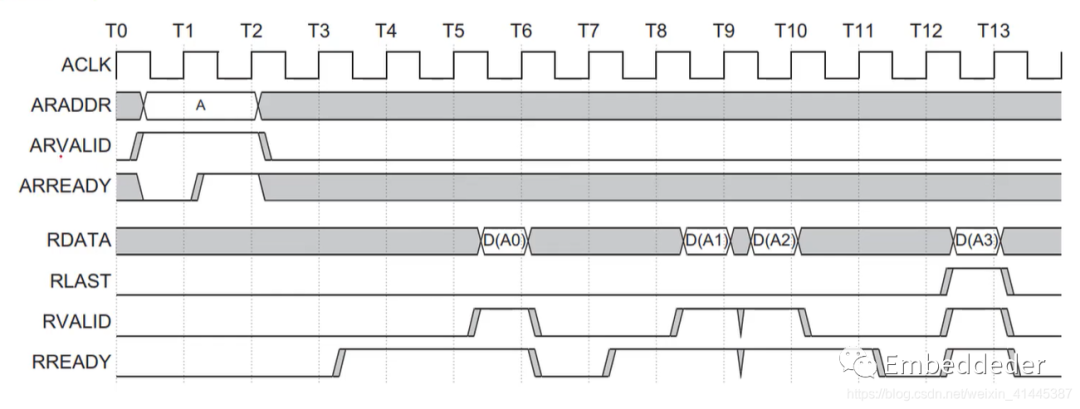

AXI總線協議時序

AXI突發讀

下圖所示,當ARVALID信號和ARREADY信號都拉高時地址有效(地址信息和ARVALID是同步的),也就是在T2時刻讀取到所要讀取的地址,然后等待RVALID和RREADY都拉高,即可讀取到數據,也就是在T5時刻內讀取到第一個數據A0(數據和RVALID是同步的),依次讀取A1、A2、這里的時序圖定義A3為最后一次傳輸,所以RLAST也被拉高。

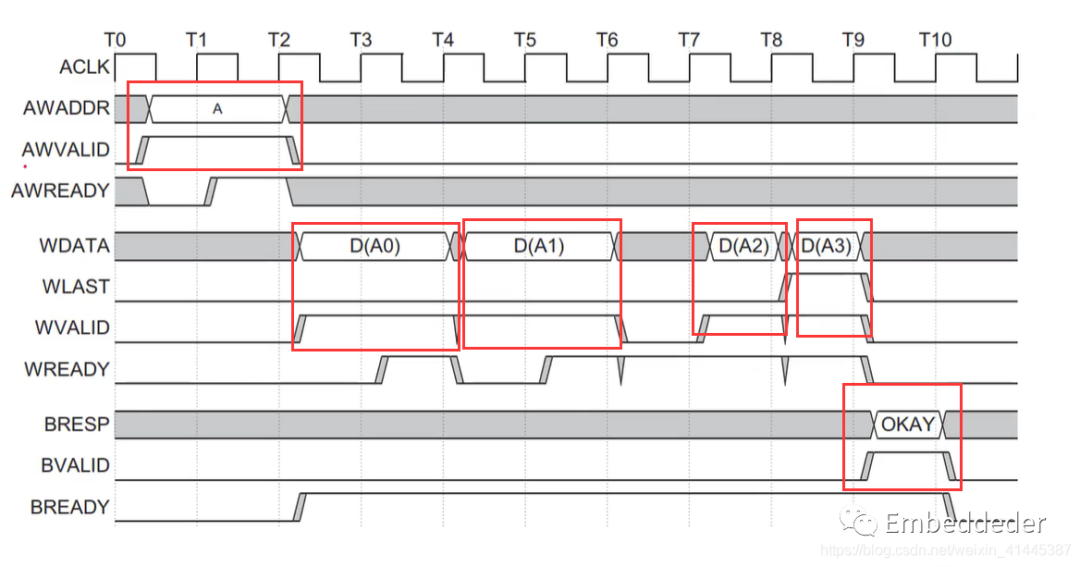

突發寫

下圖所示,當AWVALID信號和AWREADY信號都拉高時地址有效(地址信息和AWVALID是同步的),也就是在T2時刻上升沿讀取到所要寫入的地址。然后主機發送寫入的數據(數據和WVALID信號是同步的),依次寫入A0、A1、A2、A3,當寫入最后一個數據時,WLAST信號也要拉高,當寫操作完成后,從機要發送一個響應信號,這個信號也是在BVALID和BREADY為高時有效。

Reference

ARM公司的IHI0022D。

正點原子ZYNQ開發視頻教程。

編輯:jq

-

ARM

+關注

關注

134文章

9121瀏覽量

368230 -

數據傳輸

+關注

關注

9文章

1928瀏覽量

64715 -

AXI

+關注

關注

1文章

128瀏覽量

16667

原文標題:ZYNQ-AXI總線的信號接口要求以及時序關系

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ZYNQ基礎---AXI DMA使用

總線接口的類型與選擇指南

ADS8698有上電時序要求嗎?

AMBA AXI4接口協議概述

接口芯片的讀寫信號與系統的關系

瀚海微SD NAND之SD 協議(31)總線的信號和時序

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

FPGA 高級設計:時序分析和收斂

有關PL端利用AXI總線控制PS端DDR進行讀寫(從機wready信號一直不拉高)

SoC設計中總線協議AXI4與AXI3的主要區別詳解

PCIe-AXI-Cont用戶手冊

時序電路的分類 時序電路的基本單元電路有哪些

漫談AMBA總線-AXI4協議的基本介紹

淺談ZYNQ-AXI總線的信號接口要求以及時序關系

淺談ZYNQ-AXI總線的信號接口要求以及時序關系

評論