我們用一個(gè)3-8譯碼器來(lái)結(jié)束本次對(duì)組合邏輯電路的介紹,并且最后我們還給大家準(zhǔn)備了一個(gè)略微酸爽的任務(wù),確保大家的腦神經(jīng)都可以得到充分的摩擦。閑話不多,現(xiàn)在開(kāi)始。

本次實(shí)驗(yàn)的任務(wù)是構(gòu)建一個(gè)3-8譯碼器,且將譯碼結(jié)果通過(guò)小腳丫的LED燈顯示。

聽(tīng)上去并不難,而且我能想象到,一定會(huì)有不少同學(xué)會(huì)立刻開(kāi)始畫(huà)一個(gè)8行的真值表,然后通過(guò)卡諾圖進(jìn)行化簡(jiǎn),且根據(jù)最終的邏輯表達(dá)式畫(huà)出門(mén)電路圖。這個(gè)方法當(dāng)然沒(méi)有錯(cuò),不過(guò),如果面對(duì)更多位數(shù)的系統(tǒng),比如4-16或者是8-256的譯碼器,建一個(gè)幾百行的真值表并進(jìn)行邏輯運(yùn)算聽(tīng)上去似乎不那么科學(xué)。

在這里我們將采用模塊化的思路來(lái)完成我們的實(shí)驗(yàn)設(shè)計(jì)。

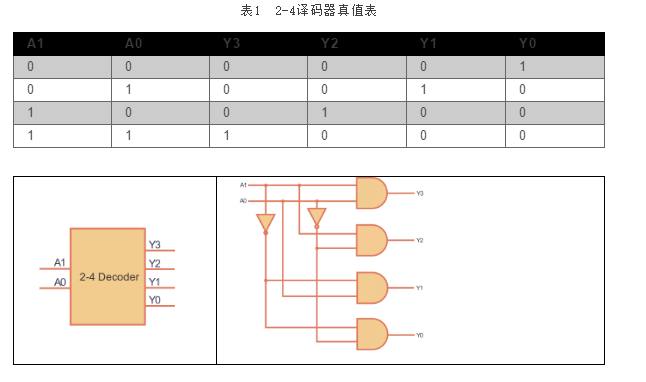

在開(kāi)始進(jìn)行模塊化設(shè)計(jì)之前,我們先做一個(gè)2-4譯碼器,也就是譯碼器系列中最底層的基礎(chǔ)模塊。

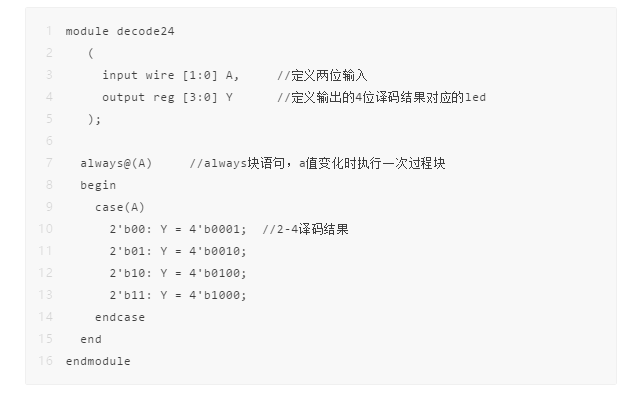

這次的代碼我們采用行為級(jí)描述(Behavioral-level)的寫(xiě)法,直接根據(jù)真值表將輸入與輸出的各種組合進(jìn)行直接關(guān)聯(lián)。可以看出,行為級(jí)的寫(xiě)法甚至不需要構(gòu)建門(mén)電路,僅通過(guò)輸入輸出對(duì)應(yīng)關(guān)系即可構(gòu)建,因此最為抽象。

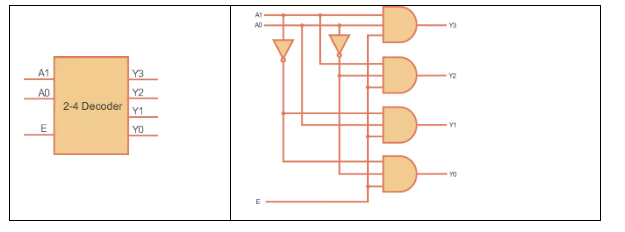

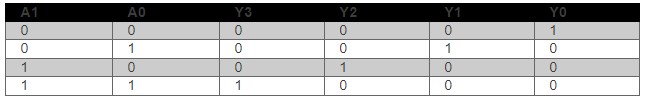

有了最基礎(chǔ)的模塊,如何通過(guò)它搭建出3-8譯碼器呢?現(xiàn)在,我們?cè)谠械恼嬷当砩霞由弦宦肥鼓?a target="_blank">信號(hào)E,再來(lái)觀察一下新的真值表。可以發(fā)現(xiàn),當(dāng)E為低電平時(shí),不論輸入的取值如何,前四位輸出均為0。當(dāng)E為高電平時(shí),右側(cè)仍然為2-4譯碼器的輸出結(jié)構(gòu)。

我們可以把表3看作為一個(gè)3-8譯碼器的真值表,只不過(guò)輸入端的最高位由E代替。由于E為低電平時(shí)輸出最高的四位均為0,因此確保我們?cè)趯?duì)后四位輸出(黃色)進(jìn)行賦值不會(huì)影響到前四位的輸出。

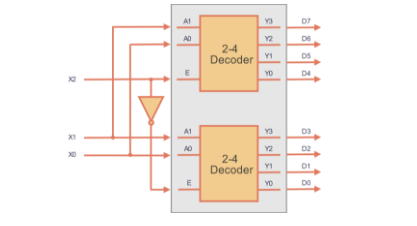

從表3不難看出,黃框和紅框?qū)?yīng)的其實(shí)就是一個(gè)帶有使能端的2-4譯碼器,且使能端E控制著前后半端位數(shù)的輸出結(jié)果。也就是說(shuō),一個(gè)3-8譯碼器可以由兩個(gè)2-4譯碼器構(gòu)成。同理,一個(gè)4-16譯碼器可以由兩個(gè)3-8譯碼器構(gòu)成,以此類(lèi)推。

帶有使能E的2-4譯碼器如下圖所示。實(shí)際上就是在之前的代碼上稍做修改,在這里我們就不詳細(xì)寫(xiě)出來(lái)了,給大家自行練習(xí)的機(jī)會(huì)。

接下來(lái),按照之前的分析,我們畫(huà)出由兩個(gè)2-4譯碼器組成的3-8譯碼器的結(jié)構(gòu)。

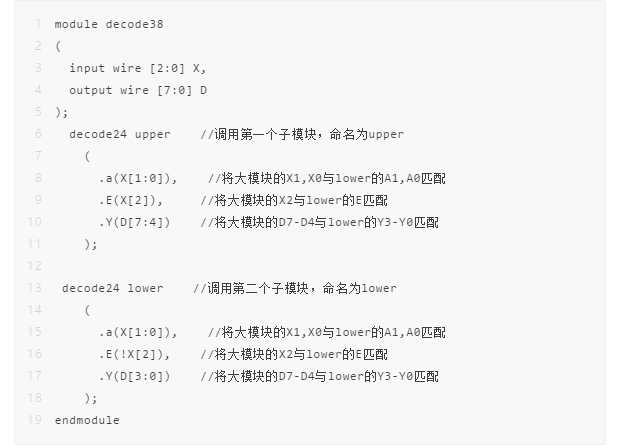

以下是用Verilog寫(xiě)的一個(gè)3-8譯碼器,在程序里我們調(diào)用了兩次2-4譯碼器的子模塊。注意,子模塊的文件需要和decode38文件放在同一個(gè)工程目錄下,不然就成了隔壁老王了。

當(dāng)你反復(fù)在圖和代碼之間徘徊幾輪,并有了多么痛的領(lǐng)悟之后,你就可以把自己編譯好的程序下載到小腳丫里,然后通過(guò)實(shí)驗(yàn)測(cè)試你的代碼了。

練習(xí)一下,當(dāng)我們把輸出D7-D1分別對(duì)應(yīng)為小腳丫上的L7-L1,且輸入X2-X0分別對(duì)應(yīng)至小腳丫的SW3-SW1,請(qǐng)判斷以下的LED狀態(tài)(低電平亮)。

在倒騰了半天之后,你終于搞定了代碼,并且成功在小腳丫上驗(yàn)證了你的設(shè)計(jì),于是滿(mǎn)懷信心的你終于可以嘗試一下通過(guò)模塊化的設(shè)計(jì)思路去構(gòu)建4-16甚至更多位的譯碼器了。

責(zé)任編輯人:CC

-

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42664 -

譯碼器

+關(guān)注

關(guān)注

4文章

312瀏覽量

50400

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何使用SN74LV4051A搭建一個(gè)3,-8譯碼器?

設(shè)計(jì)一個(gè)虛擬3-8譯碼器,實(shí)現(xiàn)138譯碼器的功能

關(guān)于 3-8譯碼器的 vhdl描述問(wèn)題

設(shè)計(jì)一個(gè)虛擬3-8譯碼器,實(shí)現(xiàn)138譯碼器的功能

用QT的強(qiáng)制轉(zhuǎn)換函數(shù)寫(xiě)3-8譯碼器

3-8譯碼器進(jìn)行仿真設(shè)置問(wèn)題

Xilinx FPGA入門(mén)連載20:3-8譯碼器實(shí)驗(yàn)

怎么用3-8譯碼器實(shí)現(xiàn)8個(gè)led的簡(jiǎn)單算法的循環(huán)點(diǎn)亮

請(qǐng)問(wèn)怎么使用SN74LV4051A搭建一個(gè)3,-8譯碼器?

用2-4譯碼器連接為3-8譯碼器

求一種在FPGA中使用行為描述語(yǔ)句實(shí)現(xiàn)3-8譯碼器的設(shè)計(jì)方案

基于FPGA采用模塊化思路設(shè)計(jì)一個(gè)譯碼器

如何采用模塊化思路構(gòu)建一個(gè)3-8譯碼器

如何采用模塊化思路構(gòu)建一個(gè)3-8譯碼器

評(píng)論