什么是競爭和冒險?

(1)競爭

在一個組合電路當中,當某一個變量經過兩條以上的路徑到達輸出端的時候,由于每條路徑上的延遲時間的不同,到達終點的時間就會有先有后,這一現象稱作競爭。

(2)冒險

在具有競爭現象的組合電路中,當某個變量發生變化的時候,比如說從 1 跳到 0,或者說從 0 跳到 1,如果真值表所描述的邏輯關系或者功能遭受到短暫的破壞,在輸出端出現一個不應有的尖脈沖毛刺,這種現象就叫冒險。

冒險是由競爭造成的,而競爭是因為電路中的時延不同,所以選D,

冒險是因為電路中的時延問題導致。

但是有競爭的時候不一定會出現冒險。

怎么識別競爭冒險?

(1)公式法

寫出邏輯表達式,當某些邏輯變量取特定值 0 或 1 時,

若邏輯表達式能轉換為 A·(~A),則該電路存在1型冒險(該為 0 的時候出現了為 1 的錯誤數據,1 型冒險);

若邏輯表達式能轉換為 A+(~A),則該電路存在0型冒險(該為 1 的時候出現了為 0 的錯誤數據,0 型冒險)。

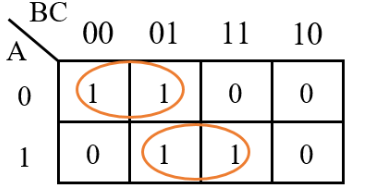

(2)卡諾圖法

畫出其卡諾圖,

若輸入變量在卡諾圈內改變時,則輸出不會有冒險現象;

若輸入變量是在相鄰卡諾圈的相鄰處發生變化,并且是從一個卡諾圈進入另一個卡諾圈,則有可能產生邏輯冒險現象。(卡諾圖相切)

當A=1、C=0,B由0->1時,在卡諾圈內變化,不會出現冒險;

當B=C=1,A由0>1時,在卡諾圈內變化,不會出現冒險。

當A=B=1,C從0>1時,相當于輸入變量A、B、C從110變化到111,此時的變化是從一個卡諾圈變化進入另一個卡諾圈,該電路輸出存在冒險現象。

如何消除冒險?

(1)增加冗余項

增加一個冗余項AB,這樣狀態變化時也是在卡諾圈內變化,此時邏輯表達式不是最簡表達式,但是消除了冒險。

(2)增加選通信號(高電平)

輸入端加入選通信號,針對 A+(~A) 的 1 型冒險,避開毛刺。

(3)引入封鎖脈沖(低電平)

輸入端加入封鎖脈沖信號,針對 A·(~A) 的 0 型冒險,避開毛刺。

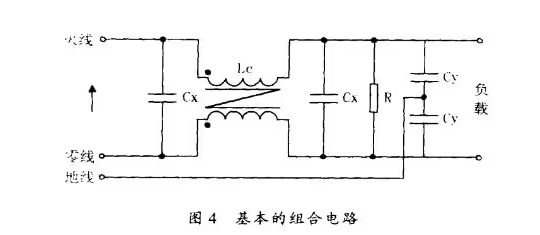

(4)增加濾波電容

冒險輸出的是一個很窄的毛刺,在輸出端接濾波電容將其濾除。

(5)采用可靠性編碼

比如格雷碼,每次只變化1位。

原文標題:組合邏輯競爭冒險,時序邏輯亞穩態【0型冒險和1型冒險及其消除方法】

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

電路

+關注

關注

172文章

5914瀏覽量

172254 -

時序

+關注

關注

5文章

387瀏覽量

37333

原文標題:組合邏輯競爭冒險,時序邏輯亞穩態【0型冒險和1型冒險及其消除方法】

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

安全型繼電器型號表示方法

電流反饋型運放與電壓反饋型運放

從山川到海洋,BIG WALNUT大核桃三防手機陪伴你的每一步冒險

組合電路中0型冒險和1型冒險及其消除方法

組合電路中0型冒險和1型冒險及其消除方法

評論