作者:谷國棟;田波;張永順

1 引言

隨著無線電技術的迅猛發展,雷達、導航、宇宙飛行、導彈及空間探索工作都需要高穩定度、高精度的頻率源。鎖相振蕩源具有頻率穩定度高、相位噪聲低、易于集成等突出優點,因而成為通信、雷達、武器制導和電子測量儀器等系統的核心部件。在射頻及微波系統中,采用串行碼數據輸入的數字式電荷泵頻率合成器,外接壓控振蕩器(VCO)和環路濾波器,即可組成鎖相(PLL)頻率源。它具有電路設計簡單、功耗低、可靈活編程控制分頻比來調整鎖相環路的工作頻率等優點,在3GHz以下均可方便地直接構成PLL振蕩源。目前,具有代表性的產品是美國國家半導體公司的LMX23XX系列、菲利普公司的UMAl0系列和SA小數分頻系列、富士通公司的MB15系列頻率合成器。

本文介紹的富士通公司生產的MBl5U36是一種高性能的雙環集成鎖相環頻率合成器,芯片內集成了鎖相頻率合成器的多種重要部件,使用時只需再合理搭配上一或二塊集成電路和少量的外圍電路,即可構成一個完整且可靠性很高的頻率合成器,該電路的設計簡單,應用靈活,且能減小系統體積。

2 MBl5U36的結構及性能

2.1MBl5U36的結構

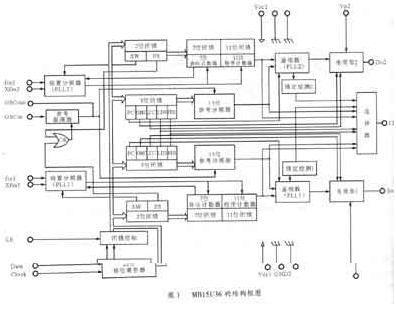

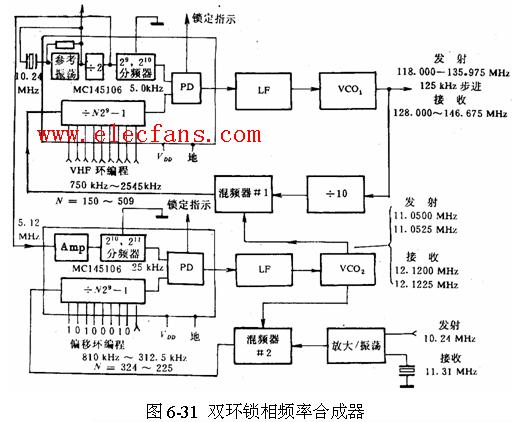

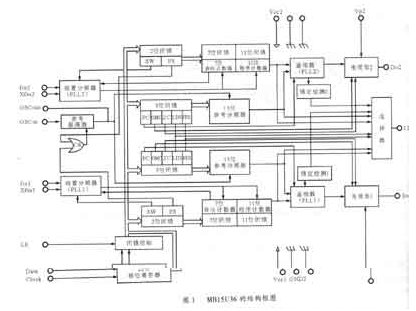

MBl5U36為串行碼數據輸入的數字式電荷泵型頻率合成器,圖1示出其結構框圖,兩環路組成結構的形式相同,主要包括鑒相器、電荷泵、可編程數字分頻器(主程序分頻器、參考分頻器)、前置分頻器等部分。其主要特性如下:最高工作頻率1.2GHz(RF2)、2.0GHz(BFl);具有64/65或128/129可選的雙模前置分頻器;電源電壓范圍為3.0V~5.5V;電流消耗典型值為6mA;內含平衡式、低泄漏電荷泵;具有節能工作模式。在Vcc=3V時,電流消牦典型值為10μA;采用20引腳SSOP型封裝。

2.2 MBl5U36的引腳功能

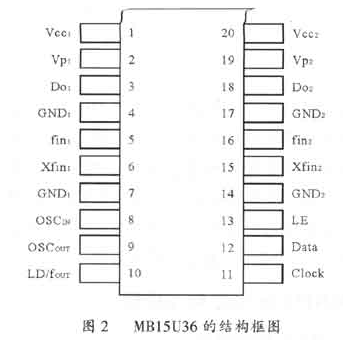

MBl5U36的引腳排列形式如圖2所示,括號內的數字為引腳號。

OSGIN(8)和OSCOUT(9)是參考振蕩器的輸入端和輸出端,外接溫度補償晶體振蕩器或晶體時,通過交流耦合到輸入端。

VCC1(1)是RF1-PLL(頻率合成器1)電源電壓輸入端,電壓范圍為3V~5.5V,電源濾波的旁蹋器應盡可能靠近該腳,并直接連接到地。

V CC12(20)是RF2-PLL(頻率合成器2)電源電壓輸入端,電壓范圍為3V~5.5V,電源濾波的旁路器應盡可能靠近該腳,并直接連接到地。

VP1(2)是RF1-PLL電荷泵的工作電壓輸入端。

VP2(19)是RF2-PLL電荷泵的工作電壓輸入端。

DO1(3)是RF1-PLL內部電荷泵輸出端,可通路濾波器來控制外部VCO。

DO2(18)是RF2-PLL內部電荷泵輸出端,可環路濾波器來控制外部VCO。

Fin1 (5)是RF1-PLL的前置分頻器輸入端,號輸入,通過交流耦合形式連接VCO。

Fin2(16)是RF2-PLL的前置分頻器輸入端,號輸入,通過交流耦合形式連接VCO。

Xfin1 (6)是RF1-PLL前置分頻器補充輸入端接旁路電容器應盡可能靠近該腳,并直接連接到地。

Xfin2(15)是RF2-PLL前置分頻器補充輸人竭接旁路電容器應盡可能靠近該腳,并直接連接到地。

GND1(4,7)是RF1-PLL接地端。

GND2(14,17)是RF2-PLL接地端。

LD/fOUT(10)是鎖定檢測輸出或相位比較監測輸出端,輸出方式可通過串行格式編程數據流的LDS和FDS位進行選擇。

Clock(11)是22位移位寄存器時鐘輸入端,數據在時鐘的上升沿進入各個寄存器。

Data(12)是串行數據輸入端,根據串行格式編程數據流中控制位的設置,數據被傳輸到相應的鎖存器。

LE(13)是使能輸入端,當LE端變為高電平時,根據串行格式編程數據流中控制位的設置,移位寄存器中的數據將傳送到相應的閉鎖。

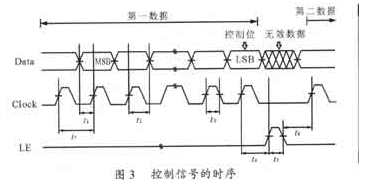

圖3示出Clock、Data和LE端的控制信號時序。

3 典型應用

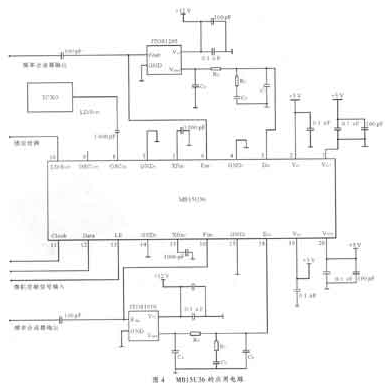

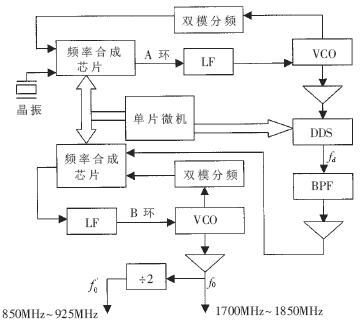

我們采用串行碼數據輸入的數字式微波頻率合成器設計的PLL振蕩源,可作為某通信系統干擾機的本振源。以MBl5U36為核心,選擇適當的外部VCO,設計相應的環路濾波器,設計構成的低噪聲、高穩定度的頻率合成器組成框圖如圖4所示。兩個環路鎖定在同一個溫補參考晶振(TCXO)頻率上,各環路分別接各自的VCO及三階環路濾波器。各環路的分頻比、參考分頻比率等數據(Data)在基帶部分的CPU上設定后,與時鐘信號(Clock)、使能信號(LE),按串行格式通過BUS總線一同送入。選用的晶振參考頻率為10MHz,環路1輸出頻率范圍為1 720MHz~1 850MHz,頻率間隔為200kHz,參考分頻比為50,環路總分頻比8 600~9 250。環路2輸出頻率范圍為740MHz~960MHz,頻率間隔為20kHz,參考分頻比為500,環路總分頻比37 000~48 000。雙模前置分頻器工作于64/65模式,MBl5U36內部電荷泵輸出誤差經環路濾波器后驅動壓控振蕩器,從而形成鎖相環路。

4 環路濾波器設計

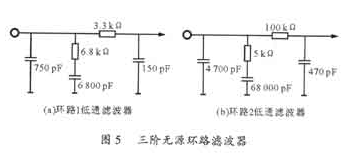

頻率合成器應保證很低的相位噪聲,必須根據指標要求選擇高性能的頻率合成器、低噪聲的VCO及設計濾波特性良好的環路濾波器。環路濾波器的作用是抑制鑒相器輸出電壓中的載頻分量和高頻噪聲,降低由VCO控制電壓的不純而引起的寄生輸出。對電荷泵型的頻率合成器,MB15U36推薦使用二階或高階無源低通濾波器,圖5為三階低通環路濾波器。我們采用開環增益帶寬和相位裕度法推導出濾波器元件計算公式,當環路帶寬ωp,VCO的電調靈敏度Kr、主分頻比N、鑒相靈敏度Kp及對鑒相頻率所需增加的額外衰減A確定以后,可編制出計算三階環路濾波器的程序,只需輸入已知參數,即可得到元件的標稱值。其中,N值變化較大,可按N=√N1N2取值,N1從分別為最小和最大環路分頻比(例如本文環路2設計中對N的取值采用N= √N1N2=2 261)。利用此程序計算出環路濾波器的元件值,實驗證明計算結果可靠,設計的環路濾波器元件值在圖中標出。

責任編輯:gt

-

鎖相環

+關注

關注

35文章

584瀏覽量

87767 -

濾波器

+關注

關注

161文章

7817瀏覽量

178128 -

頻率合成器

+關注

關注

5文章

219瀏覽量

32354

發布評論請先 登錄

相關推薦

鎖相環MC14046構成的新型頻率合成器

雙環集成鎖相環頻率合成器MBl5U36的性能特點及典型應用分析

雙環集成鎖相環頻率合成器MBl5U36的性能特點及典型應用分析

評論