【引言】

本系列教程演示如何使用xilinx的HLS工具進行算法的硬件加速。分為三個部分,分別為HLS端IP設計,vivado硬件環境搭建,SDK端軟件控制。 在HLS端,要將進行硬件加速的軟件算法轉換為RTL級電路,生成便于嵌入式使用的axi控制端口,進行數據的傳輸和模塊的控制。

【HLS介紹】

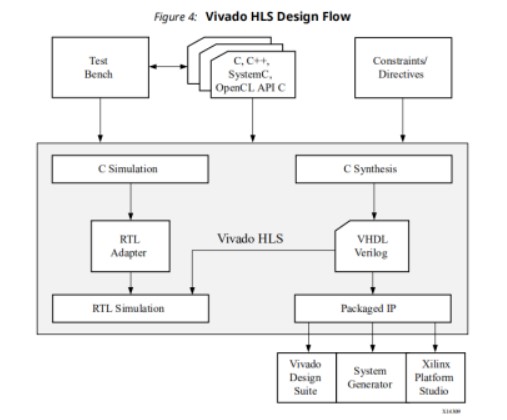

HLS可以將算法直接映射為RTL電路,實現了高層次綜合。vivado-HLS可以實現直接使用 C,C++ 以及 System C 語言對Xilinx的FPGA器件進行編程。用戶無需手動創建 RTL,通過高層次綜合生成HDL級的IP核,從而加速IP創建。 HLS的官方參考文檔主要為:ug871( ug871-vivado-high-level-synthesis-tutorial.pdf )和ug902(ug902-vivado-high-level-synthesis.pdf)。 對于Vivado Hls來說,輸入包括Tesbench,C/C++源代碼和Directives,相應的輸出為IP Catalog,DSP和SysGen,特別的,一個工程只能有一個頂層函數用于綜和,這個頂層函數下面的子函數也是可以被綜合的,會生成相應的VHDL和Verilog代碼,所以,C綜合后的RTL代碼結構通常是跟原始C描述的結構是一致的,除非是子函數功能很簡單,所需要的邏輯量很小。并不是所有的C/C++都可以被綜合,動態內存分配和涉及到操作系統層面的操作不可以被綜合。 Vivado HLS 的設計流程如下:

在整個流程中,用戶先創建一個設計 C、C++ 或 SystemC 源代碼,以及一個C的測試平臺。通過 Vivado HLS Synthesis 運行設計,生成 RTL 設計,代碼可以是 Verilog,也可以是 VHDL。有了 RTL 后,隨即可以執行設計的 Verilog 或 VHDL 仿真,或使用工具的C封裝器技術創建 SystemC 版本。然后可以進行System C架構級仿真,進一步根據之前創建的 C 測試平臺,驗證設計的架構行為和功能。設計固化后,就可以通過 Vivado 設計套件的物理實現流程來運行設計,將設計編程到器件上,在硬件中運行和/或使用 IP 封裝器將設計轉為可重用的 IP。

Step 1: 新建一個工程

1,Creat New Project新建文檔,輸入工程名稱和工程路徑。完成后點擊Next。

2,添加設計文件,并制定頂層函數。完成后點擊Next。

3,添加C語言仿真文件。完成后點擊Next。

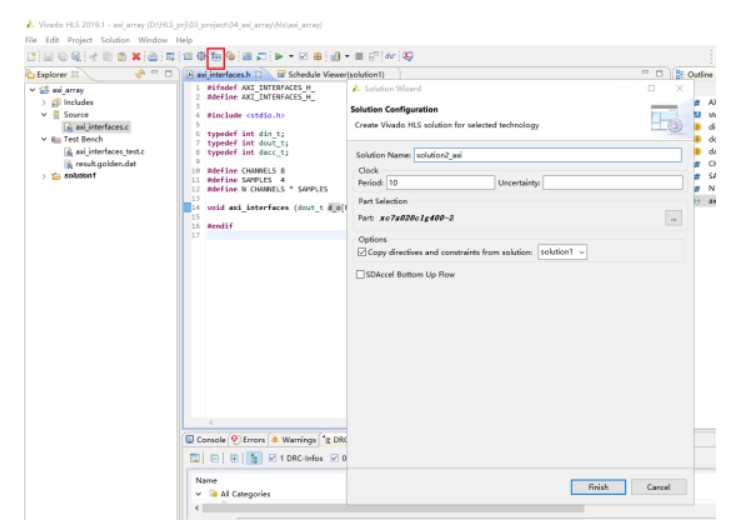

4,:配置Solution Name,一般默認即可。配置Clock Period,單位是ns。配置Uncertainty,默認為空。選擇產品型號。完成后點擊Finish。

5,工程新建成功后進入的開發界面,HLS是典型的Eclipse界面,和SDK的界面十分相似。

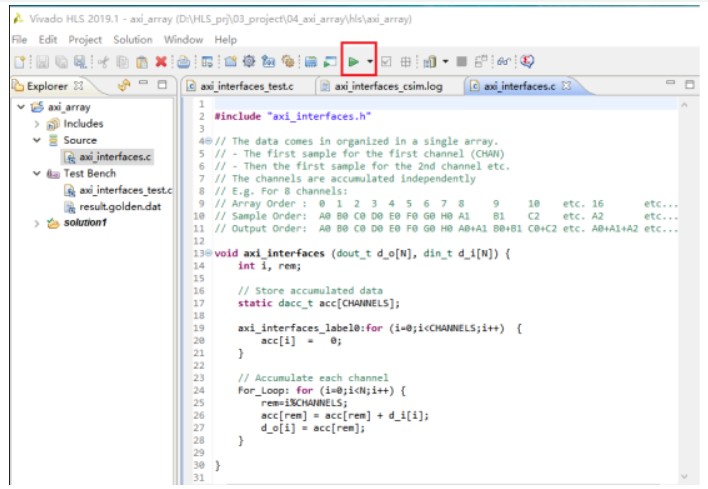

導入的文件的代碼如下: 1,源文件。axi_interfaces.c

#include"axi_interfaces.h"void axi_interfaces (dout_t d_o[N], din_t d_i[N]) {inti,rem;// Store accumulated datastaticdacc_tacc[CHANNELS];axi_interfaces_label0:for (i=0;i

#ifndef AXI_INTERFACES_H_ #defineAXI_INTERFACES_H_ #include

#include "axi_interfaces.h" int main () { // Create input data din_t d_i[N] = {10, 20, 30, 40, 50, 60, 70, 80, 11, 21, 31, 41, 51, 61, 71, 81, 12, 22, 32, 42, 52, 62, 72, 82, 13, 23, 33, 43, 53, 63, 73, 83}; dout_t d_o[N]; int i, retval=0; FILE*fp; // Call the function to operate on the data axi_interfaces(d_o,d_i); // Save the results to a file fp=fopen("result.dat","w"); fprintf(fp, "Din Dout "); for(i=0;i

Din Dout 10 10 20 20 30 30 40 40 50 50 60 60 70 70 80 80 11 21 21 41 31 61 41 81 51 101 61 121 71 141 81 161 12 33 22 63 32 93 42 123 52 153 62 183 72 213 82 243 13 46 23 86 33 126 43 166 53 206 63 246 73 286 83 326

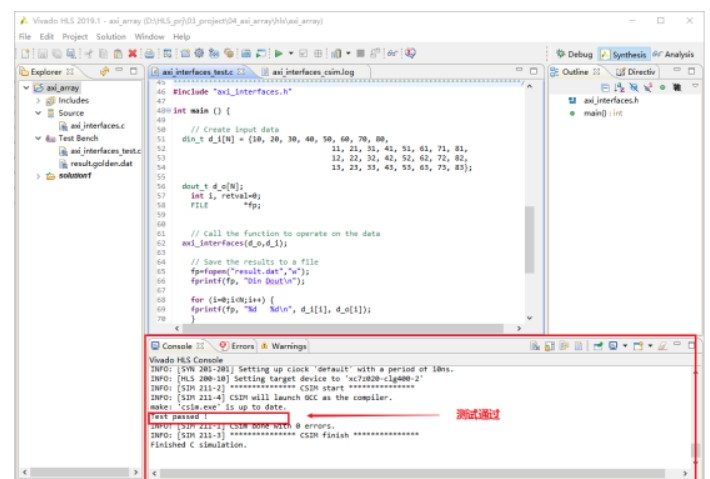

本步驟是對功能代碼的邏輯驗證,相當于功能前仿。

2,點擊紅框中的按鈕,開始C源代碼驗證。

3,驗證的結果顯示在控制欄中。如圖顯示,測試通過。

4,在頭文件中,重定義了數據類型,參數,并進行了函數聲明。

Step 3: 高層次綜合

本步驟是把功能代碼的綜合成RTL邏輯。 1,點擊紅框中的按鈕,將C代碼綜合成RTL。綜合完成后,查看結果。

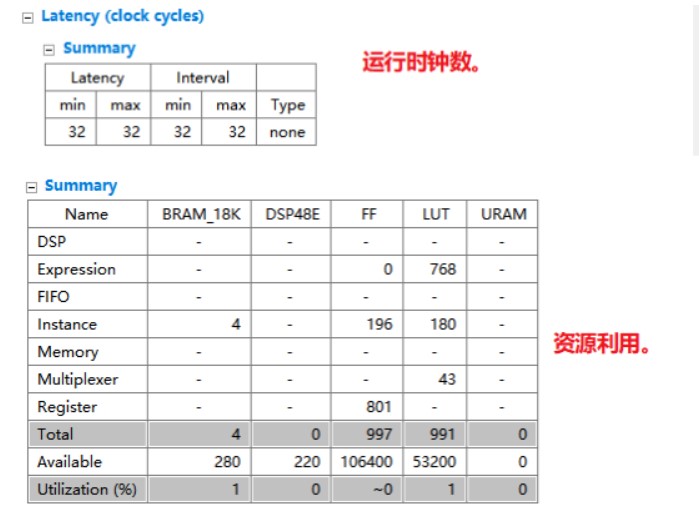

2,綜合完成后,查看綜合報告。包括時序,延時,資源占用,端口信息等。

3,端口分析。(1)控制端口用于控制和顯示該模塊的工作狀態。各個端口的功功能如下,默認情況下會生成下面四個控制端口。 lap_start(in):為高時,該模塊開始處理數據。 lap_done(out):為高時,表示模塊處理數據完成。 lap_idle(out):表明模塊是否處于空閑態。高電平有效。為高時,該處于空閑態。 lap_ready(out):為高時,表示模塊可以接受新的數據。(2)數據端口用于傳遞模塊的輸入輸出參數。 參數d_o,d_i 為數組類型,故默認狀態下回生成內存接口。內存接口 (數組類型參數)數據來自外部的memory,通過地址信號讀取相應的數據,輸入到該模塊中。輸入數組從外部內存中讀源數據,輸出數組從向外部內存寫入結果數據。各個端口的定義如下。 laddress:地址信號 lce0:片選信號 lwe0:寫使能信號 ld0 :數據信號 4,綜合結果分析。 在分析界面,可以看到模塊的運行情況。包括數據依賴關系和各個周期執行的操作,IO口的讀寫,內存端口的訪問等等。

Step4: 綜合優化

在使用高層次綜合,創造高質量的RTL設計時,一個重要部分就是對C代碼進行優化。 Vivado HLS擁有自動優化的功能,試圖最小化loop(循環)和function(函數)的latency。除了自動優化,我們可以手動進行程序優化,即用在不同的solution中添加不同的directive(優化指令)的方法,進行優化和性能對比。其中,對同一個工程,可以建立多個不同的solution(解決方案),為不同的solution添加directive可以達到如下目的。 優化的類型可分為如下類別: l端口優化。指定不同類型的模塊端口。 l函數優化。加快函數的執行速度,減小執行周期。 l循壞優化。利用展開和流水線形式,減小循環的執行周期。

2,不同solution位于不同的文件夾中。

3,選中綜合文件。可以在direct框中看可進行優化的標簽。

4,雙擊選擇d_o,選擇interface,s_axilite。點擊ok。將d_o的端口類型設置為s_axilite類型。

5,參考d_o,將d_i的接口類型也設置為s_axilite。將d_i的端口類型設置為s_axilite類型。

6,雙擊選擇函數名稱axi_interface,選擇interface,s_axilite。點擊ok。將控制端口的端口類型設置為s_axilite類型。

7,雙擊循環標簽,選擇流水線優化(pipeline),點擊ok。

8,雙擊循環標簽,選擇循環展開優化(unroll),點擊ok。

9,同上,也將標簽為for_loop的循環進行流水線和展開優化。

11,重新進行函數綜合,查看綜合報告如下。

12,分析。 同未優化相比,優化過后的函數綜合后生成的模塊的運行時鐘大大減小。端口的接口類型也變為了axi_lite端口。但資源占用率有所增加,也體現了用資源換速度的設計理念。

Step5: 綜合結果文件

綜合完成后,在各個solution的syn文件夾中可以看到綜合器生成的RTL代碼。包括systemc,VHDL,Verilog。

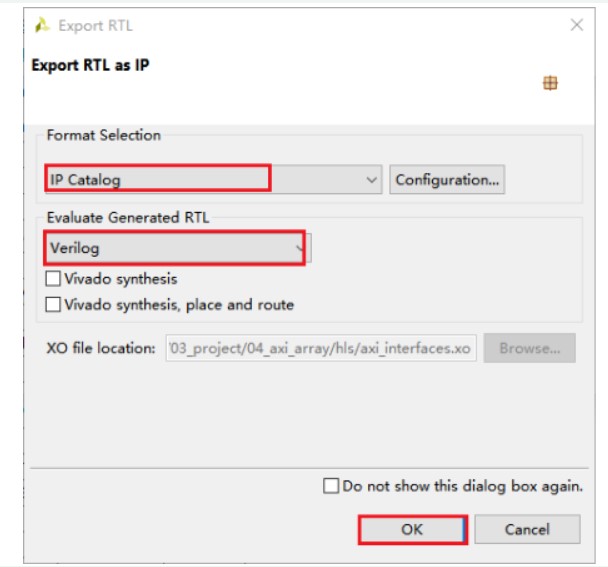

Step6:導出IP

在菜單里Solution>Export TL,設置如下,點擊ok。

IP封裝完成后,會在impl文件夾中輸出ip文件夾,其中包含了RTL代碼(hdl),模塊驅動(drivers),文檔(doc)等信息,其中包含一個壓縮包文件,是用于建立vivado工程所用的IP壓縮包。

Step7:總結

本文重點講解了hls軟件的使用方法和優化方法,在C語言模塊設計上沒有重點講解。在掌握了hls軟件的基本用法和優化方法后,接下來就可以設計更加復雜的C語言模塊,進行rtl綜合,加快設計開發的速度。

責任編輯:lq6

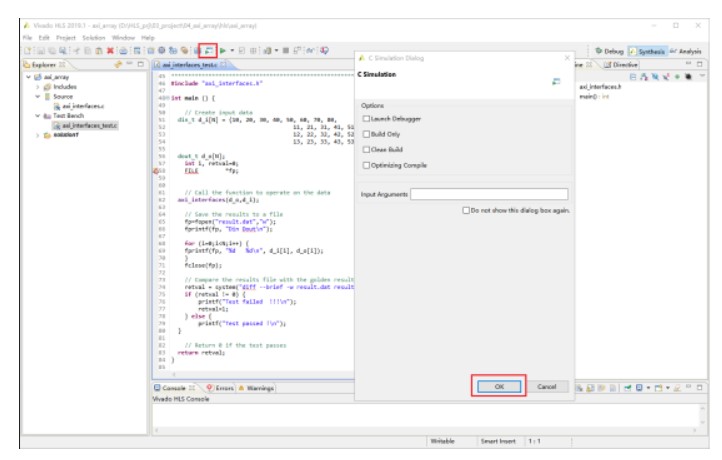

Step 2: C源代碼驗證

1,測試程序的代碼入下圖。該程序先調用綜合的函數,得到計算結果,再和預先的數據集進行比較,最后返回計較的結果。計算結果和預先的數據集一致時,測試通過,不一致時,測試失敗。需要查看代碼,尋找錯誤。

1,點擊下面紅框的圖標,新建solution。

10,最終的優化情況總結如下。

-

HLS

+關注

關注

1文章

130瀏覽量

24159

原文標題:Vivado-hls使用實例

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

探針頭型使用方法有哪些

優化 FPGA HLS 設計

ModBus Scan32模擬軟件的使用方法

可編程電源使用方法

光纖熱縮管正確使用方法

RA MCU中的CRC模塊和使用方法

重點介紹hls軟件的使用方法和優化方法

重點介紹hls軟件的使用方法和優化方法

評論