伴隨著導(dǎo)航系統(tǒng)功能日益多樣化、軟件算法愈加復(fù)雜和集成度要求更高的趨勢,在大規(guī)模可編程器件上設(shè)計、驗證和測試導(dǎo)航SoC芯片成為解決方案之一。導(dǎo)航系統(tǒng)SoC芯片設(shè)計的要求主要有:

①安全性。芯片的所有功能模塊運行正常,運行機(jī)制透明,可靠性強。

②可配置性。根據(jù)應(yīng)用要求對硬件進(jìn)行裁減和配置,達(dá)到最佳的功能、功耗和面積比。

③高運算能力。具備在特定時間內(nèi)完成復(fù)雜算法的運算能力。

SoC芯片的核心是實現(xiàn)運算和控制功能的微處理器。LEON是一款基于SPARC V8架構(gòu)的開源微處理器IP軟核,在VHDL源代碼基礎(chǔ)上,結(jié)合具體需求加入定制的運算單元和外設(shè)接口建立SoC系統(tǒng)。在配置靈活的LEON核上運行Embedded Linux,提供SoC調(diào)試和測試的基本平臺。

1 軟硬件平臺構(gòu)建

1.1 LEON軟核架構(gòu)簡介

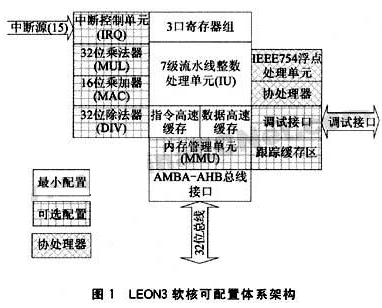

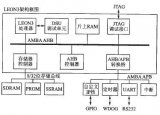

LEON核心是一個與SPARCV8兼容的整數(shù)處理單元IU(Integer Unit),LEON2是5級流水線,LEON3是7級流水線。LEON包含整數(shù)硬件乘法和除法單元、雙協(xié)處理器接口(FPU浮點處理單元和Co-processor協(xié)處理器),分離的指令和數(shù)據(jù)總線(Harvard結(jié)構(gòu))。LEON通過高速的AMBA-AHB總線,指令緩存和數(shù)據(jù)緩存分別和內(nèi)存控制器及高速的外部接口相連傳輸數(shù)據(jù)。低速的AMBA-APB總線實現(xiàn)片上外設(shè)的接口,例如定時器、串口、網(wǎng)絡(luò)接口等。LEON3軟核可配置體系架構(gòu)如圖1所示。

1.2 LEON在SoC芯片開發(fā)應(yīng)用中的優(yōu)勢

LEON軟核最突出的優(yōu)勢是其良好的可配置性和可移植性,以及遵循GPL許可證協(xié)議的開源性。這些特性保證導(dǎo)航系統(tǒng)SoC芯片的安全性,提供良好的性能和靈活的解決方案,也決定了在LEON上進(jìn)行嵌入式操作系統(tǒng)移植的特殊性。

1.2.1 開源性

基于GPL許可證協(xié)議,LEON非容錯版本軟核IP提供VHDL源代碼,僅是容錯版本的LEON軟核需要商業(yè)授權(quán)。源代碼公開是實現(xiàn)導(dǎo)航系統(tǒng)SoC芯片設(shè)計安全性的前提,同時也使研究者和開發(fā)者從根本上研究軟核的細(xì)節(jié)從而定制滿足具體應(yīng)用的軟核成為可能。與全部源代碼開放的LEON相比,Altera的NIOS軟核等其他軟核僅提供若干接口,無法在更深的軟核層次上進(jìn)行設(shè)計和優(yōu)化。

1.2.2 優(yōu)異的可配置性

LEON軟核通過集成一套豐富的接口和運算單元IP庫,根據(jù)具體要求來達(dá)到性能、功耗和面積的平衡和優(yōu)化的目的。

①軟核IU可配置參數(shù)包括流水線的深度、地址和數(shù)據(jù)高速緩存(Cache)。另外,常用指令及指令序列可以根據(jù)定制的硬件進(jìn)行優(yōu)化;在設(shè)計或配置新運算單元后能夠?qū)χ噶罴M(jìn)行擴(kuò)展。在導(dǎo)航系統(tǒng)SoC芯片設(shè)計中,通過配置LEON的整數(shù)硬件乘除法單元以實現(xiàn)較高的運算性能;而在其他某些使用軟件乘除法,即滿足要求的應(yīng)用中無需配置,以降低功耗和優(yōu)化芯片面積。

②外圍設(shè)備接口硬件通過掛載AMBA總線來實現(xiàn)。LEON3的AMBA-AHP總線上能夠靈活選擇集成opencores的以太網(wǎng)控制器和GRETH以太網(wǎng)控制器中的任意一個。針對導(dǎo)航系統(tǒng)中常見的1553總線接口設(shè)備,在LEON中通過配置GR1553單元完成1553總線到AMBA-AHB總線的轉(zhuǎn)換,為1553總線設(shè)備的集成提供了方便。

③硬件加速單元(如特定加密算法、數(shù)字信號處理單元和浮點處理單元)根據(jù)需求集成。

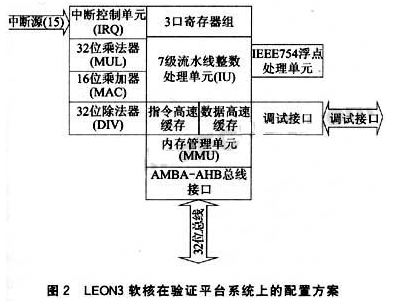

優(yōu)異的可配置性帶來了硬件設(shè)計極大的靈活性,也為嵌入式操作系統(tǒng)的移植帶來了一定難度(特別是在擴(kuò)展了指令集的情況下)。考慮到進(jìn)行性能測試的完整性和靈活性,LEON3軟核在本項目中的配置方案如圖2所示。(詳細(xì)配置參數(shù)未列出)

1.2.3良好的可移植性

LEON軟核通過層次度分明的VHDL模型實現(xiàn)。通過VHDL中特定的配置接口,LEON核的關(guān)鍵參數(shù)(例如修改Cache的大小和組織方式,乘法器的生成,速度、芯片面積的調(diào)整以及容錯方案的選擇)都能夠靈活設(shè)置和移植;而唯一使用專用技術(shù)的模型是內(nèi)存宏模塊。這一部分的設(shè)計采用了加上中間交互層接口的方式,因此移植的工作僅需重新編寫中間交互層接口。導(dǎo)航系統(tǒng)中包括單次濾波在內(nèi)的大量算法經(jīng)過硬件實現(xiàn)后需集成在LEON中,根據(jù)LEON特定的配置接口即可實現(xiàn)集成和SoC系統(tǒng)移植。在本硬件平臺的設(shè)計中,針對特定硬件開發(fā)板,通過修改頂層module文件設(shè)置以及更新引腳配置,即可完成硬件設(shè)計的移植工作。

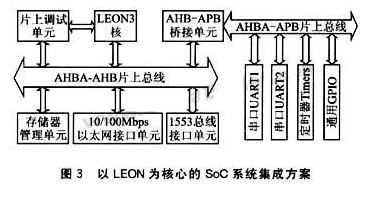

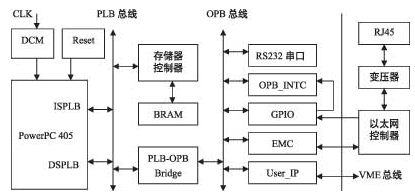

目前,LEON在研究領(lǐng)域被廣泛應(yīng)用,特別是作為軟核嵌入在可編程器件中,作為構(gòu)建SoC芯片的控制和運算中心。LEON軟核的容錯版本也已經(jīng)用在了空間站上。在本導(dǎo)航系統(tǒng)SoC芯片項目中,選擇了開源且配置靈活的LEON硬件平臺和Linux軟件平臺,并且在初期測試中表現(xiàn)出良好的性能。在本驗證平臺上,SoC系統(tǒng)需要以太網(wǎng)接口、1553總線接口、串口、通用I/O口以及調(diào)試單元,具體配置方案如圖3所示。

1.3 Linux系統(tǒng)的移植和調(diào)試

近年來Linux憑借其開源、性能優(yōu)異、軟件資源豐富的優(yōu)勢,在嵌入式平臺上得到了廣泛的應(yīng)用。在LEON上運行的操作系統(tǒng)目前已經(jīng)有RTEMS、eCOS、VxWorks和嵌入式Linux。選擇嵌入式Linux的主要原因,是由于Linux的開發(fā)平臺搭建得比較完善,在工具鏈、內(nèi)核移植、驅(qū)動程序以及應(yīng)用程序的各層上都有很好的支持;使用Linux開發(fā)能夠大大加快開發(fā)的進(jìn)度,并滿足多數(shù)應(yīng)用的指標(biāo)。目前,對LEON提供良好支持的Linux發(fā)行版有Snapgear。由于LEON軟核優(yōu)異的可配置性和可移植性,在LEON上進(jìn)行Linux的移植工作與普通定制的嵌入式微處理器相比,有很多特殊點和難點,主要表現(xiàn)在兩個方面。

(1)配置和編譯內(nèi)核

編譯內(nèi)核的目的在于,生成在目標(biāo)CPU上運行的內(nèi)核。由于LEON自身硬件的可配置性,Linux的源代碼中也需要加入與硬件核相關(guān)的選項進(jìn)行配置。若LEON軟核配置IP,例如硬件加速單元、加密單元或外設(shè)接口,則Linux內(nèi)核中需加入驅(qū)動程序。因此,內(nèi)核的配置分為兩類,一類是配置LEON軟核自身的設(shè)置,另一類是配置目標(biāo)板上的其他外圍設(shè)備,例如內(nèi)存系統(tǒng)、外設(shè)接口等。與一般的定制嵌入式CPU(如ARM體系的CPU)相比,前一類配置是LEON獨有的。這種配置的靈活性為軟硬件平臺的定制提供了極大的方便。例如,Snapgear Embedded Linux根據(jù)具體需求配置硬件乘除法指令和浮點運算單元FPU;在不需要進(jìn)行浮點運算的應(yīng)用中,配置LEON硬件就不需配置浮點單元,相應(yīng)Linux的配置中取消FPU,進(jìn)而節(jié)省硬件資源和軟件的開銷。

項目中實際采取的LEON軟核配置方案為:LEON核選擇LEON2MMU或LEON3MMU,時鐘頻率為50MHz,配置硬件整數(shù)乘除法指令和FPU對應(yīng)的浮點操作指令。外圍設(shè)備配置的串口的起始波特率為38 400 bps,另外,還配置了只讀存儲區(qū)ROM和隨機(jī)存取器RAM。

(2)調(diào)試內(nèi)核

LEON軟核平臺調(diào)試工具有:TSIM、GRSIM和GRMON。

TSIM:SPARC架構(gòu)處理器通用軟件仿真器,用于軟件仿真ERC32-和LEON微處理器。

GRSIM:LEON平臺軟件仿真器,支持多處理器平臺(MP)。

GRMON:LEON平臺硬件仿真調(diào)試器,支持基于GRLIB軟核IP的SoC設(shè)計的硬件調(diào)試。

TSIM作為軟件模擬的VHDL模型,調(diào)試過程中常見的啟動選項設(shè)置如下:

-freq:設(shè)置TSIM模擬LEON處理器硬件的工作頻率,LEON3默認(rèn)為50 MHz。

-fpm:配置模擬FPU模塊。

-nfp:針對無FPU的模擬硬件平臺關(guān)閉FPU。

-nov8:針對無硬件乘除法硬件平臺關(guān)閉硬件乘除法指令。

-pr:指定使用性能觀察器。

在TSIM-LEON平臺上進(jìn)行程序的測試和調(diào)試過程中,Profiling(性能觀察器)能夠顯示程序各個分支函數(shù)以及宏在實際運行中占用的資源,從而為程序的進(jìn)一步優(yōu)化提供必要參考,例如某測試程序在程序運行完畢后使用pro命令得出的結(jié)果:

Program exited normally

tsim>pro

function rario(%)

_start 99.99

_hardreset_real 99.99

main 99.82

processl 92.90

__muldf3 56.44

__adddf3 31.14

…

宏_muldf3和_adddf3在程序運行中占用了大量時間,需進(jìn)一步優(yōu)化。經(jīng)測試證明,通過在LEON中集成FPU消除了宏_muldf3和__adddf3,從而大幅提高浮點運算性能。

2 LEON數(shù)學(xué)運算性能及算法測試

在LEON軟核系統(tǒng)上移植成功Linux后,通過特定測試程序驗證LEON在數(shù)學(xué)運算上的性能,以確定是否滿足項目開發(fā)的需求。測試中對比ARM9 SC32410,分析LEON以及其集成FPU配置的性能,并根據(jù)測試結(jié)果對軟硬件配置進(jìn)一步優(yōu)化。由于LEON硬件配置十分靈活,因此在測試中采用了多種平臺,編譯程序的選項也有對應(yīng)的設(shè)置。中斷響應(yīng)、功耗等雖然也是處理器性能的重要方面,但本文尚未涉及。

2.1 測試平臺

(1)硬件測試平臺

硬件測試平臺如表1所列。

TSIM仿真器通過主機(jī)的浮點機(jī)制來進(jìn)行浮點運算仿真,因此仿真器的浮點精度與主機(jī)平臺相關(guān)。仿真器的時間精度與MeikoFPU相同,集成FPU的LEON3相當(dāng)于集成MeikoFPU的LEON3。

(2)軟件測試平臺

①LEON2和LEON3在Linux 2.6.11下運行。

②直接使用gcc編譯生成程序加載到LEON上并運行,無操作系統(tǒng)。

③SamsungS3C2410在Linux 2.4.18下運行。

(3)不同硬件測試平臺上測試程序說明

不同的硬件平臺和軟件平臺的搭配需在編譯程序過程中指定特定選項(通過Makefile管理):

①一msoft-float選項。LEON平臺上若未集成FPU,則進(jìn)行浮點運算必須指定該選項,此時所有浮點運算轉(zhuǎn)化為軟件模擬實現(xiàn),代價是運行時間大大增加,優(yōu)勢是能夠節(jié)省硬件資源(加入FPU后LEON的LE的使用率是無FPU情況下的近2倍)。

②-mv8選項。LEON平臺上配置硬件整數(shù)乘除法構(gòu)件時需要指定該選項。

③sparc-linux-gcc和sparc-elf-gcc編譯器。對于LEON平臺,若在Linux系統(tǒng)上運行測試程序,則需用sparc-linux-gcc進(jìn)行編譯,程序使用動態(tài)鏈接庫完成鏈接;若直接在LEON硬件上加載運行,則需用sparc-elf-gcc:進(jìn)行編譯,程序使用靜態(tài)鏈接庫完成鏈接。

④arm-linux-gcc:編譯器。ARM9的S3C2410編譯器為arm-linux-gcc。

⑤-O3優(yōu)化選項。LEON和ARM的微處理器通過指定該選項進(jìn)行程序算法優(yōu)化。

2.2測試項目及說明

測試項目1:整型數(shù)組與浮點數(shù)組的加法、乘法及乘加運算。每種類型的運算都循環(huán)50 000次,以驗證LEON各種平臺和ARM9的MCU在數(shù)學(xué)運算上的性能,并分析加入Linux系統(tǒng)后程序運行性能的變化。

測試項目2:單次濾波算法,程序每一次運行包含12 791次浮點乘法和13 595次浮點加法,以驗證在導(dǎo)航系統(tǒng)的濾波算法中LEON在多種配置下的性能。

測試程序采用clock()系統(tǒng)調(diào)用獲取算法開始運行和結(jié)束運行的時間,并以算法的運行時間作為衡量系統(tǒng)效能的唯一標(biāo)準(zhǔn)。

2.3測試總結(jié)

LEON平臺靈活的軟硬件配置在多項測試中表現(xiàn)優(yōu)異,總結(jié)如下:

①與主流ARM9微處理器在數(shù)學(xué)運算上性能相當(dāng)。

②嵌入式Linux操作系統(tǒng)平臺相對于無系統(tǒng)平臺有一定資源開銷,根據(jù)具體應(yīng)用合理選擇軟件平臺是否需要嵌入式Linux系統(tǒng)。

③指定-mv8和-03選項后程序性能提升顯著,根據(jù)具體應(yīng)用合理選擇是否配置整數(shù)硬件乘除法器。

④LEON硬件配置FPU后浮點運算性能提高一個數(shù)量級,代價是綜合需要的邏輯資源增長一倍,在權(quán)衡性能和可編程器件資源后合理選擇配置方案。

結(jié)合導(dǎo)航系統(tǒng)SoC芯片高速數(shù)據(jù)處理的需求,設(shè)計方案定型為LEON+FPU,在測試中能夠滿足系統(tǒng)的運算吞吐量指標(biāo)要求。

可配置FPU對LEON數(shù)學(xué)運算性能的提升極為有效,特別是在運算密集型的SoC設(shè)計中。LEON3的GRFPU相對于其他常見微處理器的FPU有較大優(yōu)勢。表2為若干處理器核FPU單元完成浮點運算指令需要的處理(延遲)時鐘周期數(shù)對比情況口。

時鐘周期數(shù)說明:括號外數(shù)字是指令處理周期數(shù),即硬件流水線中完成該指令的周期;括號內(nèi)數(shù)字是指令延遲周期數(shù),即該指令進(jìn)入流水線至從流水線中輸出結(jié)果所需要的時鐘周期數(shù)。

3 結(jié)論

作為硬件VHDL代碼開源的SPARC架構(gòu)軟核IP微處理器,LEONX(包括LEON2和LEON3)良好的可移植性和可配置性使其成為建立片上系統(tǒng)微處理器的一個優(yōu)選方案。采用Snapgear Embedded Linux的方案能夠提供一個從內(nèi)核、庫文件到常用應(yīng)用程序的驗證原型。然而,LEON硬件配置上的改變、升級需要驅(qū)動程序的支持,定制的軟件也需要自主開發(fā)。另外,在LEON平臺上移植并運行良好的實時操作系統(tǒng)有RTEMS和eCOS,根據(jù)實際的需求可以靈活選擇這些軟件開發(fā)平臺。

通過詳盡的對比測試,LEON軟核的性能優(yōu)異,在導(dǎo)航系統(tǒng)SoC芯片原型設(shè)計中得到驗證。測試為基于LEON開源可配置軟核的嵌入式系統(tǒng)開發(fā)的軟硬件配置方式提供了有益的參考,特別是集成浮點處理單元FPU的方案。隨著可編程器件規(guī)模的超大型化,實現(xiàn)高性能且配置靈活的開源SoC硬件系統(tǒng)及軟件平臺的優(yōu)勢日益明顯,為制造ASIC提供前期原型論證提供極大方便。

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19286瀏覽量

229813 -

soc

+關(guān)注

關(guān)注

38文章

4165瀏覽量

218244 -

微處理器

+關(guān)注

關(guān)注

11文章

2263瀏覽量

82444

發(fā)布評論請先 登錄

相關(guān)推薦

基于SOC/IP的智能傳感器設(shè)計研究

基于AVR 8位微處理器的FSPLC微處理器SOC設(shè)計

SoC驗證平臺的FPGA綜合怎么實現(xiàn)?

怎么設(shè)計集軟核處理器的嵌入式設(shè)計平臺?

學(xué)習(xí)RISC-V入門 基于RISC-V架構(gòu)的開源處理器及SoC研究

用LEON3開源軟核處理器怎么才可以設(shè)計一個動態(tài)圖像邊緣檢測

求一種基于FPGA的微處理器的IP的設(shè)計方法

如何構(gòu)建基于LEON開源軟核的SoC平臺?

基于IP復(fù)用設(shè)計的微處理器FSPLCSOC模塊

AEMB軟核處理器設(shè)計的SoC系統(tǒng)驗證平臺

LEON處理器結(jié)構(gòu)特點

基于LEON3開源軟核處理器的動態(tài)圖像邊緣檢測SoC設(shè)計

在FPGA中利用IP核實現(xiàn)SOC系統(tǒng)中的串口收發(fā)接口的設(shè)計

基于PowerPC 405微處理器和VME總線實現(xiàn)以太網(wǎng)接口設(shè)計

基于ARM微處理器的嵌入式TCP-IP協(xié)議的實現(xiàn)與應(yīng)用

基于LEON開源微處理器IP軟核實現(xiàn)SoC系統(tǒng)基本平臺的構(gòu)建

基于LEON開源微處理器IP軟核實現(xiàn)SoC系統(tǒng)基本平臺的構(gòu)建

評論