作者:符運生,陳雪,胡駿,王晨凌,劉冬

基于以太網的無源光網絡(EPON)是一種融合了以太網和無源光網絡(PON)優點的接入網技術,具有容量大、成本低、對IP業務支持好、技術成熟和維護簡單等優點,是未來實現FTTx的理想方案之一。目前EPON系統已在日本大規模應用,我國也有不少EPON系統投入商業應用。為使EPON能夠低成本、大規模地成功應用,不僅要求不同廠商的EPON光線路終端(OLT)和光網絡單元(ONU)設備能夠互通,而且需要方便有效地在EPON網絡開通前完成工程驗收,以及在EPON網絡運行過程中進行便捷的維護等。由于EPON點對多點的拓撲結構及其相應的上行時分多址接入(TDMA)方式,傳統的網絡測試設備都不能直接介入到EPON系統內部,只能通過EPON用戶側和網絡側接口進行相關測試,因此無法監測EPON內部運行狀況,不能對會影響互通的EPON相關協議進行測試分析。為此我們設計開發了EPON測試儀,以幫助運營商進行EPON組網前的設備互通測試和組網后的工程驗收和網絡維護。

1、系統簡介

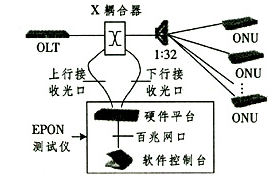

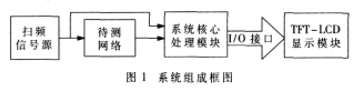

EPON采用單纖雙向通信方式,為了觀測EPON的內部運行情況,我們在OLT與光分配網絡(ODN)主干光纖之間接入X型光耦合器,分出部分上行和下行光信號至EPON測試儀,以實現對上下行鏈路的監視,如圖1所示。

圖1EPON測試儀介入被測網絡的方式

EPON測試儀由硬件平臺和配套的軟件控制臺兩大部分組成,其中硬件平臺負責EPON協議幀和相關數據的采集處理以及與軟件控制臺的通信,軟件控制臺負責EPON相關協議分析、提供用戶界面和對硬件平臺的配置管理等。本文著重闡述EPON測試儀硬件平臺的設計與實現。

2、硬件平臺功能需求分析

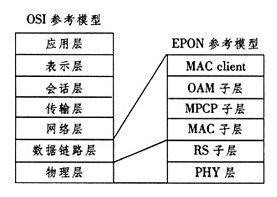

EPON測試儀主要關注影響EPON互通和運維的EPON調和(RS)子層、多點MAC控制(MPCP)子層和運行管理維護(OAM)子層。其中RS子層定義了EPON的前導碼格式,它在原以太網前導碼的基礎上引入了邏輯鏈路標識(LLID)區分OLT與各個ONU的邏輯連接,并增加了對前導碼的8位循環冗余校驗(CRC8);MPCP子層負責ONU到OLT的注冊、上行方向TDMA機制的運行等;OAM子層則負責有關EPON網絡運維的功能。EPON參考模型如圖2所示。

圖2EPON參考模型

EPON測試儀的主要功能有兩個:幫助發現影響互通的原因和方便EPON網絡的管理維護。前一個功能主要是指它可以幫助分析ONU的注冊過程是否符合標準、注冊成功后上層OAM消息的交互和業務的互通是否存在問題等;后一個功能主要是指它可為網絡維護人員提供在線ONU的基本信息和鏈路參數的統計數據,以方便運營者對網絡的管理和故障定位。

根據EPON測試儀的功能要求和我們對EPON測試儀硬件平臺和軟件控制臺的功能分割,確定EPON測試儀硬件平臺功能需求如下:

(1)提取ONU注冊過程所涉及的幀。

(2)按配置的過濾條件采集非注冊過程MPCP幀和OAM幀。針對EPON的特點,過濾條件可為LLID、幀的前64字節內用戶自定義的6字節長關鍵字,或二者的“與/或”組合。考慮到協議幀流量、送往軟件控制臺前的封裝開銷、與控制臺接口的速率限制和實現復雜度等因素,支持最多64個LLID過濾條件,和兩組用戶自定義關鍵字,關鍵字支持精確到比特的掩碼配置。

(3)對采集到的EPON協議幀(MPCP/OAM幀)打上本地時鐘標簽,并標明是來自EPON上行還是下行鏈路。

(4)EPON前導碼校驗的差錯率統計,支持統計使能和統計數據上報周期的配置。

(5)基于最多256個LLID,對前導碼正確的EPON幀的業務流量和幀校驗序列(FCS)校驗結果進行統計,支持統計使能和統計數據上報周期的配置。

(6)采集到的EPON協議幀和統計信息被封裝到以太網幀后通過百兆以太網接口送軟件控制臺分析。

(7)硬件平臺的配置內容由軟件控制臺通過百兆接口下達,配置內容包括EPON協議幀的過濾條件、鏈路統計項的使能和上報周期、EPON協議幀和統計信息被封裝到以太網幀時的源地址/目的地址/類型(DA/SA/type)字段等,硬件平臺應支持向軟件控制臺返回配置確認幀。

3、硬件平臺的設計實現

3.1硬件總體結構

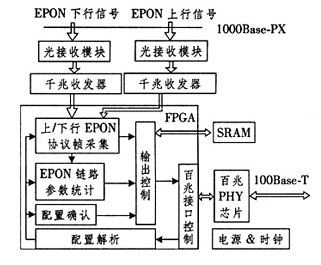

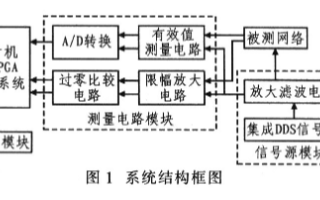

EPON測試儀硬件平臺的組成如圖3所示:

圖3EPON測試儀硬件平臺框圖

光接收模塊采用符合IEEE 802.3ah規范中1000Base-PX光接口要求的EPON光收發模塊,但只使用光接收部分。千兆以太網收發器芯片則采用商用芯片,它完成比特同步和串/并變換功能,然后將并行數據通過10比特接口(TBI)輸出給EPON測試儀核心功能現場可編程門陣列(FPGA)來處理。

核心功能FPGA完成底層硬件平臺的核心處理功能,包括EPON協議幀的采集、EPON鏈路參數統計和用戶配置等,綜合考慮這些功能對FPGA的資源需求、可擴展性和低成本要求,我們選擇的是Altera公司的stratix系列芯片。

百兆物理層(PHY)芯片采用的是VT6108S,它實現核心功能FPGA與軟件控制臺的接口功能。由于核心功能FPGA采集數據的峰值速率可達千兆速率,而輸出給控制臺時僅為百兆速率,故使用一個外部靜態存儲器(SRAM)實現輸出數據的緩存。

3.2核心功能的FPGA設計

3.2.1EPON協議幀的采集

圖4是上/下行協議幀采集框圖。千兆收發器芯片通過TBI接口將EPON上/下行鏈路的數據送給核心功能FPGA,FPGA以異步先入先出(FIFO)方式將接收到的數據同步到FPGA內部的125 MHz時鐘,然后進行8B/10B解碼,轉換為千兆比特媒質無關接口(GMII)格式的數據并恢復出各幀。

圖4上/下行協議幀采集框圖

經過EPON前導碼校驗和FCS校驗后,錯誤的幀將被丟棄。由于MPCP幀的type域為0x8808,OAM幀的type域為Ox8809,幀分類模塊據此篩選出MPCP/OAM幀送過濾模塊。

過濾模塊包括一個注冊過程提取模塊和一個用戶自定義過濾模塊。注冊過程提取模塊能夠根據LLID和幀內type/opcode字段篩選出所有的注冊過程幀,其余的幀送用戶自定義過濾模塊。用戶自定義過濾模塊支持按LLID過濾,或按用戶自定義幀內字段過濾,或按兩種過濾條件的“與/或”組合過濾,具體參數見硬件平臺功能需求分析。

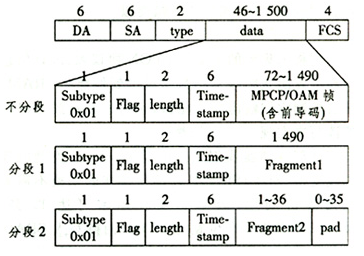

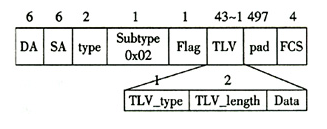

由于硬件平臺與軟件控制臺的接口為百兆以太網口,故采集到的EPON協議幀(含EPON前導碼)需要先封裝到以太網幀再輸出給軟件控制臺,封裝時應盡量反映EPON協議幀的原始信息,如采集時間、來自EPON上行方向還是下行方向等,這些分別在timestamp域和flag域中標識,另外考慮到EPON幀封裝到以太網幀后的長度可能會超過以太網的最大傳輸單元(MTU),長度大于1 490字節的EPON協議幀將被分為2段封裝,有關分段的信息也包含在flag域。封裝格式見圖5。其中在subtype域標明以太網幀的凈荷部分為EPON協議幀。

圖5EPON協議幀的封裝

3.2.2EPON鏈路參數統計

我們對反映EPON鏈路性能最為關鍵的3類信息:EPON前導碼CRC8校驗的差錯率、各LLID對應幀的FCS校驗差錯率和各LLID對應的業務流量信息,進行了統計上報。

基于用戶對幾類統計數據的關注程度不同,底層支持對各類統計的使能和上報周期控制,在上報周期到達時刻,統計信息將被打包輸出。為了在數據輸出時仍能進行統計,我們使用了兩套統計模塊,當一套需要輸出統計信息時,則切換到另一套進行參數統計。

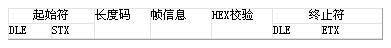

在EPON中,OAM消息均以TLV(Type Length Value)的格式承載,然后再被封裝到OAM幀中的data域,這種格式使得OAM消息具有很好的擴展性。在此我們借鑒了EPON OAM幀的封裝方式,統計數據將先被封裝到一個TLV中,在TLV頭部的type字段標明該TLV承載了哪類統計信息,通過length域標明該TLV的長度。在將TLV封裝到以太網幀時,仍使用了subtype字段來標識該以太網幀的凈荷部分為統計信息,flag域預留,封裝格式見圖6。

圖6統計信息的封裝格式

3.2.3配置解析

來自軟件控制臺的各種配置消息由配置解析模塊處理后,被送往相應模塊。用戶可配內容包括EPON協議幀的過濾條件、各鏈路統計項的使能和上報周期以及數據封裝到以太網幀時的DA/SA/type字段等。

考慮到與軟件控制臺的通信線路可靠性,當配置解析模塊收到一個沒有誤碼的配置消息后,它將產生一個包含該配置消息號和配置生效時間的確認幀告知控制臺,格式與統計幀類似。

3.2.4輸出控制

它將采集到的上下行EPON協議幀、統計信息幀和配置確認幀等幾路數據調度到外部的SRAM,然后控制它們輸出到百兆口,這通過對外部SRAM的讀寫來實現。

外部存儲器我們采用的是pipelined類型的零總線變換(ZBT)SRAM,其讀寫操作的切換不需要任何等待周期,因而總線利用率可達100%。SRAM的數據接口位寬為36 bit,而待寫入SRAM的各路數據位寬為9 bit(8 bit數據+1 bit幀包絡信息),這樣各路數據每4個時鐘分別往SRAM寫一次36 bit位寬數據即可實現線速存儲。為此將SRAM劃分為3個獨立的存儲區,并將讀寫時隙分配如下:第1個時鐘周期可往SRAM的存儲1區寫EPON上行協議幀,第2個時鐘周期可往SRAM的存儲2區寫EPON下行協議幀,第3個時鐘周期可往SRAM的存儲3區寫統計信息幀和配置確認幀,第4個時鐘周期可從SRAM讀出數據,從某一塊存儲區讀出完整一幀后即切換到讀另一塊存儲區。

3.3測試結果

我們在北京格林威爾科技發展有限公司的EPON系統上進行了實際測試。所研發的EPON測試儀能夠提取ONU注冊過程中涉及到的所有幀;當收到控制臺配置的過濾條件時,它將向控制臺返回一個確認消息,然后按照配置的過濾條件提取特定MPCP/OAM幀;可對幾類鏈路參數中的某一類或全部進行統計,并可獨立配置各類統計數據的上報周期;所有送往控制臺的數據均按設定格式封裝到以太網幀。此外我們還對EPON測試儀硬件平臺支持的參數進行了測試,測試結果表明,各項功能和性能指標均與設計要求相符。

4、結束語

本文說明了研究開發EPON測試儀的意義,簡要描述了其功能結構,并著重闡述了其硬件平臺的FPGA設計與實現。EPON測試儀可以有效地幫助網絡運營商進行設備互通測試、工程驗收和網絡運維等。

責任編輯:gt

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603387 -

以太網

+關注

關注

40文章

5425瀏覽量

171723

發布評論請先 登錄

相關推薦

基于FPGA的RS485接口誤碼測試儀的設計怎么實現?

求一種基于FPGA的誤碼率測試儀的方案

基于電路板維修測試儀軟件系統的實現

基于USB接口的通用測試儀的設計與實現

基于FPGA的新型誤碼測試儀的設計與實現

基于FPGA的高速誤碼測試儀的設計

數字電容測試儀實現方案

基于DDS和FPGA器件實現頻率特性測試儀的設計

基于51內核和FPGA器件實現便攜式幅頻特性測試儀的應用方案

基于FPGA器件實現EPON測試儀的應用設計

基于FPGA器件實現EPON測試儀的應用設計

評論