1. IBM GPM模型結構

隨著ASIC技術和工藝突飛猛進的發展,65/45nm工藝已成為當前設計的主流,高頻翻轉,沖擊電流求給ASIC后端版圖設計,封裝及系統設計帶來了前所未有的挑戰,信號完整性問題,以及往往被忽略的因芯片接口電路同時開關造成的同步開關噪聲(SSN),由于影響到其相臨邏輯器件的穩定和時序變得越來越關鍵。在芯片設計階段,需要對芯片的版圖布局、芯片封裝以及客戶板級信息進行建模和聯合仿真,才可以確保系統很好滿足整個系統性能的要求,提高設計的成功率。因此如何在物理設計前提供相對精確的仿真模型成為一個關鍵問題。

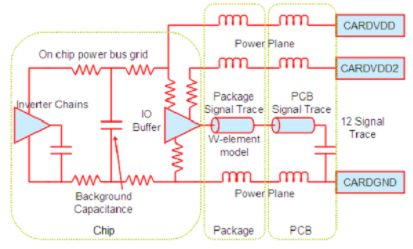

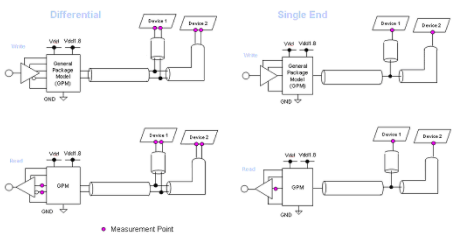

IBM在設計大規模芯片的過程中采用基于Hspice 語言建立的GPM(Generic Package Model)模型指導設計中的前仿與設計后驗證,它不僅包含封裝供電網絡和信號通路的模型,還包括芯片上的供電網絡、IO以及與芯片局部的SRAM、RA等邏輯電路和片上濾波電容(DECAP)的布局,另外客戶還可以加入實際的PCB負載模型與其連接組成完整的鏈路仿真模型。GPM模型的物理結構框圖如圖1所示。

圖1 IBM GPM物理結構框圖

其中,C4是用于連接芯片與封裝的焊球,Package VDD Supply是封裝上芯片內核供電網絡,Package VDD2 Supply是封裝上的IO供電網絡,而Package GND Supply是封裝上GND網絡,On-Chip VDD Bus, On-Chip VDD2 Bus, On-Chip Ground Bus則是芯片上相應供電網絡。對圖1所示各個部分建模,可以方便地得到GPM模型的電路結構(如圖2)。

IBM的芯片采用結構相對固定的電源網絡,設計初期可以對于電源網絡建模使用一套標準的RLC參數模型,并可以根據實際設計所采用的布局,對芯片和封裝的電源網路RLC參數進行修正。對于不同的尺寸的芯片與封裝設計,通過調節BGA與C4端相應的電源管腳比例可以實現在不改變基本模型結構的情況下,調整接入仿真模型RLC網絡的比例近而接近實際設計。對于板級負載,GPM模型里也會提供標準接口。

圖2 GPM模型電路結構

GPM模型具體由以下幾個部分組成:

1)芯片內部電源和地的電阻網絡;

2)芯片內部電源/地網絡,和布線層所產生的寄生電容;

3)用來模擬時鐘buffer、splitter、latches以及組合邏輯的反相器鏈路結構;

4)封裝信號線、過孔、焊球模型;

5)封裝電源/地平面、過孔、焊球模型;

6)連接在模型提取窗口內的器件電流模型

綜合考慮仿真速度與精度,作為局部仿真模型在90nm工藝下,一般芯片上提取窗口大小為800umX1200um。模型一般包含若干I/Os,信號線為有損傳輸線模型,信號線之間存在互感和互容,過孔、焊球等不連續性結構也采用RLC參數模型。

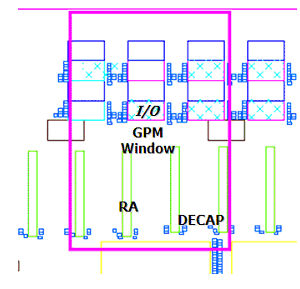

2. GPM模型的提取

GPM模型是一種基于SPICE的模型,由于門級仿真運算量即使可以抽取整個芯片的spice模型也無法完成仿真,因此在對芯片建模時只截取局部的信息,稱作GPM 窗口(如圖3)。根據芯片布局的實際情況,GPM窗口內可能會包含不同類型和數量的存儲器、IO、DECAP等器件,建模的時候會根據全局線性預分析(基于快速線形分析工具)結果選取噪聲最大的窗口進行分析,其往往集中于IO及翻轉的邏輯最多,而DECAP最少含有大動態功耗器件的區域。

圖3 GPM窗口

對于一般的邏輯電路,GPM模型使用一串反相器來模擬其翻轉情況,而對于SRAM或者RA等IP核的模擬,GPM模型使用了已經建好的簡化電流波形模擬這些IP核的翻轉,IO則使用了實際的SPICE模型進行仿真。

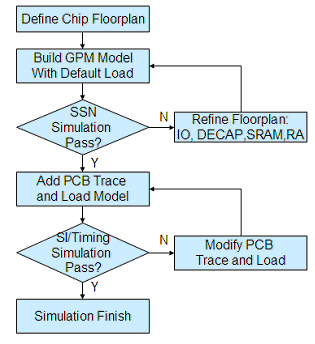

3. GPM仿真流程

GPM模型的建模和仿真具體實現過程如圖4所示。

圖4 GPM模型建模和仿真流程

芯片布局開始制定時,GPM的建模可以和物理設計同步進行,在IO的輸出端加載客戶負載模型進行SSN仿真,可以得出芯片上此切片電路的電氣數據(電壓,電流,抖動等)依此對電源去耦方案及布局進一步進行優化調整直到滿足設計要求。一旦布局確定,原來建立的GPM模型就可以交給客戶用實際的PCB負載模型替換默認的負載,并結合實際的應用環境對IO的信號質量、SSN和時序進行仿真,其結果可以幫助客戶在早期對系統的設計進行優化,使問題盡量被發現并在早期將其解決。

4. GPM模型在DDR2設計中的應用

4.1 IO buffer設置:

實際應用不同,創建GPM模型的拓撲結構也不一樣,不同的IO buffer模型將直接影響仿真的結果。本文使用IBM的BSSTL18DDR2(單端)和BSSTL18DDR2DIFF(差分)IO buffer構造DDR2接口電路。

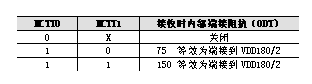

這兩種buffer都是雙向的,VDD操作電壓為1.1-1.3V, VDD180為1.65-1.95V,通常為1.8V。MCDHALF可以選擇驅動能力,當MCDHALF為“0”時,驅動為“Full”;當MCDHALF為“1”時,驅動為“Half”;MCTT0和MCTT1用來配置ODT,其真值表如表1所示:

表1 ODT控制信號設置

4.2 拓撲結構:

GPM模型能夠精確地對芯片內部包括封裝進行建模,也支持客戶加入PCB上引入的實際負載信息,同時拓撲結構也很方便修改。圖5中顯示的就是DDR2在“讀”操作和“寫”操作時DQS(差分)和DQ(單端)的拓撲結構。

圖5 GPM實際拓撲結構示意圖

當然PCB實際負載可以是S參數模型,也可以是W-Element模型。在仿真過程中,需要考慮實際系統中的各種非連續效應,如阻抗匹配問題,源端終端反射,線間耦合等。

4.3 同步開關噪聲(SSN):

GPM模型可以很好地支持對同步開關噪聲(SSN)進行分析,從而確定芯片布局時所加入的去耦電容是否足夠,最終的分析結果可以用來指導芯片的布局,通過增加去耦電容的數量,減少IO和邏輯的密度等方法來滿足芯片電源噪聲的要求,同時可以聯合PCB負載仿真得到板級去耦策略。

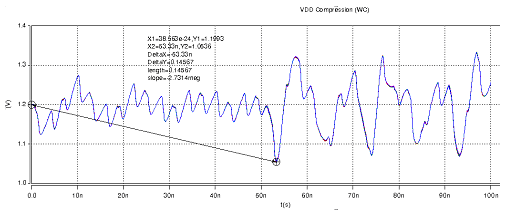

圖6 VDD電壓波形

圖6是用GPM模型仿真得到的芯片VDD的波形。波形中50ns到60ns之間的一個電壓低谷代表了IO同時開始翻轉的時刻,而疊加在整個波形中的紋波則體現了GPM窗口中除IO以外的其余邏輯電路翻轉對VDD的影響。在設計中需要保證最低電壓不低于電路所需的最低電壓,一般需滿足15%的紋波限制,根據不同的電壓域和IO類型,也會有所不同。

4.4 時序分析:

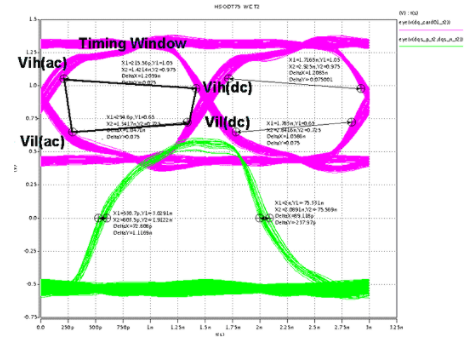

這里重點介紹利用GPM模型分析DQ與DQS之間的時序關系。在時序分析中最重要的就是通過分析建立時間(setup time)和保持時間(hold time)的裕量(margin)來評估系統的信號質量和穩定性。通常以有效時序窗口(Timing Window)概念來計算,所謂有效時序窗口,是指數據信號從發送端傳輸到接收端時,建立時間和保持時間的總和(如圖7),其取決于板級、封裝設計以及接口電路模式的選擇。

圖7 有效時序窗口--Timing Window

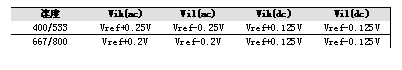

其中,JEDEC標準里規定了Vih(ac/dc)和Vil(ac/dc),如表2所示。

表2 Vih/Vil的ac和dc值

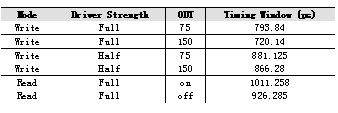

通過配置不同讀寫模式,驅動能力和片上端接電阻對有效時序窗口大小的分析,我們可以得到關于時序最優的解決方案。表3是用GPM模型對這幾種情況下分析的結果:

表3 各種情況下Timing Window

從表3可以看出,在“寫”的情況下,驅動能力為“Half”,ODT為75ohm端接時,時序有效窗口最大,相應的建立時間和保持時間的裕量最大;在“讀”的情況下,同是“Full”強驅動,打開ODT和關閉ODT也會有不同的效果,前者會更好。

5. 結論

1)本文通過實例介紹了基于GPM的DDR2高速接口的設計和仿真,接口信號完整性與封裝結構、芯片布局、IO類型、板級走線、驅動負載緊密相關,我們可以通過系統應用的實際需求進行設計和仿真。

2)由于GPM的建模對設計文件的依賴性較少,所以在進行芯片布局的同時就可以開始進行模型的建立和分析,對芯片的布局設計提供了很好的指導,并成為芯片電源噪聲的簽收標準之一。

3)GPM可以導入客戶的PCB互聯模型,用于對IO的時序和信號完整性進行分析。模型中包含了電源網絡的信息,仿真得到的結果也包含了SSN的信息,更加接近實際的應用環境。可以用于能指導ASIC的設計團隊完成IO的時序收斂,客戶PCB的系統設計。

4)GPM模型中IO的模型采用IBM自行研發的IO buffer的SPICE模型,對各種高速接口(如DDR2)的建模與仿真,可以達到非常高的精度。同時,GPM 仿真可以在設計初期對芯片、封裝和板級設計提供指導,從而極大的減少整個系統設計和驗證的周期。

責任編輯:gt

-

電源

+關注

關注

184文章

17809瀏覽量

251086 -

接口

+關注

關注

33文章

8675瀏覽量

151556 -

封裝

+關注

關注

127文章

7968瀏覽量

143190

發布評論請先 登錄

相關推薦

Altera DDR2仿真

采用Cyclone III FPGA實現DDR2接口設計

什么是DDR2 SDRAM

DDR2,DDR2是什么意思

DDR2 Layout指導手冊

基于FPGA的DDR2 SDRAM存儲器用戶接口設計

基于Xilinx的DDR2 SDRAM存儲控制器的用戶接口設計與仿真

MPC8379E與DDR2之間的PCB布線及仿真設計

Spartan-3的FPGA與DDR2 SDRAM的接口實現

基于GPM實現DDR2高速接口的應用設計和仿真

基于GPM實現DDR2高速接口的應用設計和仿真

評論