講一講Xilinx家的MIPI方案。這里以普通7系列作為討論的對象, X家高端的KU+/MPSOC+有已經(jīng)可以直接支持MIPI接口的IO了。

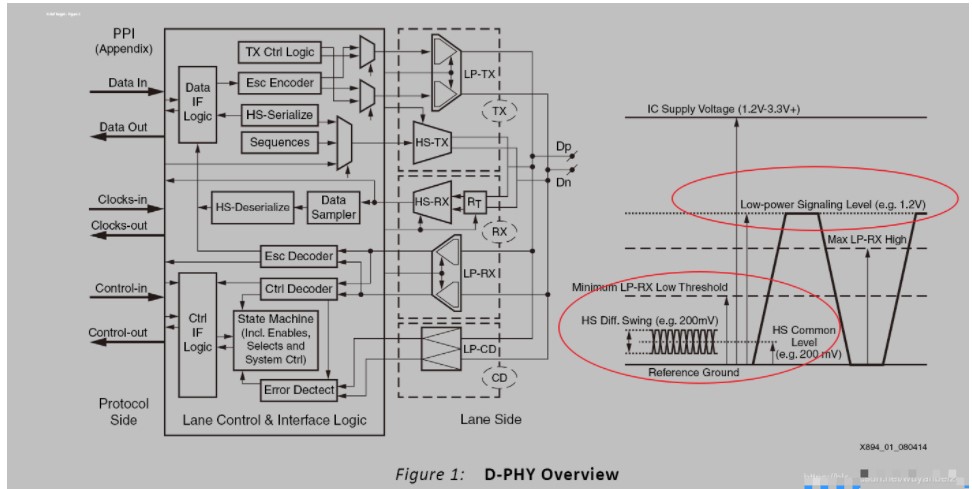

由于MIPI信號(hào)的比較特別,在設(shè)計(jì)之初應(yīng)該充分考慮了低功耗,所以MIPI原生的信號(hào)電平支持HS和LP模式,工作于不同的電平標(biāo)準(zhǔn):

從圖中可以 清楚的看到,MIPI電氣信號(hào)存在同時(shí)存在2個(gè)電平模式,如果接到FPGA的引腳上,很明顯FPGA是無法支持的。

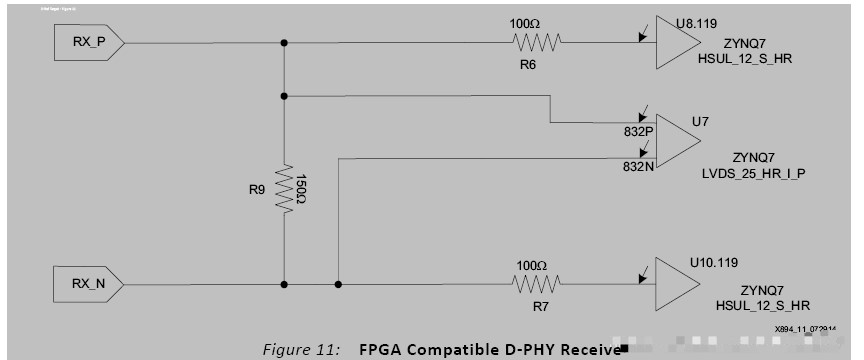

同時(shí),HS模式的電平標(biāo)準(zhǔn)FPGA也是不支持的。所以,Xilinx家給出了2種方案,實(shí)現(xiàn)MIPI信號(hào)電平的轉(zhuǎn)換,這個(gè)在文檔XAPP894中有詳細(xì)的介紹,下面只給出MIPI DPHY Rx部分 1電阻網(wǎng)絡(luò)

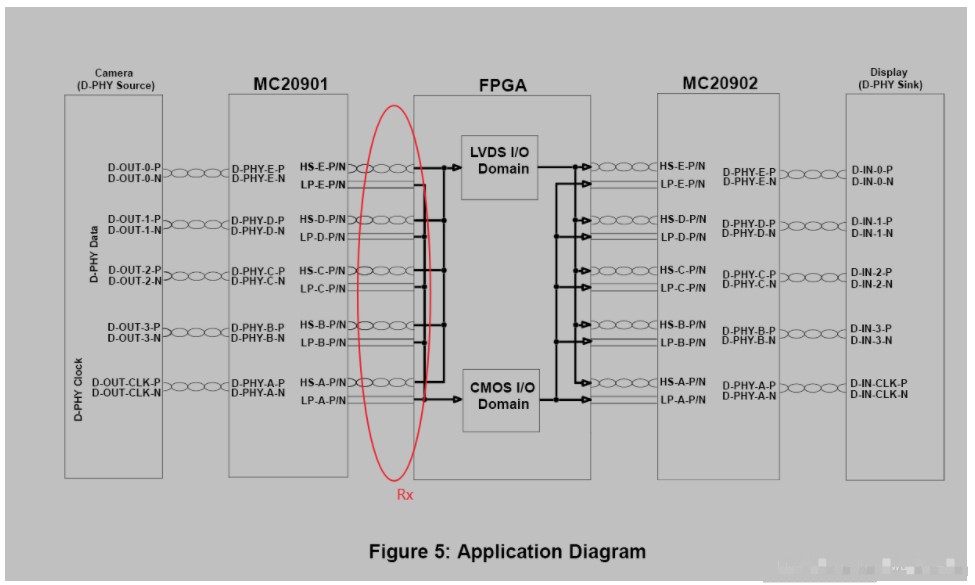

在MIPI線速率較高的情況下,不建議使用該方式。 2外部芯片 MC20901 在用于接收攝像頭時(shí),只需要用到MC20901即可

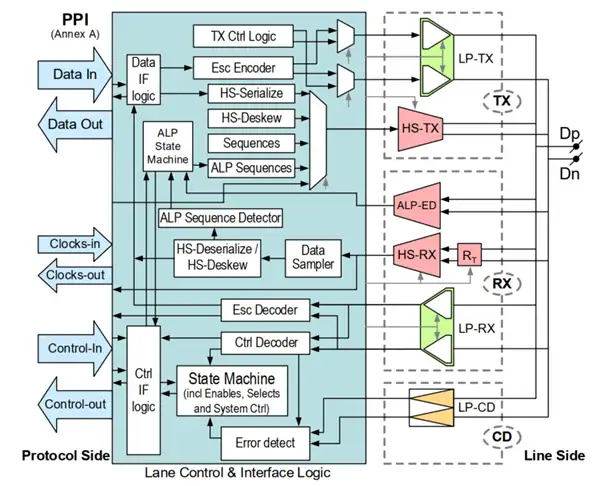

關(guān)于MIPI的調(diào)試 MIPI的調(diào)試前提是你正確的完成了sensor的配置,建議從網(wǎng)上或者FAE那里獲取一組已經(jīng)驗(yàn)證過的配置來驅(qū)動(dòng)sensor。這樣接下來調(diào)試的重心就可以放到MIPI部分。(補(bǔ)充說一句,高中生物我印象最深的一個(gè)概念就是:做實(shí)驗(yàn)要進(jìn)行變量控制,滿足單一變量的重復(fù)對比試驗(yàn)才能說明問提。然而工作中,很多時(shí)候出了問提定位都是胡亂猜) 由于使用的四Xilinx的MIPI RX Subsystem IP解決方案,所以用戶能配置的部分其實(shí)并不多。但是這個(gè)Subsystem內(nèi)部其實(shí)是2個(gè)IP構(gòu)成,一個(gè)是MIPI-DPHY,另外一個(gè)是MIPI-CSI2接口,然后兩個(gè)IP之間采用PPI接口互聯(lián)。MIPI DPHY通過接收比特流數(shù)據(jù),然后根據(jù)幀格式,恢復(fù)出packet。協(xié)議中對packet進(jìn)行了ECC校驗(yàn),具備一定的識(shí)別和糾正錯(cuò)誤的能力。但是如果信號(hào)質(zhì)量不好,出現(xiàn)的錯(cuò)誤較多,則會(huì)出現(xiàn)不可恢復(fù)的錯(cuò)誤,在圖像上顯示的就是時(shí)許不對導(dǎo)致的飛線,甚至花屏。

在綜合完成以后,打開綜合后的原理圖,進(jìn)入MIPI DPHY部分,對物理層后綴為err的信號(hào)進(jìn)行mark_debug,然后保存到xdc文件中用于后期的調(diào)試

從圖中可以看到xilinx 的MIPI IP PPI接口中 errorths信號(hào)拉高,說明存在行丟失的情況,出現(xiàn)該情況,如果物理層錯(cuò)誤信號(hào)不斷,再檢查完FPGA工程本身沒問題,則可以從硬件方面考慮是否存在問題。

責(zé)任編輯:lq6

-

Xilinx

+關(guān)注

關(guān)注

71文章

2168瀏覽量

121694 -

MIPI

+關(guān)注

關(guān)注

11文章

310瀏覽量

48682

原文標(biāo)題:Xilinx FPGA MIPI 接口簡單說明

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

直播報(bào)名丨第4講:AI檢測系統(tǒng)落地工具詳解

C語言數(shù)組應(yīng)用計(jì)算機(jī)導(dǎo)論A第6講:數(shù)組

直播報(bào)名丨第3講:如何選擇合適的算法模塊

直播報(bào)名丨第2講:熱門AI檢測案例解析

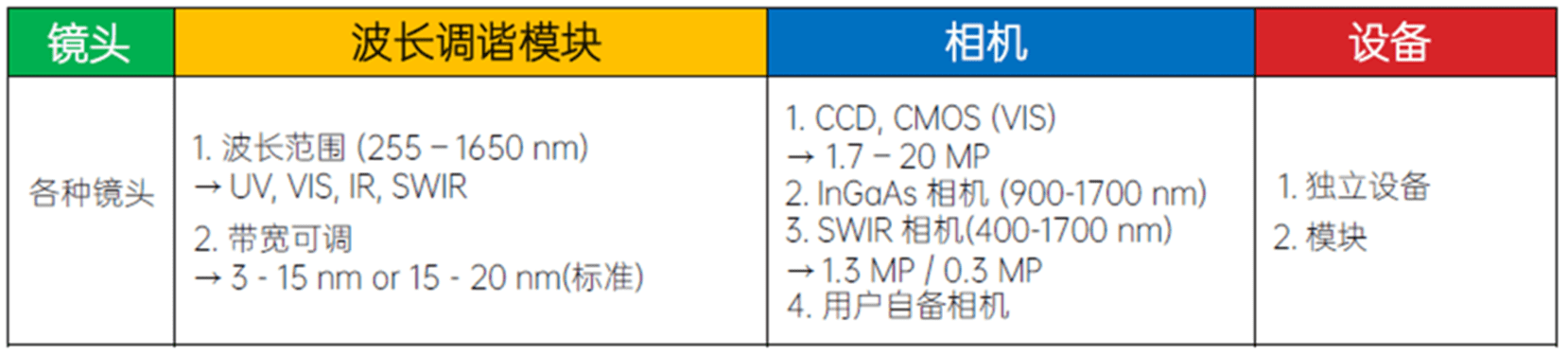

友思特“未來視界”趣味實(shí)驗(yàn)室 第2講:中草藥的高光譜成像

聚焦MIPI 系列之四:一文盤點(diǎn)D-PHY/C-PHY/M-PHY之架構(gòu)與測試解決方案

mipi顯示器接口多少引腳

mipi接口和edp接口可以轉(zhuǎn)換嗎?

EtherCAT轉(zhuǎn)Profinet網(wǎng)關(guān)配置說明第一講:配置軟件安裝及介紹

帶你了解雙端口MIPI、LVDS橋接到TYPE-C、DP 1.2或者EDP方案 內(nèi)置MCU 無需外掛單片機(jī)

第五講:51單片機(jī)+RA8889驅(qū)動(dòng)控制彩屏 完整源碼說明 【 源碼v1.2 】

5條DC-DC PCB layout建議

講一講Xilinx家的MIPI方案

講一講Xilinx家的MIPI方案

評(píng)論