集成電路芯片的測試(ICtest)分類包括:分為晶圓測試(wafertest)、芯片測試(chiptest)和封裝測試(packagetest)。

一般說來,是根據(jù)設(shè)計(jì)要求進(jìn)行測試,不符合設(shè)計(jì)要求的就是不合格。而設(shè)計(jì)要求,因產(chǎn)品不同而各不相同,有的IC需要測試大量的參數(shù),有的則只需要測試很少的參數(shù)。事實(shí)上,一個(gè)具體的IC,并不一定要經(jīng)歷上面提到的全部測試,而經(jīng)歷多道測試工序的IC,具體在哪個(gè)工序測試哪些參數(shù),也是有很多種變化的,這是一個(gè)復(fù)雜的系統(tǒng)工程。

IC的測試是IC生產(chǎn)流程中一個(gè)非常重要的環(huán)節(jié),在目前大多數(shù)的IC中,測試環(huán)節(jié)所占成本常常要占到總成本的1/4到一半。

芯片測試的過程是將封裝后的芯片置于各種環(huán)境下測試其電氣特性,如消耗功率、運(yùn)行速度、耐壓度等。經(jīng)測試后的芯片,依其電氣特性劃分為不同等級(jí)。而特殊測試則是根據(jù)客戶特殊需求的技術(shù)參數(shù),從相近參數(shù)規(guī)格、品種中拿出部分芯片,做有針對(duì)性的專門測試,看是否能滿足客戶的特殊需求,以決定是否須為客戶設(shè)計(jì)專用芯片。

芯片測試價(jià)格:

本文整合自 儀器網(wǎng)、百度愛采購

責(zé)任編輯:fqj

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

相關(guān)推薦

在芯片制造過程中,測試是非常重要的一環(huán),它確保了芯片的性能和質(zhì)量。芯片測試涉及到許多專業(yè)術(shù)語這其中,CP(Chip Probing),F(xiàn)T(

![的頭像]() 發(fā)表于

發(fā)表于 10-25 15:13

?404次閱讀

SOC(System on Chip,芯片上的系統(tǒng))芯片的測試是一個(gè)復(fù)雜且全面的過程,涉及多個(gè)參數(shù)和模塊。以下是對(duì)SOC芯片測試的主要參數(shù)和

![的頭像]() 發(fā)表于

發(fā)表于 09-23 10:13

?734次閱讀

測試芯片

博森源推拉力機(jī)

發(fā)布于 :2024年08月03日 17:59:50

本文就芯片測試做一個(gè)詳細(xì)介紹。芯片的測試大致可以分成兩大部分。CP(chipprobering)和FT(finaltest)。某些芯片還會(huì)進(jìn)

![的頭像]() 發(fā)表于

發(fā)表于 07-26 14:30

?2436次閱讀

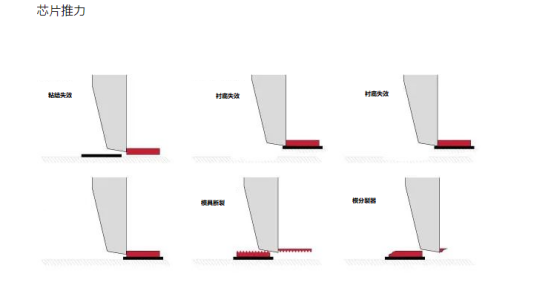

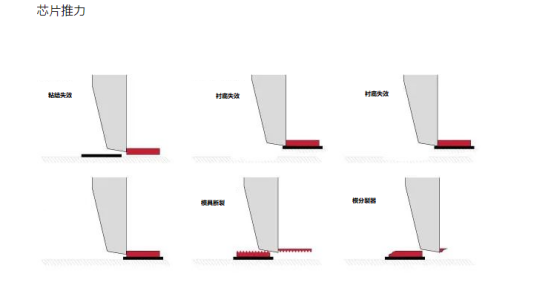

最近,小編收到了很多來自半導(dǎo)體行業(yè)客戶的咨詢,主要關(guān)于芯片推力測試的問題,他們想知道應(yīng)該采用何種設(shè)備和方法。為了滿足客戶的測試需求,科準(zhǔn)測試為其定制了一套技術(shù)方案,內(nèi)含操作步驟。 在半

![的頭像]() 發(fā)表于

發(fā)表于 05-15 16:55

?1037次閱讀

芯片測試作為芯片設(shè)計(jì)、生產(chǎn)、封裝、測試流程中的重要步驟,是使用特定儀器,通過對(duì)待測器件DUT(DeviceUnderTest)的檢測,區(qū)別缺

![的頭像]() 發(fā)表于

發(fā)表于 05-13 15:20

?567次閱讀

在測試準(zhǔn)備階段,需要對(duì)測試環(huán)境、測試數(shù)據(jù)和測試設(shè)備進(jìn)行準(zhǔn)備。同時(shí)需要對(duì)測試方案進(jìn)行評(píng)估和修訂,以確保測試

![的頭像]() 發(fā)表于

發(fā)表于 05-08 16:55

?876次閱讀

芯片測試的主要目的是確保芯片的質(zhì)量和可靠性,以及驗(yàn)證芯片的設(shè)計(jì)是否符合規(guī)范和要求。具體來說,測試可以檢測出

![的頭像]() 發(fā)表于

發(fā)表于 05-08 16:54

?1544次閱讀

在開始量產(chǎn)之前,芯片設(shè)計(jì)師會(huì)進(jìn)行設(shè)計(jì)驗(yàn)證,以確保芯片的設(shè)計(jì)滿足規(guī)格要求。這包括功能驗(yàn)證、時(shí)序驗(yàn)證和電氣驗(yàn)證等,確保芯片在理論設(shè)計(jì)上沒有問題。

![的頭像]() 發(fā)表于

發(fā)表于 05-08 16:52

?2151次閱讀

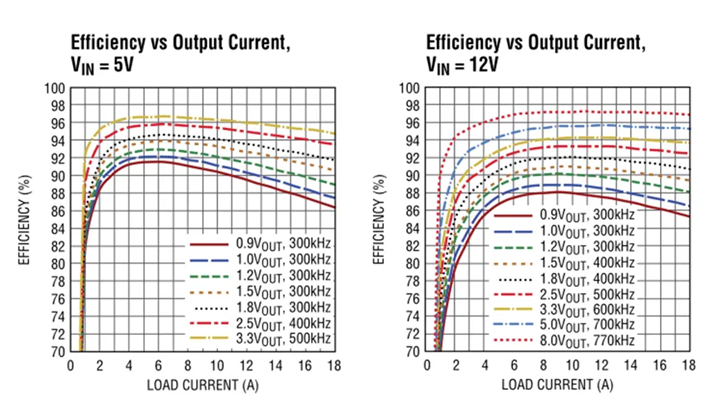

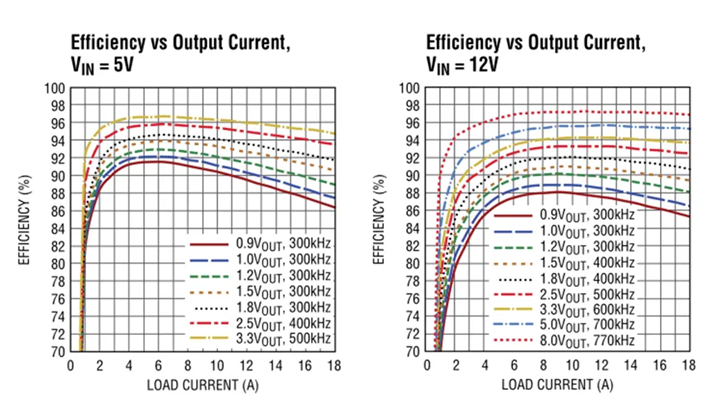

可通過檢測以下指標(biāo)參數(shù)來評(píng)估電源芯片的性能:輸入/出電壓范圍、輸出紋波、電壓調(diào)整率、負(fù)載調(diào)整率、反饋端電壓、欠壓關(guān)斷及欠壓恢復(fù)滯后、輸入偏置電流、輸出電流、輸出電流限制、啟動(dòng)過沖及啟動(dòng)延時(shí)、負(fù)載躍

![的頭像]() 發(fā)表于

發(fā)表于 05-06 14:20

?563次閱讀

封裝測試是將生產(chǎn)出來的合格晶圓進(jìn)行切割、焊線、塑封,使芯片電路與外部器件實(shí)現(xiàn)電氣連接,為芯片提供機(jī)械物理保護(hù),并利用測試工具,對(duì)封裝完的芯片

![的頭像]() 發(fā)表于

發(fā)表于 04-29 08:11

?2881次閱讀

芯片產(chǎn)線批量測試,不僅耗時(shí)長、無法規(guī)范測試流程、保證測試可靠性,而且無法進(jìn)行數(shù)據(jù)統(tǒng)一管理、滿足產(chǎn)線測試

![的頭像]() 發(fā)表于

發(fā)表于 04-23 13:47

?496次閱讀

隨著集成電路技術(shù)的飛速發(fā)展,芯片作為現(xiàn)代電子設(shè)備的核心組件,其性能和質(zhì)量對(duì)于整個(gè)系統(tǒng)的穩(wěn)定性和可靠性具有至關(guān)重要的影響。因此,在芯片生產(chǎn)過程中,出廠測試和ATE(自動(dòng)測試設(shè)備)

![的頭像]() 發(fā)表于

發(fā)表于 04-19 10:31

?1959次閱讀

WAT需要標(biāo)注出測試未通過的裸片(die),只需要封裝測試通過的die。

FT是測試已經(jīng)封裝好的芯片(chip),不合格品檢出。WAT和FT很多項(xiàng)目是重復(fù)的,F(xiàn)T多一些功能性

發(fā)表于 04-17 11:37

?830次閱讀

集成芯片測試好壞的方法主要包括以下幾個(gè)步驟。

![的頭像]() 發(fā)表于

發(fā)表于 03-19 16:52

?1328次閱讀

芯片測試流程 芯片測試價(jià)格

芯片測試流程 芯片測試價(jià)格

評(píng)論