OPA0基準(zhǔn)模式

OPA0基準(zhǔn)模式OPA0支持OPA和基準(zhǔn)兩種工作模式,在OPA模式下,OPA0是一個普通的三端運(yùn)算放大器。

SYNWIT

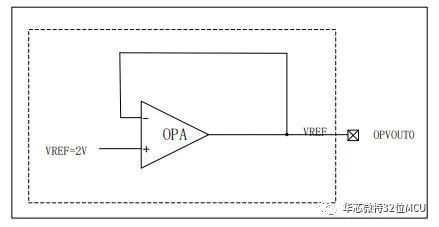

在基準(zhǔn)模式下,OPA0為OPA1和OPA2PGA模式提供基準(zhǔn),此時OPA0不可用于放大器,此模式下提供的VREF2V的基準(zhǔn)電壓輸出到OPVOUT0管腳上,OPAOUT0管腳不可作為其他的功能引腳使用,可通過配置OPACR寄存器中OPA0MD和OPA0ON位配置。

圖1-1丨OPA0 基準(zhǔn)模式內(nèi)部結(jié)構(gòu)圖

1

PGA功能OPAx支持OPA和PGA兩種工作模式,在OPA模式下,OPA0、OPA1、OPA2是一個普通的三端運(yùn)算放大器。

2

在PGA模式下,使用OPA1和OPA2時需配置OPA0為基準(zhǔn)模式,此時OPA0是一個正端接內(nèi)部2V基準(zhǔn)的電壓跟隨器,可通過內(nèi)部連接,為PGA模式下的OPA1/OPA2提供電壓基準(zhǔn),此電壓基準(zhǔn)會直接輸出至OPAOUT0腳,不需要配置或切換外部引腳,此時OPA0只能作為VREF的電壓跟隨器使用,輸出2V的電壓,其內(nèi)部結(jié)構(gòu)圖如圖1-1所示。

3

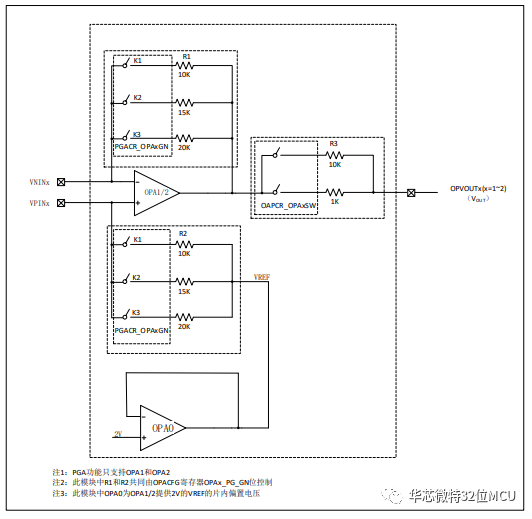

在PGA模式下,OPA1和OPA2是一個通過選擇內(nèi)置反饋電阻(10k、15k、20k)選擇增益倍數(shù)的可編程增益放大器,支持3種增益選項。

OPA1和OPA2其內(nèi)部結(jié)構(gòu)圖如圖1-2所示。

圖1-2丨OPA1/OPA2 PGA 內(nèi)部結(jié)構(gòu)圖

程序中配置如下(雙電阻采樣配置模式)

static void OPA_Init(void)

{

SYS-》ACMPCR |= (1 《《 SYS_ACMPCR_CMP0MD_Pos);

SYS-》ACMPCR |= (1 《《 SYS_ACMPCR_CMP1MD_Pos);

SYS-》ACMPCR |= (1 《《 SYS_ACMPCR_CMP2MD_Pos);

//首先將OPA0、OPA1和OPA2進(jìn)行OPA模式初始化

SYS-》OPACR |= (1 《《 SYS_OPACR_OPA0MD_Pos);

//設(shè)置OPA0為電壓基準(zhǔn)模式:OPA0 Mode, 0 OPA 1 PGA

SYS-》PGACR &= ~(1 《《 SYS_PGACR_OPA0VR_Pos);

//設(shè)置OPA0的電壓基準(zhǔn):0 2.0V 、1 2.01V 、2 1.99V 、3 1.98V

//OPA1

PORT_Init(PORTA, PIN10, PORTA_PIN10_OPA1_INN, 0);

PORT_Init(PORTA, PIN9, PORTA_PIN9_OPA1_INP, 0);

//OPA1輸入引腳初始化

SYS-》OPACR |= (1 《《 SYS_OPACR_OPA1MD_Pos);

//設(shè)置OPA1為PGA模式:0 OPA 1 PGA

SYS-》PGACR |= (1 《《 SYS_PGACR_OPA1GN_Pos);

//PGA模式下 OPA1增益反饋電阻選擇:0 10K 1 15K 2 20K

SYS-》PGACR |= (1 《《 SYS_PGACR_OPA1SW_Pos);

// PGA模式下OPA1輸出濾波電阻選擇:0 1K 1 10K

//OPA2

PORT_Init(PORTB, PIN8, PORTB_PIN8_OPA2_INN, 0);

PORT_Init(PORTB, PIN7, PORTB_PIN7_OPA2_INP, 0);

//OPA2輸入引腳初始化

SYS-》OPACR |= (1 《《 SYS_OPACR_OPA2MD_Pos);

//設(shè)置OPA2為PGA模式:0 OPA 1 PGA

SYS-》PGACR |= (1 《《 SYS_PGACR_OPA2GN_Pos);

//PGA模式下 OPA2增益反饋電阻選擇:0 10K 1 15K 2 20K

SYS-》PGACR |= (1 《《 SYS_PGACR_OPA2SW_Pos);

// PGA模式下OPA2輸出濾波電阻選擇:0 1K 1 10K

SYS-》OPACR |= (1 《《 SYS_OPACR_OPA0ON_Pos);

SYS-》OPACR |= (1 《《 SYS_OPACR_OPA1ON_Pos);

SYS-》OPACR |= (1 《《 SYS_OPACR_OPA2ON_Pos);

//OPA0、OPA1和OPA2開啟

}

*******

芯片存在OPAxOUT引腳部分沒有引出(內(nèi)部已經(jīng)連接),特注釋:OPA1OUT對應(yīng)管腳為A8,請使用ADC0_CH7進(jìn)行采樣;OPA2OUT對應(yīng)管腳為B9,請使用ADC0_CH8進(jìn)行采樣。

編輯:jq

-

引腳

+關(guān)注

關(guān)注

16文章

1207瀏覽量

50725

原文標(biāo)題:SWM20x系列電機(jī)框架搭建:OPA(PGA)篇

文章出處:【微信號:gh_ed4f95bde4df,微信公眾號:華芯微特32位MCU】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

ADS1256基準(zhǔn)輸入端振蕩的原因?

ADS1281開發(fā)板上的OPA1632和基準(zhǔn)源的疑問求解答

關(guān)于DAC60501內(nèi)部基準(zhǔn)電壓VREFIO的問題求解

關(guān)于數(shù)據(jù)轉(zhuǎn)換器的基準(zhǔn)電壓選擇和設(shè)計提示

關(guān)于\"OPA615\"的SOTA的跨導(dǎo)大小的疑問求解

求助,關(guān)于OPA551的輸出電壓問題求解

使用OPA735反向電路將+2.500V基準(zhǔn)電壓輸出-2.5V基準(zhǔn)電壓,為什么會有鋸齒電壓紋波?

求助,關(guān)于OPA445帶寬問題求解

用OPA310來提高驅(qū)動能力時,使用電壓跟隨的方法和使用基準(zhǔn)緩沖的方法有什么區(qū)別?

關(guān)于定位系統(tǒng)技術(shù)你知道多少?

OPA727.OPA2727,OPA4727.OPA728運(yùn)算放大器數(shù)據(jù)表

關(guān)于OPA0基準(zhǔn)模式你知道多少?

關(guān)于OPA0基準(zhǔn)模式你知道多少?

評論