在先前的文章中《近距離看GPU計算(2)》,我們談到GPU相比CPU有更大的內存帶寬,此言不虛,這也是眾核GPU有源源不斷數據彈藥供給,能夠發揮強大算力的主要原因。基本上GPU的內存帶寬要比CPU多一個數量級。

但是考慮到GPU運算核心的數量,平均下來顯存帶寬真的足夠富裕嗎?參考資料1的《Memory bandwidth》文章提供了很有趣的視角,我們在這里介紹下。MOS 6502發布于1975年,是微型計算機發展史上非常重要的一塊芯片。

6502一般運行在1M時鐘頻率,每個時鐘可以訪問1Byte內存數據,6502的一條指令需要花費3~5個時鐘,所以平均下來每條指令大概可以獲得4B內存數據。

與此相對照,Intel的Corei7-7700K是一款目前比較主流的桌面CPU,運行頻率4.2G,內存帶寬大概50GB/s。i7-7700K一共有4個處理核心,所以每個核心大概可以均攤到12.5GB/s的內存帶寬,也就是每個時鐘可以訪問約3B的內存數據。

該CPU的IPC(Instruction Per Clock)為1,極優化的代碼可以達到的IPC為3,按此計,每條指令可得1B的內存數據,跟老前輩6502相比,已經落后不少。

更進一步,現代CPU支持256位長度的SIMD指令,每個時鐘最多執行3條指令,類比GPU,我們以32位為一個通道作為單獨執行線程,這樣每個時鐘我們一共有24條指令執行,所以每條指令可以訪問0.125B內存數據或者說每8條指令得到1B內存數據。

我們再回過頭來看看GPU的情形。以NVidiaGeForce GTX 1080Ti為例,內存帶寬484GB/s,處理單元工作頻率為1.48G,所以對整個GPU來說,每個時鐘大概可以訪問327B內存數據。這個GPU一共有28個SM(類似CPU的處理核心),每個SM有128個SP,所以總共有3584個SP(類似先前SIMD32位通道)。

這樣每個SM一個時鐘大概可以訪問11.7B的內存數據,平均到128個SP,一個SP一個時鐘得到0.09B數據,換個好聽的說法就是每11條指令可以得到1B內存數據,比CPU的指標還惡劣。需要再次重申的是,因為設計目標的問題,CPU其實更關注訪存延遲指標,所以相形之下,內存帶寬的壓力對GPU更為顯著。

這也是為什么我們先前說過的GPU也開始配置多級Cache的原因,除了改善訪存延遲,也可以降低內存帶寬壓力。另外我們在《GPU歷史之二三事》里也提到Nvidia和AMD都開始擁抱移動GPU常用的TBR(Tile Based Rendering)的繪制技術,內存帶寬的壓力也應該是重要的驅動因素。

而作為軟件人員,在設計算法的時候,我們要重視算法的運算強度(見《Roofline模型初步》),要充分利用片上內存包括硬件Cache和軟件Cache(Shared Memory),以及注意內存的合并訪問(Memory Coalescing)等等來優化內存帶寬。

主要參考資料:

https://fgiesen.wordpress.com/2017/04/11/memory-bandwidth/

編輯:jq

-

gpu

+關注

關注

28文章

4740瀏覽量

128951

原文標題:再談GPU的內存帶寬

文章出處:【微信號:gh_6fde77c41971,微信公眾號:FPGA干貨】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

南亞科技與補丁科技攜手開發定制超高帶寬內存

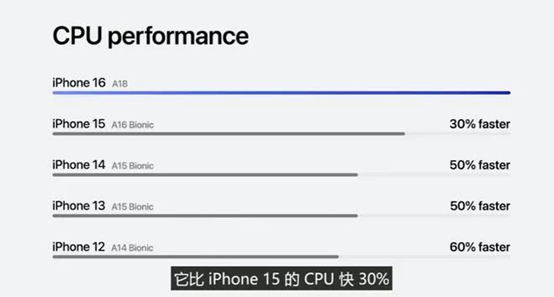

蘋果 A18 芯片發布:CPU 提升 30%、GPU 提升 40%

主板內存故障燈亮會是cpu的問題嗎

主板自檢cpu和內存燈一直來回閃

X-Silicon發布RISC-V新架構 實現CPU/GPU一體化

RISC-V芯片新突破:CPU與GPU一體化核心設計

GPU竟比CPU有更大的內存帶寬

GPU竟比CPU有更大的內存帶寬

評論