Vivado提供了三種封裝IP的方式:(1)將當前工程封裝為IP;(2)將當前工程中的BD(IPI 設計)封裝為IP;(3)將指定的文件目錄封裝為IP。

IP Packager支持的輸入文件HDL綜合文件;HDL仿真文件;說明文檔;HDL測試平臺;例子工程;約束文件;驅動;GUI定制文件;BD文件可以看到這里沒有.dcp文件,所以設計中如果包含.dcp文件,那么是無法封裝為IP的。

IP Packager輸出文件component.xml文件;用于定制IP界面的.tcl文件(位于封裝IP指定目錄下的xgui文件夾下);其他在封裝IP時用戶指定包含的文件。

IP Packager對頂層文件的要求IP Packager要求設計頂層必須是VHDL或Verilog文件。如果當前設計頂層為SystemVerilog,要先將其封裝為Verilog或VHDL文件。 IP Packager對約束的要求IP Packager支持三種約束文件:

(1)用于綜合和布局布線階段的.xdc;

(2)僅用于布局布線階段的.xdc;

(3)僅用于OOC(Out-of-context)綜合的.xdc 默認情形下,。

創建工程后調用IP,然后對IP采用OOC的綜合方式,此時就會用到僅用于OOC綜合的.xdc。在這個約束文件里,通常會包含時鐘周期約束(create_clock創建的約束)。建議在封裝IP時,要提供此約束文件。可將文件以“xx_ooc.xdc”的方式命名,同時設置其USED_IN的屬性值為out_of_context。其實,Vivado IPCatalog自帶的IP在生成時都會看到一個《ip_name》_ooc.xdc的約束文件。

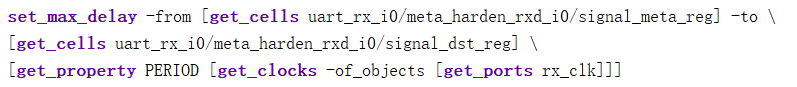

如果設計中有其他約束依賴于create_clock創建的約束,如下圖所示,set_max_delay創建約束時需要用到時鐘周期PERIOD,此時應將這類約束單獨寫在一個.xdc文件里,并將其PROCESSING_ORDER值設置為LATE。這將表明該約束文件里的約束依賴于外部約束,其實就是頂層約束文件。

編輯:jq

-

IP

+關注

關注

5文章

1708瀏覽量

149554 -

vhdl

+關注

關注

30文章

817瀏覽量

128139 -

GUI

+關注

關注

3文章

660瀏覽量

39681

原文標題:Vivado下封裝IP基本知識

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

三種封裝形式下的400G光模塊概述

systemd journal收集日志的三種方式

Windows管理內存的三種主要方式

常用的pwm跟蹤控制方式是哪三種

計算機網絡中的三種通信方式

簡述斬波電路的三種控制方式

差分晶振的輸出波形解析:三種類型要知道

介紹三種建模方式

通過TestStand三種主要運行方式探究TestStand開放式架構

一文解析Vivado的三種封裝IP的方式

一文解析Vivado的三種封裝IP的方式

評論