引言:本文我們介紹FPGA外設DDR2/DDR3硬件設計相關內(nèi)容,包括PCB板層數(shù)估計,信號端接、信號完整性及時序考慮等問題。

1.介紹

Artix-7和Spartan-7器件有各種各樣的軟件包,它們的設計都是為了獲得最大的性能和最大的靈活性。Spartan-7 FPGA封裝體積小,封裝尺寸從8mm到27mm不等,而Artix-7 FPGA封裝尺寸從10mm到35mm不等。包裝的間距分別為1.0mm、0.8mm和0.5mm。包間距定義為BGA包上連續(xù)球之間的距離,從中心到中心測量,如圖1所示。 一般來說,隨著間距的減小,PCB布線的挑戰(zhàn)增加,因為在封裝球之間布線和通孔的空間變小了。

2.層計數(shù)估算和成本權衡

圖2中公式給出了扇出全部FPGA管腳所需的FPGA層疊數(shù)。

對于Xilinx 成本優(yōu)化的FPGA,信號引腳的數(shù)量約為BGA球總數(shù)的60%。另外40%包括電源和接地信號,這些信號通常通過過孔直接連接到參考層。這是假定I/O利用率已滿。如果使用較少的I/O,則布線的信號層數(shù)相應減少。

Routing Channels:是出BGA的可用布線路徑的總數(shù),例如,(一側(cè)的BGA球數(shù)–1)× 四面。圖3顯示了5×5 BGA封裝,總計16個布線路徑,即:

一側(cè)BGA球數(shù) = 5,布線路徑 =(5-1)× 4 = 16。

每個布線路徑的布線通常是一個或兩個,這取決于可以在頂層/底層的BGA焊盤之間走線的數(shù)量。從信號完整性的角度來看,遵守面向制造的設計(DFM)指南對于確保滿足走線阻抗要求至關重要。圖4顯示了每個通道布線的示意圖。內(nèi)層上每個通道的布線取決于通孔之間的間距,并考慮到鉆至覆銅的規(guī)格要求。 對于間距為0.5mm的封裝,焊盤尺寸和封裝間距尺寸將PCB設計者限制為BGA焊盤之間的單個跡線。然而,當選擇0.8mm或1mm間距的封裝時,PCB設計師可以靈活地選擇單跟走線或兩根走線。 在高密度BGA下扇出信號時要考慮的關鍵因素包括:

外層焊盤的尺寸

通孔的尺寸和相應的焊盤/反焊盤尺寸

走線寬度和間距要求

可用的信號層數(shù)量

PCB設計師在布局期間可用的參數(shù)主要由封裝間距決定。為降低PCB制造成本,PCB設計人員除了使用更細的寬度外,還可以使用諸如微通孔、盲孔和埋入通孔等先進制造技術。然而,這些先進的制造技術并不是確保DDR3設計成功的必要條件。下圖4是各種行業(yè)術語的簡要說明,以及適用于標準PCB制造成本的近似值。

通孔縱橫比:PCB厚度與最小通孔鉆孔直徑之比。這是用來作為指導,以確保PCB制造商不超過機械能力的鉆孔設備。通孔縱橫比為10:1在標準PCB制造中相當常見。通過使用先進的PCB制造技術,在保持面向制造的設計(DFM)規(guī)則的同時,通孔縱橫比可以增加到20:1。

背鉆孔過孔:背面鉆孔過孔是一種通孔,其部分長度“鉆出”使其不再導電。這提高了信號完整性,因為它從路由中刪除了不需要的stub。典型的背鉆孔成本增加為PCB總制造成本的5-10%。焊盤中的通孔:焊盤中的通孔是直接鉆在焊盤下方的通孔。這樣就不需要使用單獨的金屬跡線(桁條)來放下通孔。這有助于突破布線和改善信號完整性,PCB制造成本會增加+10–15%,取決于通孔縱橫比。埋孔和盲孔:埋孔完全位于印刷電路板內(nèi)部,不接觸頂層或底層;盲孔從頂層或底層傳輸?shù)絻?nèi)部信號層。兩種類型的過孔都為其他布線在上方或下方騰出空間。這與通孔不同,通孔從頂層一直通到底層。埋孔或盲孔的成本增加取決于PCB上不同類型的埋孔或盲孔的數(shù)量。每種類型的埋入/盲孔都需要單獨的層壓循環(huán),從而產(chǎn)生額外的成本。例如,在16層PCB上具有三種不同類型的埋置/盲孔(L1–L4、L16–L12、L4–L8)會導致每種類型的埋置/盲孔增加30%的成本。微通孔:微通孔是盲孔的一種形式。微通孔的尺寸非常小。它們是用激光形成的,通常一次不能穿透超過一到兩層。對于每種類型的通孔,成本增加約為15%。額外層:添加額外信號層的成本可能低于上述一些高級via技術的成本。因此,增加PCB層數(shù)不應總是被視為消極的選擇。兩個附加層的成本通常使PCB制造成本增加15–20%。 通過先進的制造工藝,PCB設計師可以指定窄至2.5mil、間距為2.5mil的走線,以實現(xiàn)最佳SI性能的目標阻抗規(guī)格。

3.低成本DDR3設計指南

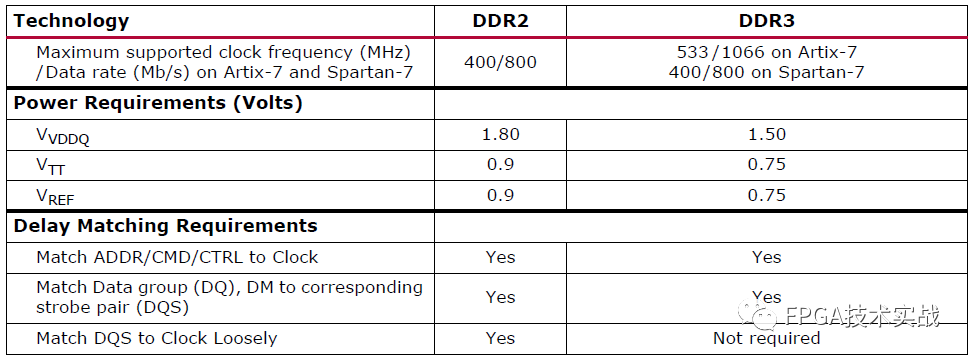

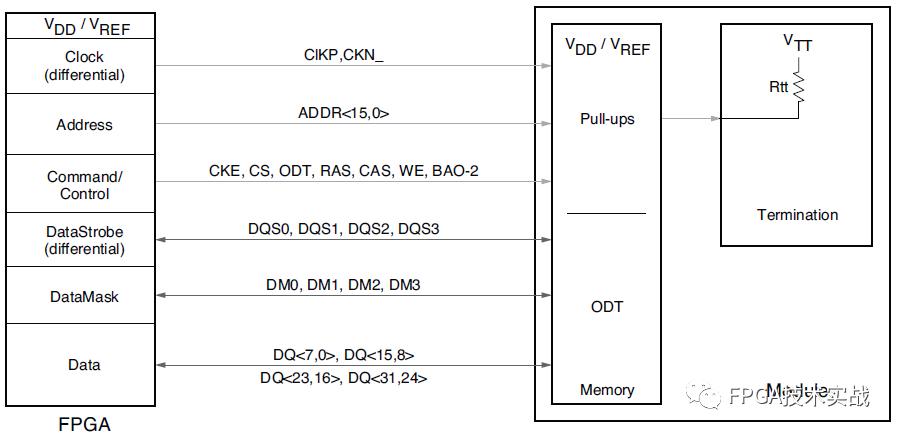

根據(jù)系統(tǒng)要求,DDR2/3內(nèi)存作為一組離散SDRAM或DIMM模塊連接到Artix-7和Spartan-7 FPGA。并非這些產(chǎn)品系列中的所有器件都支持所有可能的內(nèi)存配置。支持的確切內(nèi)存配置取決于特定的芯片/封裝組合。 無論拓撲結(jié)構(gòu)如何,DDR2/3接口能否以盡可能高的數(shù)據(jù)速率成功運行取決于驅(qū)動器和接收器緩沖器、終端、互連阻抗、延遲匹配、串擾和電源完整性。兩種內(nèi)存類型的一般比較如表3所示,而DDR2和DDR3共用的信號如圖6所示。

表3、DDR2和DDR3內(nèi)存要求比較

圖6、DDR2和DDR3內(nèi)存通用的體系結(jié)構(gòu)和接口技術 本節(jié)提供了實現(xiàn)低成本PCB設計的高級布局指南。成功的內(nèi)存布局面臨的關鍵挑戰(zhàn)是:

在最少的路由層上扇出所有數(shù)據(jù)和地址信號

通過最小化串擾、阻抗不連續(xù)引起的信號反射等,確保可靠的信號完整性。

4.信號完整性

DQ、DM、DQS網(wǎng)絡通常是點對點連接。這些網(wǎng)絡是雙向的,數(shù)據(jù)鎖存在其相關數(shù)據(jù)選通信號的上升沿和下降沿上。Xilinx建議如下:

選擇輸出阻抗最接近傳輸線阻抗的FPGA驅(qū)動器設置

從FPGA到存儲設備的PCB上的特性阻抗使用50Ω

在DRAM上啟用最接近50Ω的片上終端(ODT)設置,以最小化寫操作期間的反射

在讀取操作期間啟用FPGA端接,以確保雙向高數(shù)據(jù)速率操作的匹配端接

為了盡量減少串擾,建議在換層期間將信號間距盡量加大并盡量減少通孔stub長度。然而,F(xiàn)PGA和DRAM器件下的面積受到空間的限制,很難將信號間距加大。為了簡化PCB布局,Xilinx允許最小間距,即在扇出區(qū)域中為1X間距。1X間距是指走線之間的距離,等于走線寬度。當扇出FPGA/DRAM器件時,只要走線長度小于1in,就可以保持這種間距。為進一步確保可靠的信號完整性,還必須遵循以下準則:

扇出BGA器件區(qū)域后,走線間距保持2X間距或更大間距。

使用FR4型基板,從FPGA到DRAM的PCB互連總長度不大于4英寸。

時鐘、地址、命令和控制信號時鐘、ADDR(地址)、CMD(命令)和控制信號通常是點對多點連接,需要一種稱為Fly-by的獨特拓撲結(jié)構(gòu)。這些信號是單向的,從FPGA驅(qū)動到存儲器設備。差分時鐘時序信號分析的參考信號。外部端接ODT不適用于這些網(wǎng)絡,需要外部離散終端。推薦的形式通常是在遠端放置一個電阻器,經(jīng)過最后一個存儲設備,然后拉到VTT(VVDDQ/2)。上拉電阻器的值和互連線路的阻抗取決于網(wǎng)絡上的設備數(shù)量。這些值通常通過模擬進行優(yōu)化。 對于低成本設計,Xilinx建議遵循以下準則。

Xilinx建議使用50Ω 特性阻抗端接電阻到遠端的VTT(VDDQ/2)。這適用于大多數(shù)情況。

對于CLK差分對,建議實現(xiàn)100Ω 的差分阻抗,使用兩個單獨的50Ω 上拉電阻VDDQ和電容器。

圖8顯示了VTT電容器的布置。為確保可靠的電源完整性,Xilinx建議每四個終端電阻至少放置一個0.1μF電容與VTT相連。

此外,Xilinx建議將DRAM之間的互連長度和從最后一個DRAM到端接電阻的stub長度保持在0.75in以內(nèi)。5.信號網(wǎng)的延遲匹配雖然走線長度、阻抗和終端可以確保信號完整性,確保同步網(wǎng)絡之間的延遲匹配同樣重要。字節(jié)通道中的所有DQ和DM網(wǎng)絡必須與其關聯(lián)的DQS網(wǎng)絡相匹配。Xilinx建議如下:

所有DQ/DM網(wǎng)絡應與其相關的DQS網(wǎng)絡匹配,對于800Mb/s的DDR2/DDR3接口,走線時延保持±15ps

所有DQ/DM網(wǎng)絡應與其相關的DQS網(wǎng)絡匹配,對于1066Mb/s的DDR2/DDR3接口,走線時延保持±15ps

對于單向信號,所有ADDR/CMD/CTRL信號必須與CLK信號匹配。它是一個很好的設計實踐,匹配每個傳輸線段(FPGA到DRAM1,F(xiàn)PGA到DRAM1)DRAM2、FPGA Fly-By端電阻等)在合理公差范圍內(nèi)±25ps。

6.結(jié)論

Xilinx Artix-7和Spartan-7器件可以分別以1066Mb/s和800Mb/s的速度與DDR2/3進行互操作。本文的目的是為使用先進制造技術的層數(shù)估計和成本影響提供指導。此外,本文還提出了低成本PCB設計的高層次布局準則,有助于優(yōu)化I/O性能,降低性能的風險。

責任編輯:haq

-

FPGA

+關注

關注

1629文章

21746瀏覽量

603753 -

pcb

+關注

關注

4319文章

23108瀏覽量

398183 -

DDR

+關注

關注

11文章

712瀏覽量

65368

原文標題:Artix-7 and Spartan-7 FPGAs DDR2/DDR3 PCB設計指導

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

DDR3、DDR4、DDR5的性能對比

如何選擇DDR內(nèi)存條 DDR3與DDR4內(nèi)存區(qū)別

在DSP上實現(xiàn)DDR2 PCB布局布線

基于FPGA的DDR3多端口讀寫存儲管理設計

華邦傾力挺進DDR3市場,抓住轉(zhuǎn)單商機

XC7K410T-FFG900外設之DDR3硬件設計方案分享

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數(shù)據(jù)表

完整DDR,DDR2,DDR3 和LPDDR3 存儲器電源解決方案同步降壓控制器數(shù)據(jù)表

具有同步降壓控制器、2A LDO和緩沖基準的完整DDR2、DDR3和DDR3L存儲器電源解決方案TPS51216-EP數(shù)據(jù)表

完整的DDR2、DDR3和DDR3L內(nèi)存電源解決方案同步降壓控制器TPS51216數(shù)據(jù)表

適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準的TPS51206 2A峰值灌電流/拉電流DDR終端穩(wěn)壓器數(shù)據(jù)表

具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數(shù)據(jù)表

具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內(nèi)存電源解決方案數(shù)據(jù)表

完整的DDR、DDR2和DDR3內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)表

FPGA外設DDR2/DDR3硬件設計相關內(nèi)容

FPGA外設DDR2/DDR3硬件設計相關內(nèi)容

評論