Vivado調(diào)用Questa Sim或ModelSim仿真中存在的一些自動化問題的解決方案。

Vivado調(diào)用Questa Sim仿真中存在的一些問題

首先說明一下Modelsim與Questa Sim都可以與Vivado聯(lián)調(diào),也比較相似,但是Questa Sim比Modelsim功能更加廣泛,對于System Verilog的語法支持更加完善,本文以Questa Sim為例說明一下Vivado調(diào)用第三方仿真軟件查看波形的過程中存在的一些問題。

1、添加新的觀測信號需要重新仿真

Vivado直接調(diào)用Modelsim/QuestaSim進行仿真時,波形文件里默認只會出現(xiàn)仿真最頂層中包含的信號,若此時將仿真運行一段時間后,想要查看其他模塊信號波形時,需要重新仿真或者運行do XXX_simulate.do方可。

在這個工程中,我們調(diào)用Questa Sim進行仿真,可以看到頂層模塊會自動跑100ns。

此時,我們?nèi)粝氩榭磍_ethernet_0_pkt_gen_mon這個模塊的波形時,直接進入波形界面進行添加,結(jié)果如圖3所示。

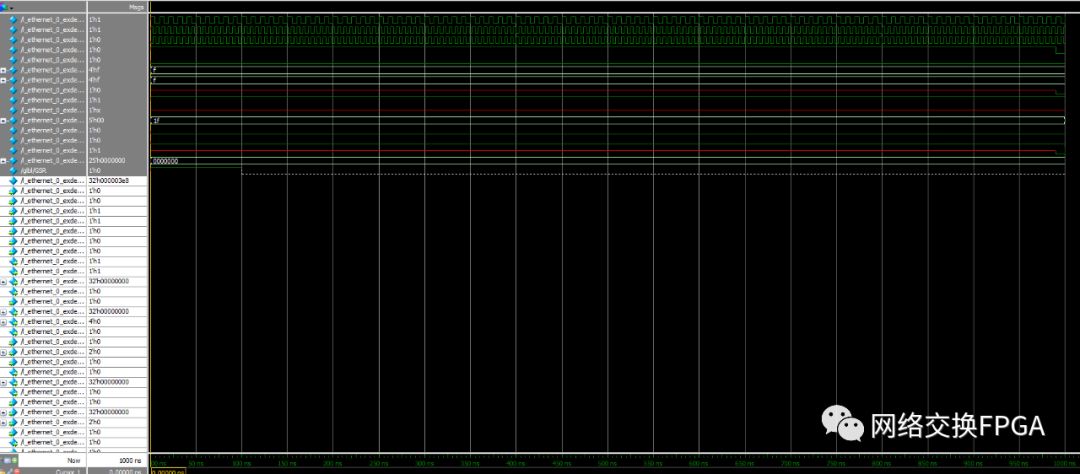

圖3 QuestaSim仿真波形

從圖3中可以看到,當(dāng)模塊的信號被添加進來后,已經(jīng)運行過的仿真時間內(nèi),新加入的信號沒有仿真結(jié)果。

2、修改邏輯代碼后,需要重新調(diào)用仿真器

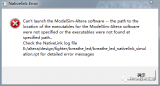

在代碼調(diào)試過程中,修改部分邏輯代碼后(不包括IP核),如果想要查看修改后工程的仿真結(jié)果,需要關(guān)閉當(dāng)前的仿真器,從vivado中重新調(diào)用方可。其原因是vivado在生成XXX_compile.do文件時,會在其末尾自動添加“quit -force”語句,而更改了相應(yīng)的代碼文件后,我們需要執(zhí)行“do XXX_compile.do”命令重新編碼整個庫,然而在運行此文件時,當(dāng)前的仿真器會被強制退出。

解決方案

為了解決上述問題,同時更加方便使用,本文使用TCL語言,編寫了一個較為方便的do文件,其可以實現(xiàn)如下功能:

1、對XXX_compile.do自動修改

對XXX_compile.do自動修改,去除其末尾的“quit -force”,并生成新的compile.do文件,其對應(yīng)的源代碼如下:

set filename [glob *_compile.do]

set content [open $filename r+]

set row 0while {![eof $content]} {

incr row

gets $content line

set list($row) $line

}

close $contentset filename2 “compile.do”;

set content [open $filename2 w+]

for {set i 1} {$i 《= $row} {incr i} {

if {![string match “quit -force” $list($i)]} {

puts $content $list($i)

}

};

close $content

2、使用“l(fā)og -r /*”命令

該命令可以讓modelsim/Questa Sim在進行仿真中,對所有信號同步進行仿真,從而解決新加入的觀測信號沒有仿真結(jié)果的問題;

3、保證仿真器不退出

當(dāng)修改工程中的邏輯代碼(不含IP核)后,只需要運行該do文件,其自動進行編譯和仿真,且使用修改后的compile.do文件,保證仿真器不退出,其對應(yīng)的源代碼如下:

set filename compile.do

do $filenameset filename [glob *_simulate.do]

do $filenamelog -r /*

restart -force

run 1ms

例程

在使用該do文件之前,需要首先通過vivado調(diào)用modelsim/ questasim,然后將do文件拷貝到工程對應(yīng)的behave文件夾下。仍以工程為例,當(dāng)修改了代碼內(nèi)部分邏輯后,在QuestaSim的transcrip界面,輸入命令do auto_update_sim.do即可自動重新編譯、仿真,結(jié)果如圖4所示(默認仿真時間設(shè)置為1ms)

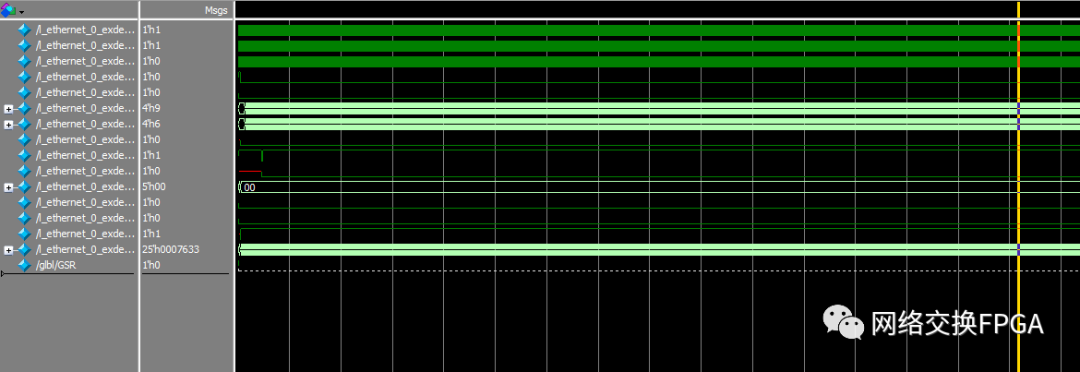

圖4 QuestaSim仿真波形

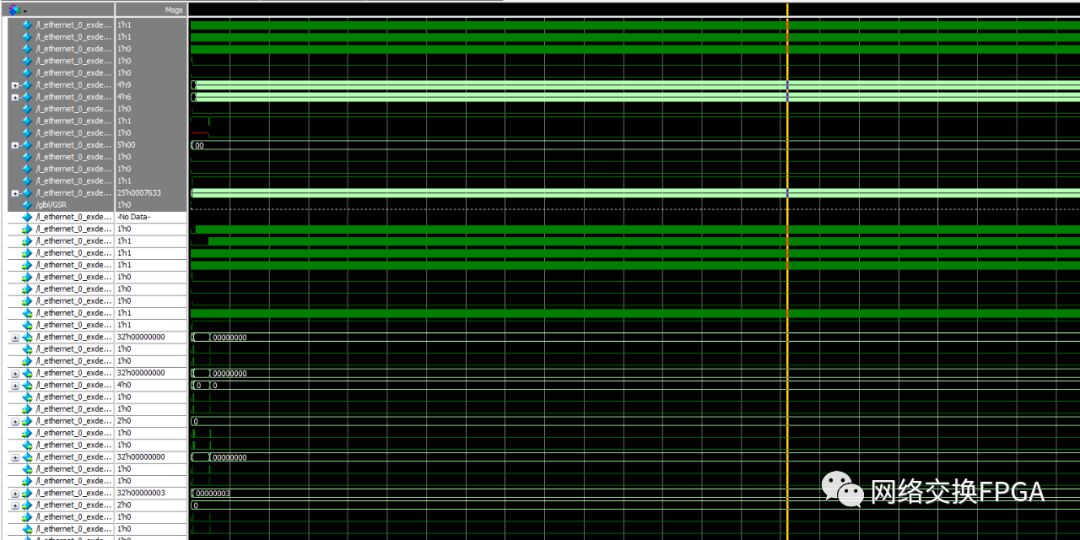

添加了l_ethernet_0_pkt_gen_mon這個模塊,可以發(fā)現(xiàn)仿真過的時間內(nèi)同樣有仿真結(jié)果,如圖5所示。

圖5 QuestaSim仿真波形

完整源碼

set filename [glob *_compile.do]

set content [open $filename r+]

set row 0while {![eof $content]} {

incr row

gets $content line

set list($row) $line

}

close $contentset filename2 “compile.do”;

set content [open $filename2 w+]

for {set i 1} {$i 《= $row} {incr i} {

if {![string match “quit -force” $list($i)]} {

puts $content $list($i)

}

};

close $content

set filename compile.do

do $filename

set filename [glob *_simulate.do]

do $filename

log -r /*

restart –force

run 1ms

編輯:jq

-

IP

+關(guān)注

關(guān)注

5文章

1708瀏覽量

149547 -

仿真器

+關(guān)注

關(guān)注

14文章

1018瀏覽量

83744 -

代碼

+關(guān)注

關(guān)注

30文章

4788瀏覽量

68612 -

Vivado

+關(guān)注

關(guān)注

19文章

812瀏覽量

66537

原文標題:[源碼]Vivado調(diào)用Questa Sim仿真小技巧

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

使用modelsim時的問題分析

Efinity FIFO IP仿真問題 -v1

如何在ModelSim中添加Xilinx仿真庫

Vivado 使用Simulink設(shè)計FIR濾波器

ISE 關(guān)聯(lián) Modelsim 詳細操作

最實用的Modelsim使用教程

fpga仿真文件怎么寫

ADS調(diào)用spectre網(wǎng)表仿真異常—薛定諤的NetlistInclude

最實用的Modelsim使用及仿真的基本步驟

Vivado調(diào)用Questa Sim或ModelSim仿真小技巧

Vivado調(diào)用Questa Sim或ModelSim仿真小技巧

評論