Versal 自適應(yīng)計(jì)算加速平臺(tái) (ACAP) 將標(biāo)量引擎 (Scalar Engine)、自適應(yīng)引擎 (Adaptable Engine) 和智能引擎(Intelligent Engine) 與領(lǐng)先的存儲(chǔ)器和交互技術(shù)有機(jī)結(jié)合,從而為任何應(yīng)用提供強(qiáng)大的異構(gòu)加速功能。Versal 架構(gòu) PCB 準(zhǔn)則已基于前幾代進(jìn)行了精簡(jiǎn),以方便 PCB 布局專(zhuān)業(yè)人員和硬件設(shè)計(jì)師使用。

Versal ACAP 中的配電系統(tǒng)

Versal ACAP 包含多條電源軌,每條電源軌都用于一項(xiàng)特定功能,如下表所示。如需了解有關(guān)電源名稱(chēng)和電壓電平的最新信息,請(qǐng)參閱《Versal AI Core 系列數(shù)據(jù)手冊(cè):DC 和 AC 開(kāi)關(guān)特性》。

向下滑動(dòng)查看Versal ACAP 主電源

適用于存儲(chǔ)器接口的 PCB 準(zhǔn)則

Versal 架構(gòu)提供了與以下存儲(chǔ)器架構(gòu)連接的解決方案:

? DDR4

? LPDDR4/4x

? RLDRAM3

? QDR-IV

所有接口的必需存儲(chǔ)器布線準(zhǔn)則:

1

判定信號(hào)走線長(zhǎng)度時(shí),請(qǐng)?jiān)诓季€約束中包含封裝延遲,除非另行指定。

2

相同字節(jié)組中的 DQ 和 DQS 信號(hào)應(yīng)在相同層級(jí)內(nèi)從 Versal 器件布線到 DRAM/DIMM。按適當(dāng)方式在字節(jié)組內(nèi)包含數(shù)據(jù)掩碼 (DM)。

3

對(duì)于多插槽拓?fù)浣Y(jié)構(gòu),從一個(gè) DIMM 布線到另一個(gè) DIMM 時(shí),請(qǐng)勿更改層級(jí)。

4

信號(hào)線必須布線于實(shí)體基準(zhǔn)內(nèi)電層上。請(qǐng)勿在空隙處布線,如下圖所示。

實(shí)體基準(zhǔn)內(nèi)電層上的信號(hào)布線

5

請(qǐng)勿在基準(zhǔn)內(nèi)電層分割處布線,如下圖所示。

基準(zhǔn)內(nèi)電層分割處的信號(hào)布線

6

請(qǐng)將布線置于距離基準(zhǔn)內(nèi)電層和空隙邊緣至少 30 mil 外,但引出線區(qū)域除外。

引出線區(qū)域布線

7

對(duì)于雙插槽 DIMM 拓?fù)浣Y(jié)構(gòu),應(yīng)將 DIMM #0 布局在離 ACAP 最遠(yuǎn)的連接器上,以降低 SI 反射的影響。DIMM#1 連接器應(yīng)布局在離 ACAP 最近的地方。

8

對(duì)于使用地址鏡像的蛤殼式配置,應(yīng)確保兩條芯片選擇線路的終端均充分去耦,并且進(jìn)出 VTT 的電層/走線厚度足夠。

Versal 器件與封裝之間的移植

封裝移植的高層次目標(biāo)是確保客戶(hù)能夠在任一管腳兼容封裝內(nèi)跨不同器件使用相同 PCB。封裝移植中存在嚴(yán)格的移植設(shè)計(jì)規(guī)則,當(dāng)前提供的大部分封裝都支持在任一給定 Versal 產(chǎn)品組合內(nèi)進(jìn)行跨器件移植。但也有跨不同器件系列的封裝可提供移植支持。

? VSVA2197 和 VSVD1760:支持在 Versal AI Core 系列與 Prime 系列內(nèi)進(jìn)行跨器件移植

? VFVF1760 和 VFVC2197:支持在 Versal Prime 系列與 Premium 系列內(nèi)進(jìn)行跨器件移植

責(zé)任編輯:haq

-

電源

+關(guān)注

關(guān)注

184文章

17732瀏覽量

250442 -

pcb

+關(guān)注

關(guān)注

4319文章

23108瀏覽量

398183 -

ACAP

+關(guān)注

關(guān)注

1文章

54瀏覽量

8171

原文標(biāo)題:用戶(hù)指南 | Versal ACAP PCB設(shè)計(jì)

文章出處:【微信號(hào):FPGA-EETrend,微信公眾號(hào):FPGA開(kāi)發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AMD推出第二代Versal Premium系列

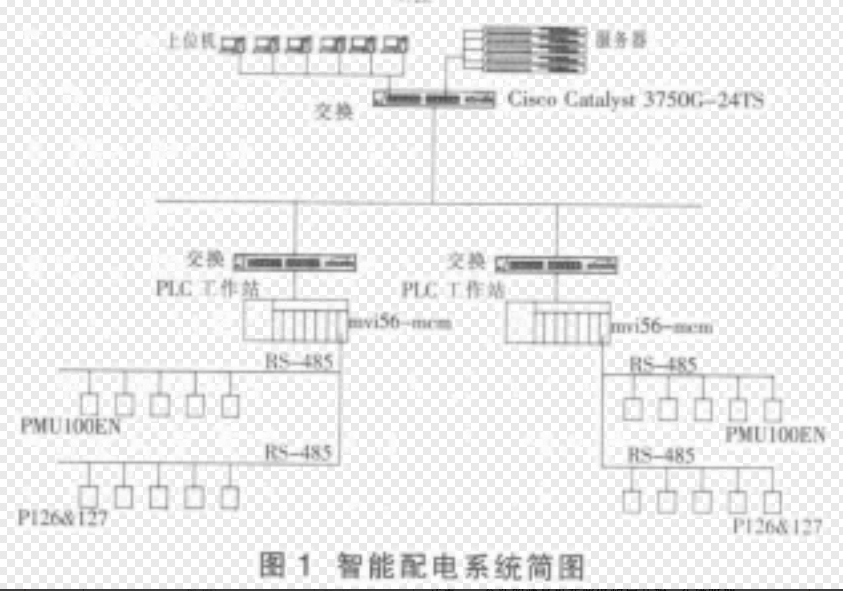

多電量數(shù)字變送器在現(xiàn)代配電系統(tǒng)中的應(yīng)用

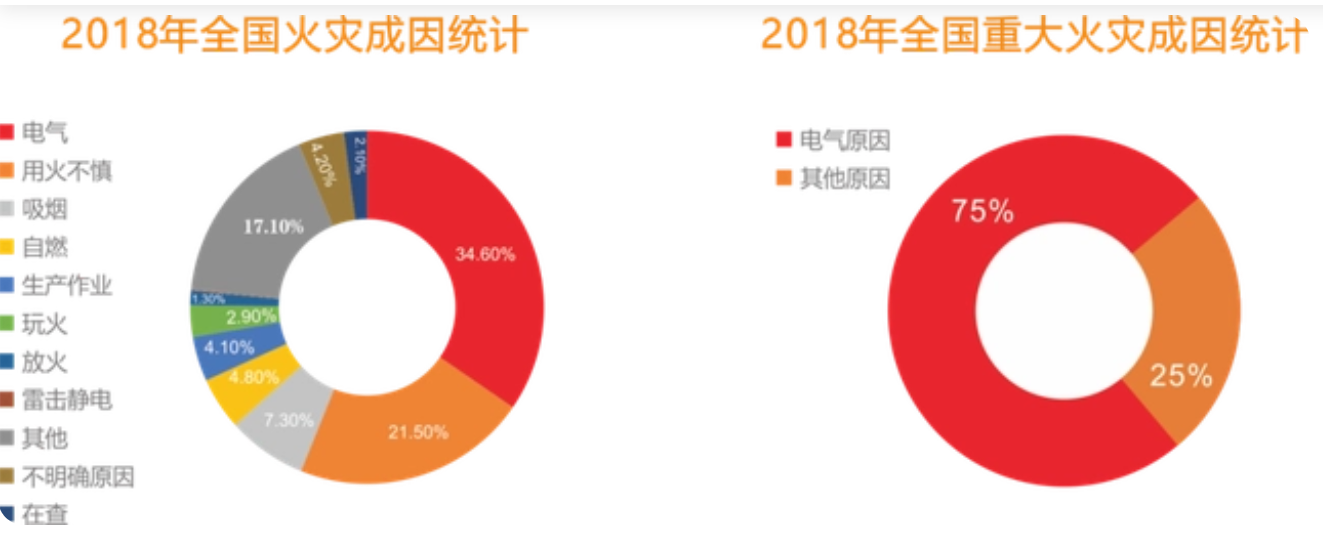

現(xiàn)代配電系統(tǒng)中電弧光保護(hù)裝置的應(yīng)用

供配電系統(tǒng)中的PT柜的作用

什么是高壓配電系統(tǒng)?如何實(shí)現(xiàn)?

ALINX VERSAL SOM產(chǎn)品介紹

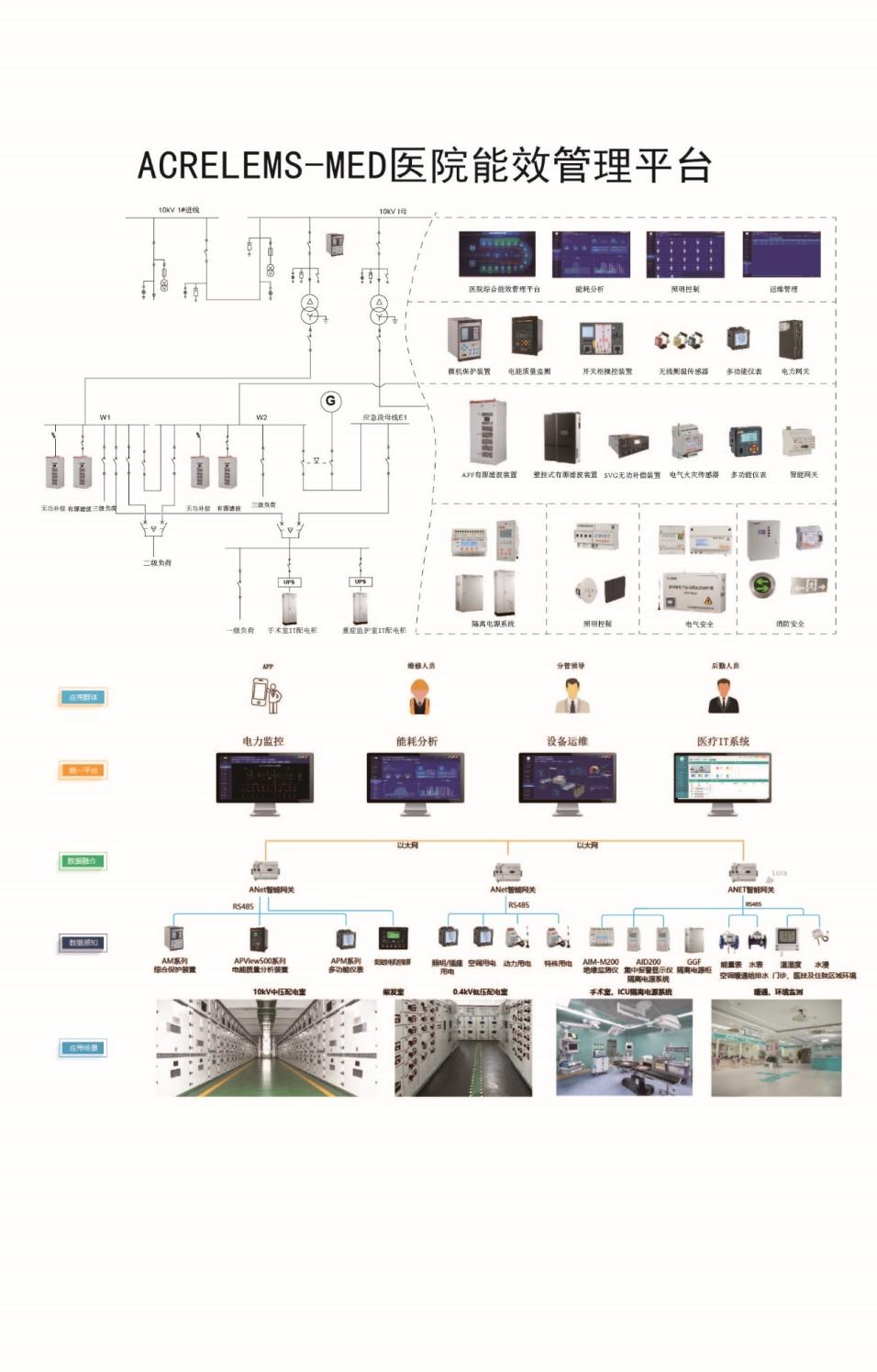

淺談醫(yī)院配電系統(tǒng)諧波分析及治理研究

基站供配電系統(tǒng)概述

什么是配電系統(tǒng)?配電系統(tǒng)如何分類(lèi)?

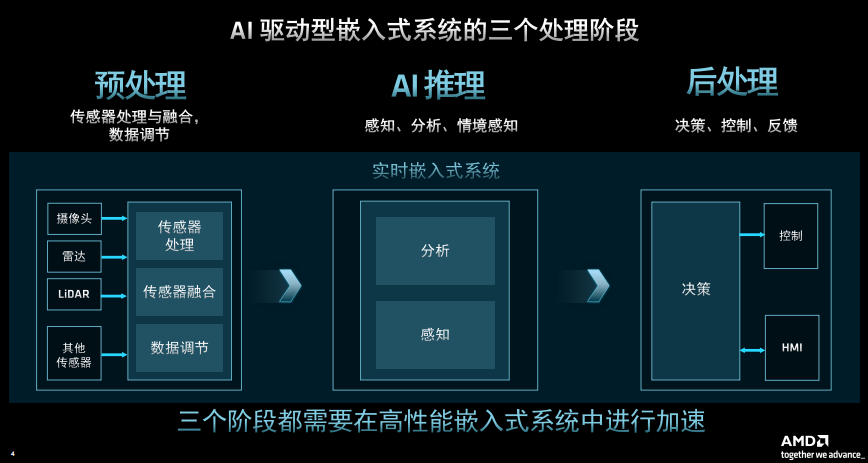

AMD Versal SoC刷新邊緣AI性能,單芯片方案驅(qū)動(dòng)嵌入式系統(tǒng)

AMD Versal SoC全新升級(jí)邊緣AI性能,單芯片方案驅(qū)動(dòng)嵌入式系統(tǒng)

在Vivado中構(gòu)建AMD Versal可擴(kuò)展嵌入式平臺(tái)示例設(shè)計(jì)流程

智能安全配電裝置在銀行配電系統(tǒng)中的應(yīng)用

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺(tái)之 Versal 介紹(2)

Versal ACAP中的配電系統(tǒng)

Versal ACAP中的配電系統(tǒng)

評(píng)論