同步技術(shù)

在芯片設(shè)計(jì)中,數(shù)據(jù)同步和在不同時(shí)鐘域之間進(jìn)行數(shù)據(jù)傳輸會(huì)經(jīng)常出現(xiàn)。為避免任何差錯(cuò)、系統(tǒng)故障和數(shù)據(jù)破壞,正確的同步和數(shù)據(jù)傳輸就顯得格外重要。這些問題的出現(xiàn)往往比較隱蔽,不易被發(fā)現(xiàn),因此正確進(jìn)行跨時(shí)鐘域處理就顯得極為重要。實(shí)現(xiàn)數(shù)據(jù)同步有許多種方式,在不同的情況下進(jìn)行恰當(dāng)?shù)耐椒绞竭x擇非常重要。以計(jì)算機(jī)中的南橋芯片為例,它通過不同的接口(如PCIe USB 吉比特以太網(wǎng)等)與外部設(shè)備相連。南橋通過不同的接口與外圍設(shè)備相連,它與北橋之間是一個(gè)通用數(shù)據(jù)接口。南橋芯片中需要使用數(shù)據(jù)同步技術(shù),目前,常用的同步技術(shù)主要分為以下幾類:

- 在不同的時(shí)鐘域之間使用FIFO

- 在不同的時(shí)鐘域之間使用握手信號(hào)

- 相位差固定的同步域內(nèi)部的數(shù)據(jù)傳輸

- 準(zhǔn)同步域之間的數(shù)據(jù)傳輸

使用FIFO進(jìn)行的數(shù)據(jù)同步

當(dāng)存在兩個(gè)異步時(shí)鐘域并且二者之間進(jìn)行數(shù)據(jù)包傳輸時(shí),雙端口FIFO最為適合。FIFO有兩個(gè)端口,一個(gè)端口寫入輸入數(shù)據(jù),另一個(gè)端口讀出數(shù)據(jù),如圖6.34所示。兩個(gè)端口工作在相互獨(dú)立的時(shí)鐘域內(nèi),通過各自的指針(地址)來讀寫數(shù)據(jù)。由于每個(gè)端口工作在相互獨(dú)立的時(shí)鐘域內(nèi),因此讀寫操作可以獨(dú)立實(shí)現(xiàn)并且不會(huì)出現(xiàn)任何差錯(cuò)。當(dāng)FIFO變滿時(shí),應(yīng)停止寫操作,直到FIFO中出現(xiàn)空閑空間。同樣,當(dāng)FIFO為空時(shí),應(yīng)停止讀操作,直到有新的數(shù)據(jù)被寫入FIFO中。

握手同步方式

FIFO可用于在不同的時(shí)鐘域之間進(jìn)行數(shù)據(jù)包的傳輸,但是在一些應(yīng)用中需要在不同時(shí)鐘域之間進(jìn)行少量數(shù)據(jù)傳輸。FIFO占用的硬件資源較大,此時(shí)可以考慮使用握手同步機(jī)制.

所謂握手,即通信雙方使用了專用控制信號(hào)進(jìn)行狀態(tài)指示,這個(gè)控制信號(hào)既有發(fā)送域給接受域的也有接收域給控制域的,有別于單向控制信號(hào)方式。

使用握手協(xié)議方式處理跨時(shí)鐘域數(shù)據(jù)傳輸時(shí),只需要對(duì)雙方的握手信號(hào)(req 和 ack)分別使用脈沖檢測(cè)方法進(jìn)行同步,在具體實(shí)現(xiàn)中,假設(shè)req ,ack, data,總線在初始化時(shí)都處于無效狀態(tài),發(fā)送域先把數(shù)據(jù)放入總線,隨后發(fā)送有效的req信號(hào)給接收域;接收域在檢測(cè)到有效的req信號(hào)后鎖存數(shù)據(jù)總線,然后會(huì)送一個(gè)有效的ack信號(hào)表示讀取完成應(yīng)答;發(fā)送域在檢測(cè)到有效ack信號(hào)后撤銷當(dāng)前的req信號(hào),接收域在檢測(cè)到req撤銷后也相應(yīng)撤銷ack信號(hào),此時(shí)完成一次正常握手通信,此后,發(fā)送域可以繼續(xù)開始下一次握手通信,如此循環(huán),該方式能夠使接收到的數(shù)據(jù)穩(wěn)定可靠,有效的避免了亞穩(wěn)態(tài)的出現(xiàn),但是控制信號(hào)握手檢測(cè)會(huì)消耗通信雙方較多的時(shí)間。

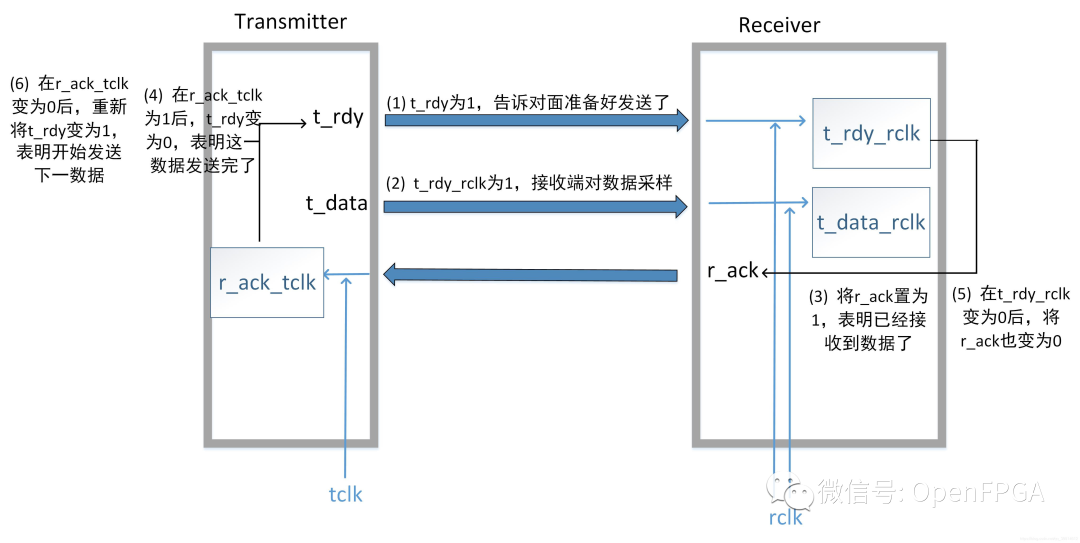

以下是握手同步機(jī)制的工作步驟:

-

用后綴_t表示發(fā)送端,用后綴_r表示接收端。發(fā)送時(shí)鐘用tclk表示,接收時(shí)鐘用rclk表示。數(shù)據(jù)從tclk域向rclk域傳輸;

-

當(dāng)需要發(fā)送的數(shù)據(jù)準(zhǔn)備好后,發(fā)送端將t_rdy信號(hào)置為有效,該信號(hào)必須在tclk下降沿時(shí)釆樣輸出;

-

在t_rdy有效期間,t_data必須保持穩(wěn)定;

-

接收端在rclk域中采用雙同步器同步t_rdy控制信號(hào),并把同步后的信號(hào)命名為t_rdy_rclk;

-

接收端在發(fā)現(xiàn)t_rdy_rclk信號(hào)有效時(shí),tdata已經(jīng)安全地進(jìn)入了rclk域,使用rclk對(duì)其進(jìn)行采樣,可以得到t_data_rclk。由于由于數(shù)據(jù)已經(jīng)在rclk域進(jìn)行了正確采樣,所以此后在rclk域使用該數(shù)據(jù)是安全的;

-

接收端將r_ack信號(hào)置位1,信號(hào)必須在rclk下降沿輸出;

-

發(fā)送端通過雙同步器在tclk域內(nèi)同步r_ack信號(hào),同步后的信號(hào)稱為r_ack_tclk;

-

以上所有步驟稱為半握手。tclk1,這是因?yàn)榘l(fā)送端在輸出下一數(shù)據(jù)之前,不會(huì)等r_ack_tclk被置為0;

-

半握手機(jī)制工作速度快,但是,使用半握手機(jī)制時(shí)需要謹(jǐn)慎,一旦使用不當(dāng),會(huì)導(dǎo)致操作錯(cuò)誤;

-

從低頻時(shí)鐘域向高頻時(shí)鐘域傳輸數(shù)據(jù)時(shí),半握手機(jī)制較為適用,這是由于接收端可以更快地完成操作。然而,如果從高頻時(shí)鐘域向低頻時(shí)鐘域傳輸數(shù)據(jù),則需要采用全握手機(jī)制;

-

當(dāng)r_ack_tclk為高電平時(shí),發(fā)送端將t_rdy置為0;

-

當(dāng)t_rdy_rclk為低電平時(shí),接收端將r_ack置為0;

-

當(dāng)發(fā)送端發(fā)現(xiàn)r_ack_tclk為低電平后,全握手過程結(jié)束,傳輸端可以發(fā)送新的數(shù)據(jù);

-

顯然,全握手過程耗時(shí)較長,數(shù)據(jù)傳輸速度較慢。然而,全握手機(jī)制穩(wěn)定可靠,可以在兩個(gè)任意頻率的時(shí)鐘域內(nèi)安全地進(jìn)行數(shù)據(jù)傳輸。如圖6.35所示為全握手機(jī)制工作波形。

上面過程比較繞口,因此我制作了一張流程圖,如下所示:

全握手機(jī)制代碼及仿真結(jié)果如下。

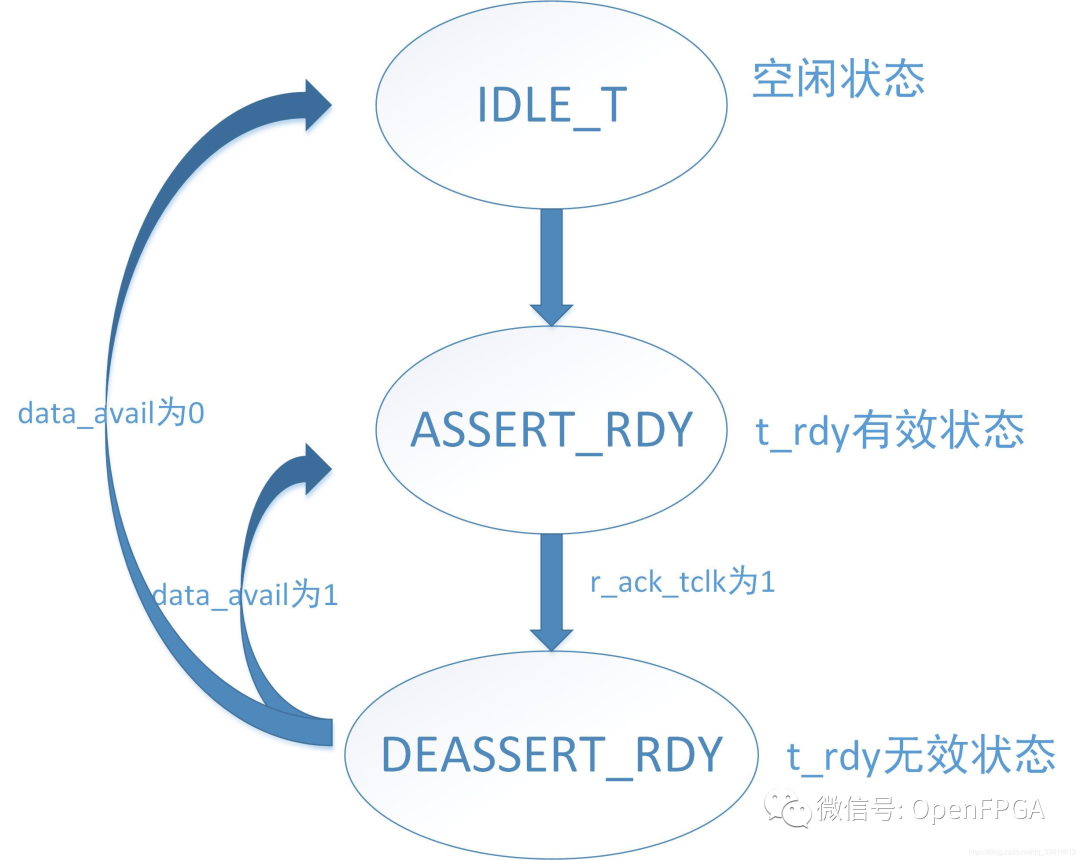

發(fā)送端:使用三個(gè)狀態(tài)的狀態(tài)機(jī),其跳轉(zhuǎn)關(guān)系如下:

moduletransmit(tclk,reset_tclk,t_rdy,data_avail,transmit_data,t_data,r_ack);

inputtclk;

inputreset_tclk;

inputdata_avail;

input[31:0]transmit_data;

inputr_ack;

outputt_rdy;

outputt_data;

localparamIDLE_T=2'd0,

ASSERT_T_RDY=2'd1,

DEASSERT_T_RDY=2'd2;

reg[1:0]t_hndshk_state,t_hndshk_state_nxt;

regt_rdy,t_rdy_nxt;

reg[31:0]t_data,t_data_nxt;

regr_ack_tclk;

always@(*)begin

t_hndshk_state_nxt=t_hndshk_state;

t_rdy_nxt=1'b0;

t_data_nxt=t_data;

case(t_hndshk_state)

IDLE_T:begin

if(data_avail)begin

t_rdy_nxt=1'b1;

t_hndshk_state_nxt=ASSERT_T_RDY;

t_data_nxt=transmit_data;

end

end

ASSERT_T_RDY:begin

if(r_ack_tclk)begin

t_rdy_nxt=1'b0;

t_hndshk_state_nxt=DEASSERT_T_RDY;

t_data_nxt='d0;

end

elsebegin

t_rdy_nxt=1'b1;

t_data_nxt=transmit_data;

end

end

DEASSERT_T_RDY:begin

if(!r_ack_tclk)begin

if(data_avail)begin

t_rdy_nxt=1'b1;

t_hndshk_state_nxt=ASSERT_T_RDY;

t_data_nxt=transmit_data;

end

elsebegin

t_hndshk_state_nxt=IDLE_T;

end

end

end

endcase

end

always@(posedgetclkornegedgereset_tclk)begin

if(!reset_tclk)begin

t_rdy<=?1'b0;

t_hndshk_state<=?IDLE_T;

??t_data?<=?32'h00000000;

r_ack_tclk<=?1'b0;

end

elsebegin

t_rdy<=?t_rdy_nxt;

??t_hndshk_state?<=?t_hndshk_state_nxt;

??t_data?<=?t_data_nxt;

??r_ack_tclk?<=?r_ack;

?end

?

end

endmodule?

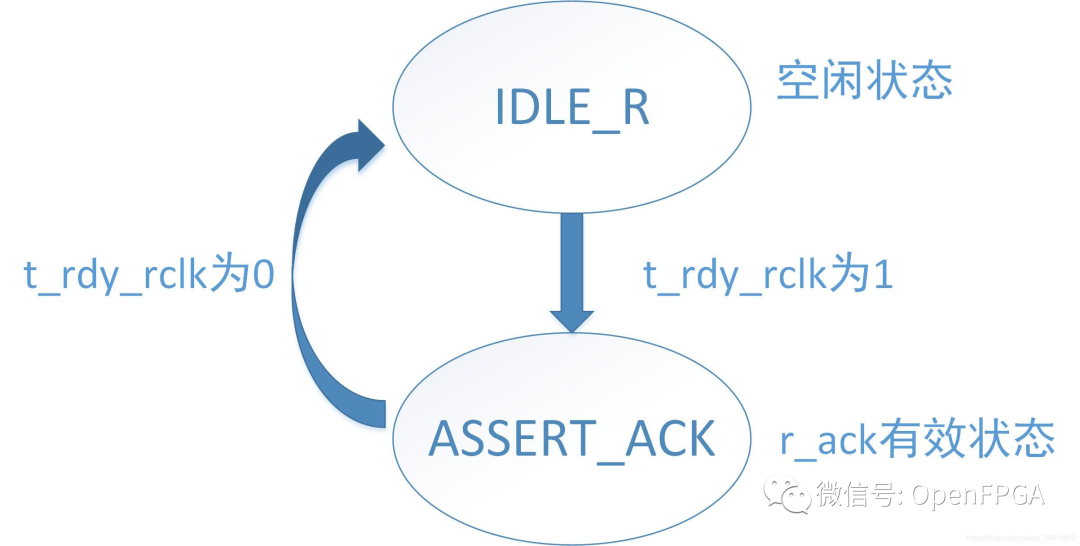

接收端:使用兩個(gè)狀態(tài)的狀態(tài)機(jī),跳轉(zhuǎn)關(guān)系如下:

modulereceiver(rclk,reset_rclk,t_rdy,t_data,r_ack);

inputrclk,reset_rclk;

inputt_rdy;

input[31:0]t_data;

outputr_ack;

regr_hndshk_state,r_hndshk_state_nxt;

regt_rdy_rclk;

reg[31:0]t_data_rclk,t_data_rclk_nxt;

regr_ack,r_ack_nxt;

localparamIDLE_R=1'b0,

ASSERT_ACK=1'b1;

always@(*)begin

r_hndshk_state_nxt=r_hndshk_state;

r_ack_nxt=1'b0;

t_data_rclk_nxt=t_data_rclk;

case(r_hndshk_state)

IDLE_R:begin

if(t_rdy_rclk)begin

r_hndshk_state_nxt=ASSERT_ACK;

t_data_rclk_nxt=t_data;

r_ack_nxt=1'b1;

end

end

ASSERT_ACK:begin

if(!t_rdy_rclk)begin

r_hndshk_state_nxt=IDLE_R;

r_ack_nxt=1'b0;

end

elsebegin

r_ack_nxt=1'b1;

end

end

endcase

end

always@(posedgerclkornegedgereset_rclk)begin

if(!reset_rclk)begin

r_hndshk_state<=?IDLE_R;

??t_data_rclk?<=?1'b0;

t_rdy_rclk<=?1'b0;

r_ack<=?1'b0;

end

elsebegin

r_hndshk_state<=?r_hndshk_state_nxt;

??t_data_rclk?<=?t_data_rclk_nxt;

??t_rdy_rclk?<=?t_rdy;

??r_ack?<=?r_ack_nxt;

?end

end

endmodule

測(cè)試代碼

`timescale1ns/1ns

moduletestbench;

regtclk_tb,rclk_tb;

reg[31:0]transmit_data_tb;

regreset_tclk_tb,reset_rclk_tb;

regdata_avail_tb;

wiret_rdy_tb;

wire[31:0]t_data_tb;

wirer_ack_tb;

parameterCLK_HALF_PERIOD1=5;

parameterCLK_HALF_PERIOD2=8;

parameterRESET_DELAY=100;

initialbegin

tclk_tb=0;

rclk_tb=0;

end

always#CLK_HALF_PERIOD1tclk_tb=~tclk_tb;

always#CLK_HALF_PERIOD2rclk_tb=~rclk_tb;

initialbegin

reset_rclk_tb=0;

reset_tclk_tb=0;

#RESET_DELAYreset_rclk_tb=1;

reset_tclk_tb=1;

end

initialbegin

#500;

data_avail_tb=1;

transmit_data_tb=32'h96431346;

end

transmittransmit_test

(.tclk(tclk_tb),

.reset_tclk(reset_tclk_tb),

.t_rdy(t_rdy_tb),

.data_avail(data_avail_tb),

.transmit_data(transmit_data_tb),

.t_data(t_data_tb),

.r_ack(r_ack_tb));

receiverreceiver_test

(.rclk(rclk_tb),

.reset_rclk(reset_rclk_tb),

.t_rdy(t_rdy_tb),

.t_data(t_data_tb),

.r_ack(r_ack_tb));

endmodule

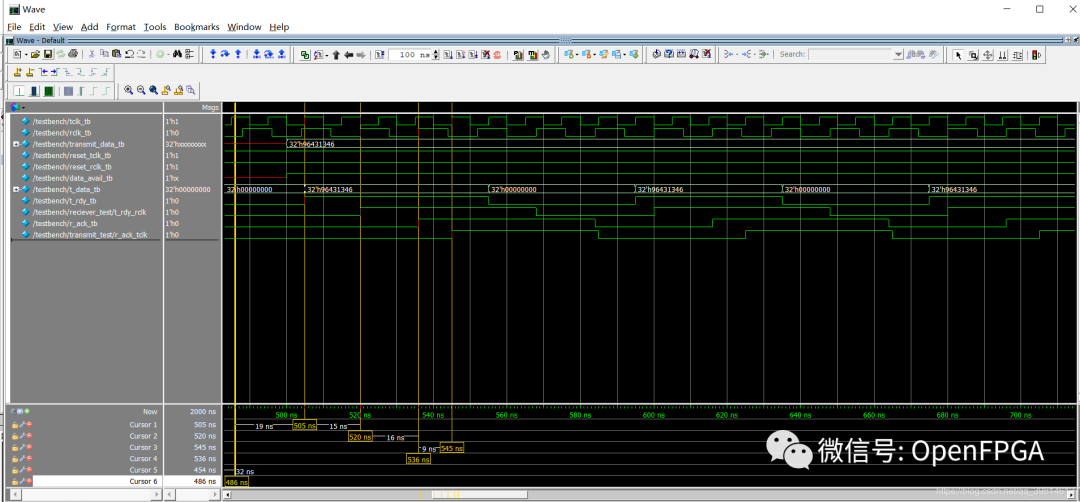

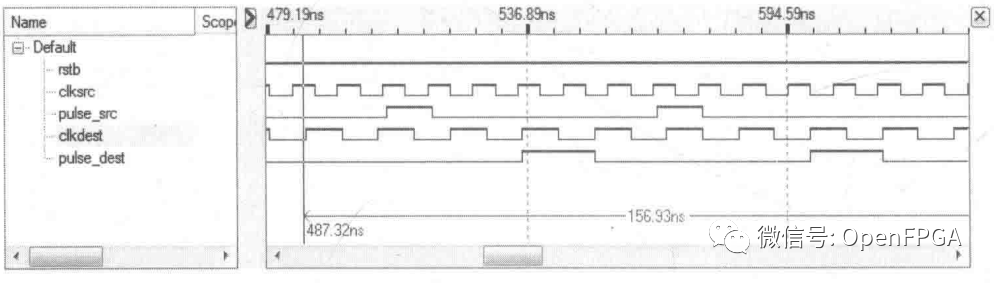

仿真結(jié)果

脈沖同步器

脈沖同步器在源時(shí)鐘域內(nèi)接收一個(gè)脈沖,在目的時(shí)鐘域內(nèi)產(chǎn)生一個(gè)脈沖。脈沖同步器內(nèi)部通常采用全握手機(jī)制來產(chǎn)生輸出脈沖。在討論脈沖同步器工作原理之前,我們先討論它的用途。有時(shí)狀態(tài)機(jī)希望更新不同時(shí)鐘域內(nèi)寄存器的數(shù)值,它可以采用全握手同步機(jī)制來達(dá)到這一目的,但全握手同步機(jī)制存在同步延遲大的問題,在全握手完成之前,狀態(tài)機(jī)都將處于等待對(duì)方響應(yīng)的狀態(tài)。

為了解決這一問題,可以引入脈沖同步器電路。引入脈沖同步器后,狀態(tài)機(jī)在源時(shí)鐘域內(nèi)產(chǎn)生更新脈沖,此后繼續(xù)執(zhí)行其他操作。脈沖同步器可以接收脈沖并完成剩余的同步和輸出脈沖產(chǎn)生工作。需要注意的是,脈沖同步器完成全握手操作需要消耗多個(gè)時(shí)鐘周期,因此狀態(tài)機(jī)發(fā)出的兩個(gè)脈沖之間需要足夠的時(shí)間間隔,否則就會(huì)出現(xiàn)邏輯錯(cuò)誤。下面是脈沖同步器的工作步驟、Verilog代碼及仿真結(jié)果。

步驟:

-

當(dāng)源脈沖(pulse_src)有效時(shí),在源時(shí)鐘域中生成一個(gè)信號(hào),并且保持有效(該信號(hào)稱為sig_stretched);

-

使用同步器在目的時(shí)鐘域中對(duì)sig_stretched信號(hào)進(jìn)行同步,稱為sig_stretched_dest;

-

sig_stretched_dest信號(hào)被送回到源時(shí)鐘域并進(jìn)行同步稱為sig_stretched_ack;

-

如果sig_stretched_ack=1,則產(chǎn)生一個(gè)脈沖,根據(jù)這一反饋脈沖來將sig_stretched置為0(完成全握手);

-

基于sig_stretched_dest,在目的時(shí)鐘域中產(chǎn)生一個(gè)脈沖稱為pulse_dest。

modulepulse_synchronizer

(clksrc,

resetb_clksrc,

clkdest,

resetb_clkdest,

pulse_src,

pulse_dest);

//*******************************************************

inputclksrc;

inputresetb_clksrc;

inputclkdest;

inputresetb_clkdest;

inputpulse_src;//pulseinsourceclockdomain

outputpulse_dest;//pulseindestinationclockdomain

regsig_stretched;

wiresig_stretched_nxt;

regsig_stretched_syncl,sig_stretched_dest;

regsig_stretched_dest_dl;

regsig_stxetched_ack_pre,sig_stretched_ack,

regsig_stretched_ack_d1;

wiresig_stretched_ack_edge;

wirepulse_dest;

assignsig_stretched_nxt=sig_stretched_ack_edge?1'b0:(pulse_src?l'bl:sig_stretched);

always@(posedgeclksrcornegedgeresetb_clksrc)

begin

if(!resetb_clksrc)

sig_stretched<=?1'bO;

else

sig_stretched<=?sig_stretched_nxt;

end

//First?two?flops?for?synchronizing?and?the?third?one?for?pulse?generation

always?@(posedge?clkdest?or?negedge?resetb_clkdcst)

begin

if?(!resetb_clkdest)

begin

?sig_stretched_sync?<=?1'b0;

sig_stretchcd_dest<=?1'b0;

sig_stretched_dest_d1<=?1'b0;

end

else

begin

sig_stretchcd_sync1<=?sig_stretched;

sig_stretched_dest??<=?sig_stretched_sync1;

sig_stretched_dest_d1?<=?sig_stretched_dest;

end

end

//?First?two?flops?are?forsynchronizingbacktosourceclockdomain.

//thirdflopisforedgedetection

always@(posedgeclksrcornegedgeresetb_clksrc)

begin

if(!resetb_clksrc)

begin

sig_strctched_ack_pre<=?1'b0;

sig_stretchecl_ack<=?1'b0;

sig_stretched_ack_d1<=?1'b0;

end

else

begin

sig_stretched_ack_pre<=?sig_stretched_dest;

sig_stretched_ack?????<=?sig_stretched_ack_pre;

sig_stretchcd_ack_d1??<=?sig_strctched_ack;

end

end

assign?sig_stretched_ack_edge?=?sig_stretched_ack?&?!sig_stretched_ack_d1;

//?Pulse?generation?in?destination?clock?domain

assign?pulse_dest?=?sig_stretched_dest?&?!sig_stxctched_dest_d1;

endmodule

相位、頻率關(guān)系固定時(shí)的跨時(shí)鐘域數(shù)據(jù)傳輸

如果兩個(gè)時(shí)鐘具有相同或者整數(shù)倍的頻率關(guān)系,上升沿之間有固定、明確的相位關(guān)系,那么在不使用FIFO或者握手協(xié)議的情況下,可以進(jìn)行數(shù)據(jù)傳輸。此時(shí)固定明確的相位關(guān)系非常重要,數(shù)據(jù)傳遞時(shí)的建立時(shí)間和保持時(shí)間必須滿足要求,如果相位關(guān)系不固定、不明確,則無法采用這種機(jī)制進(jìn)行跨時(shí)鐘域數(shù)據(jù)傳遞。在系統(tǒng)復(fù)位之后,需要調(diào)整數(shù)據(jù)延遲值(使用延遲鏈電路),從而確保跨時(shí)鐘域數(shù)據(jù)傳遞時(shí)可以進(jìn)行正確采樣。

這種機(jī)制與使用FIFO或者握手機(jī)制相比具有更小的延遲。例如,DDR數(shù)據(jù)總線上可以使用單倍的時(shí)鐘實(shí)現(xiàn)雙倍的數(shù)據(jù)傳輸。前面講過的數(shù)據(jù)位寬調(diào)整電路,也要求雙方的時(shí)鐘頻率和相位具有間定、明確的關(guān)系。

準(zhǔn)同步時(shí)鐘域

如果兩個(gè)時(shí)鐘具有相同的標(biāo)稱頻率和指定范圍內(nèi)的時(shí)鐘精度誤差,那么我們說這兩個(gè)時(shí)鐘源是準(zhǔn)同步的。在實(shí)際應(yīng)用中,通常數(shù)據(jù)發(fā)送端的本地時(shí)鐘和接收端的本地時(shí)鐘是獨(dú)立產(chǎn)生的,通常都使用晶體振蕩器這類高精度時(shí)鐘源,二者往往具有相同的標(biāo)稱值和規(guī)定范圍內(nèi)的精度誤差。

例如,PCIe要求發(fā)送和接收時(shí)鐘誤差在300ppm以內(nèi)。這就意味著在一個(gè)相對(duì)較長的時(shí)間里(例如,對(duì)PCIe來說,超過1300個(gè)時(shí)鐘周期),兩個(gè)時(shí)鐘將產(chǎn)生1個(gè)時(shí)鐘周期的偏差。下面我們將討論此時(shí)如何進(jìn)行數(shù)據(jù)傳輸同步。

PCIe,SATA等串行通信協(xié)議中廣泛使用了準(zhǔn)同步通信機(jī)制。在數(shù)據(jù)收發(fā)電路中,彈性緩沖區(qū)(FIFO)被用于進(jìn)行跨時(shí)鐘域數(shù)據(jù)傳輸。此時(shí)FIFO不僅用于跨時(shí)鐘域的同步,還需要與一定的外部電路配合,解決長時(shí)間通信時(shí),由于時(shí)鐘偏差造成的FIFO內(nèi)部數(shù)據(jù)上溢或下溢的問題。PCIe和SATA要求發(fā)送端周期性地將null字符插入傳輸數(shù)據(jù)流中;在接收端,根據(jù)FIFO內(nèi)部的數(shù)據(jù)深度,這些null字符會(huì)被丟棄或添加到FIFO中。

-

usb

+關(guān)注

關(guān)注

60文章

7963瀏覽量

265262 -

fifo

+關(guān)注

關(guān)注

3文章

389瀏覽量

43770 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110187 -

HDL

+關(guān)注

關(guān)注

8文章

327瀏覽量

47416

原文標(biāo)題:Verilog HDL-同步技術(shù)

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Verilog 與 ASIC 設(shè)計(jì)的關(guān)系 Verilog 代碼優(yōu)化技巧

Verilog與VHDL的比較 Verilog HDL編程技巧

數(shù)字系統(tǒng)設(shè)計(jì)與Verilog HDL

Verilog硬件描述語言參考手冊(cè)

Verilog HDL的基礎(chǔ)知識(shí)

Verilog HDL-同步技術(shù)你了解多少

Verilog HDL-同步技術(shù)你了解多少

評(píng)論