向量擴(kuò)展將定稿,RISC-V機(jī)器學(xué)習(xí)的崛起

RISC-V作為一個(gè)與x86和Arm相比仍算年輕的架構(gòu),自然需要不少擴(kuò)展模塊來(lái)完善其指令集架構(gòu),尤其是對(duì)標(biāo)x86與Arm的SIMD指令集。然而SIMD指令集隨著時(shí)間的發(fā)展變得越來(lái)越臃腫,讓架構(gòu)變得愈發(fā)復(fù)雜,David Patterson也在幾年前的一篇文章中寫(xiě)道,實(shí)現(xiàn)數(shù)據(jù)級(jí)并行性更優(yōu)雅的方式就是向量架構(gòu),RISC-V的向量擴(kuò)展(RVV)也應(yīng)運(yùn)而生。

在機(jī)器學(xué)習(xí)算法中,向量被廣泛用于處理數(shù)據(jù)集和數(shù)組。而RVV為基礎(chǔ)指令集新增了多個(gè)向量寄存器和向量指令,可以讓基于RISC-V架構(gòu)的處理器核心處理數(shù)組,與傳統(tǒng)的標(biāo)量運(yùn)算一起來(lái)加速大數(shù)據(jù)集的指令運(yùn)算。

RISC-V向量擴(kuò)展指令于2018年推出,在經(jīng)過(guò)了多個(gè)版本的迭代后,終于在幾天前進(jìn)入了1.0 PB狀態(tài)。RVV工作組認(rèn)同了1.0版本的穩(wěn)定性,已經(jīng)可以在上游軟件項(xiàng)目中開(kāi)發(fā)相關(guān)的工具鏈、功能模擬器與實(shí)現(xiàn)了。而前段時(shí)間的RISC-V論壇,也展示了RISC-V在向量與機(jī)器學(xué)習(xí)上的進(jìn)展。

RISC-V機(jī)器學(xué)習(xí)用于太空應(yīng)用

相信不少人都注意到近期逐漸增加的各項(xiàng)太空探索任務(wù),比如祝融號(hào)火星車(chē)與中國(guó)空間站建設(shè)等,這些任務(wù)中AI與機(jī)器學(xué)習(xí)的應(yīng)用也開(kāi)始出現(xiàn)。然而將AI與機(jī)器學(xué)習(xí)加入太空任務(wù)依舊面臨著諸多挑戰(zhàn),比如已有的太空處理器已經(jīng)無(wú)法跟上AI與ML的計(jì)算需求,但現(xiàn)成的商用設(shè)備既無(wú)法滿(mǎn)足輻射要求,也沒(méi)有太空認(rèn)證的軟件棧支持。

來(lái)自加泰羅尼亞理工大學(xué)和巴塞羅那超算中心的兩位研究員Leonidas Kosmidis和Marc Solé Bonet給出了他們的創(chuàng)新方案,實(shí)現(xiàn)了在功率有限的RISC-V處理器上加速M(fèi)L運(yùn)算。與采用額外大面積向量寄存器文件的傳統(tǒng)方式不同,他們采用了一個(gè)開(kāi)源的短SIMD模塊通過(guò)重復(fù)利用整數(shù)寄存器文件來(lái)減小面積。這一方案以2個(gè)未使用的RISC-V操作碼實(shí)現(xiàn)了17個(gè)高度可配置的定制指令,可以用于實(shí)現(xiàn)ML應(yīng)用中200多種組合運(yùn)算。

他們成功將該模塊移植到了Cobham Gaisler開(kāi)發(fā)的開(kāi)源RISC-V太空處理器NOEL-V上,在最小的NOEL-V處理器的配置下進(jìn)行通用ML程序的測(cè)試,得出的結(jié)果相當(dāng)可觀。只需多用到25%的面積,就能實(shí)現(xiàn)3到7倍的性能提升,還不會(huì)影響到處理器的頻率。

兩位研究員也實(shí)現(xiàn)了Gaisler另一個(gè)太空處理器LEON3的版本,該處理器采用的是SPARC V8的架構(gòu)。未來(lái)他們還計(jì)劃引入TensorFlow和編譯器代碼生成等一系列軟件支持,并在歐洲航天局OPS-SAT實(shí)驗(yàn)衛(wèi)星上的FPGA上進(jìn)行測(cè)試。

RISC-V向量處理器的真正挑戰(zhàn)

90年代可以說(shuō)是DSP、CISC與DSP三家爭(zhēng)霸的狀態(tài),然而到了21世紀(jì),DSP已經(jīng)越來(lái)越難突破GHz,而高頻CPU中乘積累加運(yùn)算單元的流行使得DSP在性能上敗下陣來(lái)。而RISC與CISC相比的優(yōu)勢(shì)在于其簡(jiǎn)單化的特性,更容易實(shí)現(xiàn)高頻率。然而在向量處理器(VPU)上,必須要解決數(shù)據(jù)傳輸?shù)膯?wèn)題。

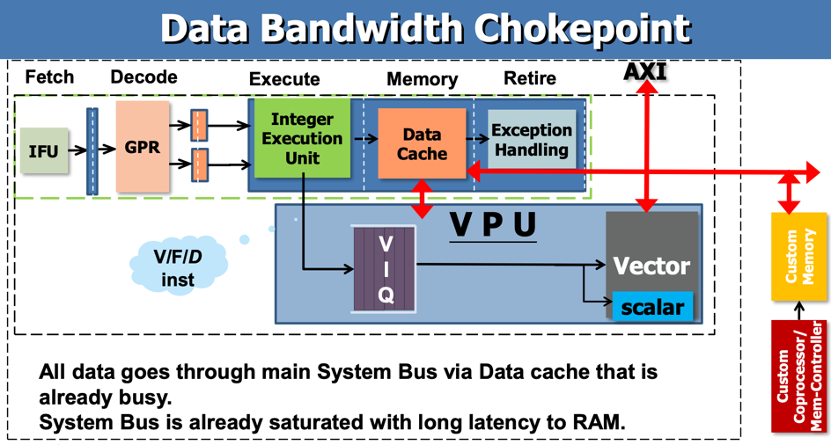

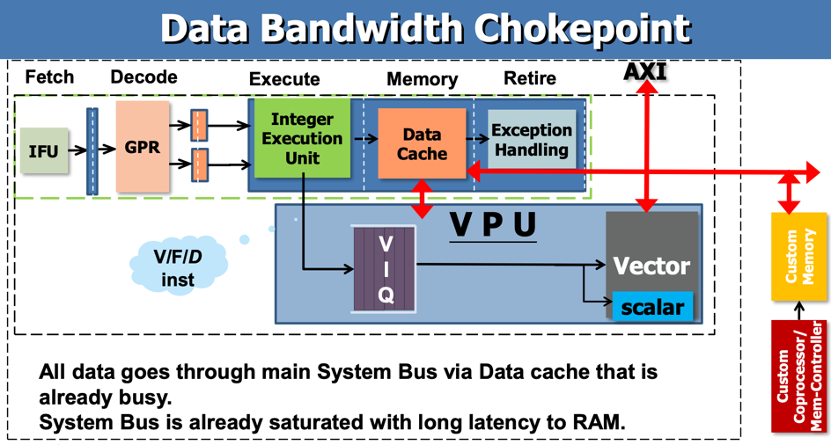

傳統(tǒng)VPU在帶寬上的瓶頸 / 晶心科技

從數(shù)據(jù)傳輸?shù)牧鞒虂?lái)看,系統(tǒng)總線(xiàn)已經(jīng)被處理器占用處于繁忙狀態(tài),而所有數(shù)據(jù)都通過(guò)緩存走向總線(xiàn),現(xiàn)在又多出了向量指令和向量數(shù)據(jù),致使總線(xiàn)到內(nèi)存的延遲增加,整體性能下降。因此,提高總線(xiàn)帶寬的同時(shí)保持高頻率,又不會(huì)增加額外的功耗也就成了一大設(shè)計(jì)挑戰(zhàn)。傳統(tǒng)的解決方案有預(yù)讀取和更大的獨(dú)立內(nèi)存與緩存等,但往往需要犧牲功耗和尺寸。

晶心科技為了解決這一挑戰(zhàn),推出了晶心自定義擴(kuò)展(Andes Custom Extension,ACE),這一RISC-V擴(kuò)展可以創(chuàng)造新的指令、新的協(xié)處理器和新的內(nèi)存位置。ACE引入了全新的Streaming Port,為外部硬件引擎創(chuàng)造了自定義數(shù)據(jù)接口和自定義數(shù)據(jù)內(nèi)存,以很小的功率代價(jià)解決了數(shù)據(jù)傳輸問(wèn)題。除此之外,ACE還可以用于數(shù)據(jù)預(yù)處理與后處理,比如格式轉(zhuǎn)換等,進(jìn)一步提升VPU的性能,更好地控制和管理外部加速器。

結(jié)語(yǔ)

RISC-V在向量擴(kuò)展與處理器上的進(jìn)展已經(jīng)相當(dāng)驚人,要知道蘋(píng)果在前段時(shí)間招募RISC-V開(kāi)發(fā)者的工作描述中,不僅要求掌握RISC-V的開(kāi)發(fā)知識(shí),還要求了解Arm NEON SIMD微架構(gòu)的向量編程。隨著RVV的定稿,向量寄存器與指令也將全部確定下來(lái),屆時(shí)相關(guān)的編譯器等工具鏈也能夠及時(shí)做到兼容。

RISC-V作為一個(gè)與x86和Arm相比仍算年輕的架構(gòu),自然需要不少擴(kuò)展模塊來(lái)完善其指令集架構(gòu),尤其是對(duì)標(biāo)x86與Arm的SIMD指令集。然而SIMD指令集隨著時(shí)間的發(fā)展變得越來(lái)越臃腫,讓架構(gòu)變得愈發(fā)復(fù)雜,David Patterson也在幾年前的一篇文章中寫(xiě)道,實(shí)現(xiàn)數(shù)據(jù)級(jí)并行性更優(yōu)雅的方式就是向量架構(gòu),RISC-V的向量擴(kuò)展(RVV)也應(yīng)運(yùn)而生。

在機(jī)器學(xué)習(xí)算法中,向量被廣泛用于處理數(shù)據(jù)集和數(shù)組。而RVV為基礎(chǔ)指令集新增了多個(gè)向量寄存器和向量指令,可以讓基于RISC-V架構(gòu)的處理器核心處理數(shù)組,與傳統(tǒng)的標(biāo)量運(yùn)算一起來(lái)加速大數(shù)據(jù)集的指令運(yùn)算。

RISC-V向量擴(kuò)展指令于2018年推出,在經(jīng)過(guò)了多個(gè)版本的迭代后,終于在幾天前進(jìn)入了1.0 PB狀態(tài)。RVV工作組認(rèn)同了1.0版本的穩(wěn)定性,已經(jīng)可以在上游軟件項(xiàng)目中開(kāi)發(fā)相關(guān)的工具鏈、功能模擬器與實(shí)現(xiàn)了。而前段時(shí)間的RISC-V論壇,也展示了RISC-V在向量與機(jī)器學(xué)習(xí)上的進(jìn)展。

RISC-V機(jī)器學(xué)習(xí)用于太空應(yīng)用

相信不少人都注意到近期逐漸增加的各項(xiàng)太空探索任務(wù),比如祝融號(hào)火星車(chē)與中國(guó)空間站建設(shè)等,這些任務(wù)中AI與機(jī)器學(xué)習(xí)的應(yīng)用也開(kāi)始出現(xiàn)。然而將AI與機(jī)器學(xué)習(xí)加入太空任務(wù)依舊面臨著諸多挑戰(zhàn),比如已有的太空處理器已經(jīng)無(wú)法跟上AI與ML的計(jì)算需求,但現(xiàn)成的商用設(shè)備既無(wú)法滿(mǎn)足輻射要求,也沒(méi)有太空認(rèn)證的軟件棧支持。

來(lái)自加泰羅尼亞理工大學(xué)和巴塞羅那超算中心的兩位研究員Leonidas Kosmidis和Marc Solé Bonet給出了他們的創(chuàng)新方案,實(shí)現(xiàn)了在功率有限的RISC-V處理器上加速M(fèi)L運(yùn)算。與采用額外大面積向量寄存器文件的傳統(tǒng)方式不同,他們采用了一個(gè)開(kāi)源的短SIMD模塊通過(guò)重復(fù)利用整數(shù)寄存器文件來(lái)減小面積。這一方案以2個(gè)未使用的RISC-V操作碼實(shí)現(xiàn)了17個(gè)高度可配置的定制指令,可以用于實(shí)現(xiàn)ML應(yīng)用中200多種組合運(yùn)算。

他們成功將該模塊移植到了Cobham Gaisler開(kāi)發(fā)的開(kāi)源RISC-V太空處理器NOEL-V上,在最小的NOEL-V處理器的配置下進(jìn)行通用ML程序的測(cè)試,得出的結(jié)果相當(dāng)可觀。只需多用到25%的面積,就能實(shí)現(xiàn)3到7倍的性能提升,還不會(huì)影響到處理器的頻率。

兩位研究員也實(shí)現(xiàn)了Gaisler另一個(gè)太空處理器LEON3的版本,該處理器采用的是SPARC V8的架構(gòu)。未來(lái)他們還計(jì)劃引入TensorFlow和編譯器代碼生成等一系列軟件支持,并在歐洲航天局OPS-SAT實(shí)驗(yàn)衛(wèi)星上的FPGA上進(jìn)行測(cè)試。

RISC-V向量處理器的真正挑戰(zhàn)

90年代可以說(shuō)是DSP、CISC與DSP三家爭(zhēng)霸的狀態(tài),然而到了21世紀(jì),DSP已經(jīng)越來(lái)越難突破GHz,而高頻CPU中乘積累加運(yùn)算單元的流行使得DSP在性能上敗下陣來(lái)。而RISC與CISC相比的優(yōu)勢(shì)在于其簡(jiǎn)單化的特性,更容易實(shí)現(xiàn)高頻率。然而在向量處理器(VPU)上,必須要解決數(shù)據(jù)傳輸?shù)膯?wèn)題。

傳統(tǒng)VPU在帶寬上的瓶頸 / 晶心科技

從數(shù)據(jù)傳輸?shù)牧鞒虂?lái)看,系統(tǒng)總線(xiàn)已經(jīng)被處理器占用處于繁忙狀態(tài),而所有數(shù)據(jù)都通過(guò)緩存走向總線(xiàn),現(xiàn)在又多出了向量指令和向量數(shù)據(jù),致使總線(xiàn)到內(nèi)存的延遲增加,整體性能下降。因此,提高總線(xiàn)帶寬的同時(shí)保持高頻率,又不會(huì)增加額外的功耗也就成了一大設(shè)計(jì)挑戰(zhàn)。傳統(tǒng)的解決方案有預(yù)讀取和更大的獨(dú)立內(nèi)存與緩存等,但往往需要犧牲功耗和尺寸。

晶心科技為了解決這一挑戰(zhàn),推出了晶心自定義擴(kuò)展(Andes Custom Extension,ACE),這一RISC-V擴(kuò)展可以創(chuàng)造新的指令、新的協(xié)處理器和新的內(nèi)存位置。ACE引入了全新的Streaming Port,為外部硬件引擎創(chuàng)造了自定義數(shù)據(jù)接口和自定義數(shù)據(jù)內(nèi)存,以很小的功率代價(jià)解決了數(shù)據(jù)傳輸問(wèn)題。除此之外,ACE還可以用于數(shù)據(jù)預(yù)處理與后處理,比如格式轉(zhuǎn)換等,進(jìn)一步提升VPU的性能,更好地控制和管理外部加速器。

結(jié)語(yǔ)

RISC-V在向量擴(kuò)展與處理器上的進(jìn)展已經(jīng)相當(dāng)驚人,要知道蘋(píng)果在前段時(shí)間招募RISC-V開(kāi)發(fā)者的工作描述中,不僅要求掌握RISC-V的開(kāi)發(fā)知識(shí),還要求了解Arm NEON SIMD微架構(gòu)的向量編程。隨著RVV的定稿,向量寄存器與指令也將全部確定下來(lái),屆時(shí)相關(guān)的編譯器等工具鏈也能夠及時(shí)做到兼容。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

處理器

+關(guān)注

關(guān)注

68文章

19379瀏覽量

230452 -

ARM

+關(guān)注

關(guān)注

134文章

9120瀏覽量

368220 -

RISC-V

+關(guān)注

關(guān)注

45文章

2306瀏覽量

46293

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

RISC-V 與 ARM 架構(gòu)的區(qū)別 RISC-V與機(jī)器學(xué)習(xí)的關(guān)系

在現(xiàn)代計(jì)算機(jī)架構(gòu)中,RISC-V和ARM是兩種流行的處理器架構(gòu)。它們各自具有獨(dú)特的特點(diǎn)和優(yōu)勢(shì),適用于不同的應(yīng)用場(chǎng)景。 1. RISC-V架構(gòu) RISC-V(讀作“risk-five”)是一種開(kāi)源

關(guān)于RISC-V學(xué)習(xí)路線(xiàn)圖推薦

RISC-V簡(jiǎn)介 :

了解RISC-V的起源、特點(diǎn)、優(yōu)勢(shì)以及應(yīng)用場(chǎng)景。

RISC-V指令集 :

學(xué)習(xí)RISC-V的基本指令集,如RV32I

發(fā)表于 11-30 15:21

希姆計(jì)算的RISC-V矩陣擴(kuò)展開(kāi)源項(xiàng)目已升級(jí)至0.5版本,支持向量+矩陣的實(shí)現(xiàn)

希姆計(jì)算的RISC-V矩陣擴(kuò)展開(kāi)源項(xiàng)目已升級(jí)至0.5版本-----支持向量+矩陣的實(shí)現(xiàn)范福杰博士&陳煒博士項(xiàng)目背景Background為了解決RISC-V在人工智能領(lǐng)域中指令碎片化

RISC-V近期市場(chǎng)情況調(diào)研

RISC-V是一種開(kāi)源的指令集架構(gòu)(ISA),近年來(lái)在全球范圍內(nèi)迅速崛起,尤其在中國(guó),RISC-V的發(fā)展勢(shì)頭十分強(qiáng)勁。以下是目前RISC-V芯片的發(fā)展情況,以及中國(guó)在這一領(lǐng)域的主要公司

RISC-V如何支持不同的AI和機(jī)器學(xué)習(xí)框架和庫(kù)?

RISC-V如何支持不同的AI和機(jī)器學(xué)習(xí)框架和庫(kù)?還請(qǐng)壇友們多多指教一下。

發(fā)表于 10-10 22:24

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未來(lái) !

加入RISC-VAdvocate行列!我們正在尋找來(lái)自世界各地的RISC-V愛(ài)好者,通過(guò)全球推廣和參與,成為支持RISC-V進(jìn)步的關(guān)鍵參與者。作為一名RISC-VAdvocate,您將

RISC-V指令集的特點(diǎn)總結(jié)

各種應(yīng)用場(chǎng)景,從嵌入式系統(tǒng)到高性能計(jì)算,都可以通過(guò)添加專(zhuān)門(mén)的指令擴(kuò)展來(lái)優(yōu)化性能。

分層設(shè)計(jì)

定義:RISC-V 架構(gòu)采用了分層設(shè)計(jì)方法,基本指令集可以通過(guò)額外的擴(kuò)展層來(lái)增強(qiáng)功能,如浮點(diǎn)運(yùn)算、向

發(fā)表于 08-30 22:05

risc-v的發(fā)展歷史

RISC-V v2.1,增加了對(duì)64位體系結(jié)構(gòu)的支持,并提供了更詳細(xì)的文檔和規(guī)范。

2017年:RISC-V基金會(huì)推出了RISC-V v2.

發(fā)表于 07-29 17:20

RISC-V適合什么樣的應(yīng)用場(chǎng)景

設(shè)計(jì)使得開(kāi)發(fā)者可以靈活選擇所需的指令集和模塊,以滿(mǎn)足嵌入式系統(tǒng)的各種性能要求。

3. 人工智能(AI)和機(jī)器學(xué)習(xí)(ML)

高性能計(jì)算:RISC-V結(jié)合AI加速器或協(xié)處理器,可以提供高效的人工智能計(jì)算

發(fā)表于 07-29 17:16

為什么要有RISC-V

的,永遠(yuǎn)不會(huì)改變。這為編譯器編寫(xiě)者,操作系統(tǒng)開(kāi)發(fā)人員和匯

編語(yǔ)言程序員提供了穩(wěn)定的目標(biāo)。模塊化來(lái)源于可選的標(biāo)準(zhǔn)擴(kuò)展,根據(jù)應(yīng)用程序的需要,硬件可以包含或不包含這些擴(kuò)展。這種模塊化特性使得RISC-V具有了

發(fā)表于 07-27 15:05

risc-v多核芯片在AI方面的應(yīng)用

應(yīng)用中的成本。

最后,RISC-V多核芯片不僅可以應(yīng)用于AI邊緣計(jì)算領(lǐng)域,還可以擴(kuò)展到其他領(lǐng)域,如數(shù)據(jù)中心、云計(jì)算、自動(dòng)駕駛、機(jī)器人等,為這些領(lǐng)域提供高效、靈活和安全的解決方案。

總的來(lái)說(shuō),R

發(fā)表于 04-28 09:20

RISC-V 基礎(chǔ)學(xué)習(xí):RISC-V 基礎(chǔ)介紹

是什么?

RISC-V 是一套開(kāi)放許可證書(shū)、免費(fèi)的、由基金維護(hù)的、一個(gè)整數(shù)運(yùn)算指令集外加多個(gè)擴(kuò)展指令集的CPU 結(jié)構(gòu)規(guī)范(ISA)。

整數(shù)運(yùn)算指令集 + 擴(kuò)展指令集

任何硬件開(kāi)發(fā)商或者組織都可以

發(fā)表于 03-12 10:25

【RISC-V開(kāi)放架構(gòu)設(shè)計(jì)之道|閱讀體驗(yàn)】匯編語(yǔ)言和擴(kuò)展指令集

【RISC-V開(kāi)放架構(gòu)設(shè)計(jì)之道|閱讀體驗(yàn)】匯編語(yǔ)言和擴(kuò)展指令集

匯編語(yǔ)言

將C語(yǔ)言翻譯成可執(zhí)行的機(jī)器語(yǔ)言的重要步驟包括編譯過(guò)程,匯編過(guò)程,鏈接過(guò)程。

函數(shù)調(diào)用約定過(guò)程分為六個(gè)階段:

1)將參數(shù)存放

發(fā)表于 02-03 13:29

【RISC-V開(kāi)放架構(gòu)設(shè)計(jì)之道|閱讀體驗(yàn)】RISC-V基礎(chǔ)整數(shù)指令集

分支的B型,用于長(zhǎng)立即數(shù)的U型和用于無(wú)條件跳轉(zhuǎn)的J型。

下面是本章的思維導(dǎo)圖:

RV32I是RISC-V的基礎(chǔ)指令集,后續(xù)會(huì)繼續(xù)拓展RISC-V的其它指令集擴(kuò)展。

發(fā)表于 01-31 21:10

【RISC-V開(kāi)放架構(gòu)設(shè)計(jì)之道|閱讀體驗(yàn)】一本好書(shū),開(kāi)卷有益

大學(xué)教授的推薦并得到各方好評(píng),這更堅(jiān)定了深入了解學(xué)習(xí)RISC-V的信心。

書(shū)中在目錄前RISC-V指令集參考卡,做下瀏覽與了解,這里一并貼出。

RISC-V的目標(biāo)是成為一款通用的指

發(fā)表于 01-21 17:03

向量擴(kuò)展將定稿,RISC-V機(jī)器學(xué)習(xí)的崛起

向量擴(kuò)展將定稿,RISC-V機(jī)器學(xué)習(xí)的崛起

評(píng)論