Q1

package里面有Cl元素,除了對hast有影響,還有啥風險?

A

如果是金線,HTST會失效,會快速加劇kirkendall void效應(鹵素會跟kirkendall效應產生的某個金鋁合金發生反應),之前有遇到case,GREEN的mold compound,供應商清線不干凈,直接在含鹵的線上做的,導致不管怎樣,可靠性都過不了,后來分析成分和生產記錄,發現異常。更換其他批次材料才解決。銅線或者合金線沒有經歷過,感覺也可能會有。

通常EMC里不允許超過20ppm的Cl,但是這個值是個燃燒法出來的平均值,如果正好有顆含cl的顆粒在銅球邊上,這就會造成銅球IMC產生變化形成crack。產線上的Cl基本都是人體帶來的,還有PVC。除此之外,有些Fab廠會用HCL來做線路刻蝕,如果清潔不干凈就會有Cl的殘留。

Q2

請問有沒有人知道考慮SOC里面SRAM軟失效時是按照SRAM加起來的容量考慮還是按照分開的容量?比如通常1Mb以上的SRAM要加ECC,那么如果是兩塊512Kb的SRAM要加ECC嗎?可以認為是制程越先進,SER失效率越低嗎?比如90nm比65nm的SRAM尺寸大一倍,所以同樣容量的SRAM,65nm的FIT是90nm的一半SER FIT?

A

軟失效率FIT在外部輻射的通量和能量固定的情況下,與SRAM的面積是成比例的,因此兩塊SRAM也要加。加或者不加應該取決于對芯片的穩定性要求。

在特定制程下,考慮到制程越先進,密度越高這個因素,還有輻射引起的電離特性,肯定不能拿不同制程的面積來算對應比例的FIT。現在季豐SER團隊正在幫晶圓廠做28nm,14nm,7nm的SER對比實驗。等做完實驗,找一下對應關系。當前的判斷是在不同制程下,肯定不會和面積成線性關系。

Q3

bonding如果不在無塵環境下,有什么風險?

A

灰塵引入,焊接困難,小停機多,影響焊接品質和OEE。萬級問題不大。后面可以清洗。萬級與十萬級沒有特別大差別。實際上國內的封裝廠幾年前沒有一家在千級無塵室做WB的。千級無塵室沒有地面架空做不到的。

Q4

芯片倒著切,有誰知道這個工藝嗎?不是超薄片,目前擔心水壓造成芯片表面損傷,有人提出有反向切割,就是圓片在上面,刀具在下面的一種方式,所以在群里問問,是否有人做過這個。

A

對于芯片表面不能進水的芯片選擇方法1)激光隱形切割2)圖形芯片置于地面,SI面正面,刀片水切割;但是問題來了設備怎么識別切割道-一種切割設備影像識別部分升級或者SI面mark切割識別印記。以上二種方法能解決您的需求,因為沒有規模化量產需求,實現成本都很高。

Q5

關于ESD HBM標準,JS-001 和 IEC61000-4-2,輸出波形一樣的嗎?有啥區別?看標準,好像都是模擬人體靜電放電的 HBM?

A

波形不一樣,JS001是芯片級ESD,61000-4-2是系統級ESD。兩者等效電路不同,波形參數上均不同。

都屬于HBM,但芯片級是模擬人體直接接觸芯片,系統級模擬的是終端產品抗靜電能力,系統級更嚴苛。

Q6

陶瓷08b/08j的在季豐電子可以封裝?金絲要求30微米以上的。

A

季豐可以做的。

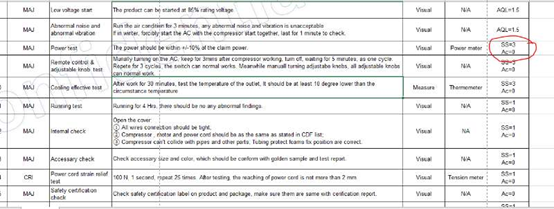

Q7

有誰知道這個SS=3 啥意思嗎?

A

Sample Size。

Q8

這個是disco的部件,有知道是什么的嗎?

A

Dressingtable,修整磨輪用的。

Q9

在FC封裝時候,把die傾斜45度,這樣做的技術成熟嗎?不是Z方向,中間紫色的是FC DIE。圖片如下所示:

A

這種沒問題的。正封的時候,有45°封裝的。倒裝FC平面旋轉45度也是可以做的。

Q10

請教下WLCSP 封測廠切換有什么可靠性影響嗎?

A

需要重新做qual實驗,facility change相當于重新走一遍流程。可以查看下圖assembly site 對應的測試項目。

Q11

電源類產品一定要做HTRB嗎?

A

HTRB是功率器件要的,比如MOST IGBT。IC不需要HTRB,是HAST,HTOL,TC等。

Q12

做過RDL的wafer,再做低溫-40度會有風險嗎?

A

RDL很常規,不影響可靠性。

Q13

你們做的RDL是在誰家做的?現在哪些封裝廠提供RDL?6um的Cu線寬線距能做到20um以內嗎?Cu下面墊的金屬有要求嗎?比如要求有多少層Al?或者Al的厚度?如果頂層Cu的話,是不是表面還要加一層polyimide?這樣可靠性比較好?否則Cu是否有氧化問題?

A

長電、華天、通富、智芯集成。RDL很多Bumping house都可以做,關鍵是看RDL的尺寸要求,如線寬,間距,厚度。wafer fab做RDL用表面的鋁層做,Bump house用Cu做。

可以的。現在10/10(線寬/間距)非常普通。最先進的是2/2。RDL下面墊有PI層,RDL是被PI層立體包圍的,不會有氧化之風險。

Cu RDL下面有PI,有鈍化層,一般對于金屬即Top metal沒有特殊需求。

Q14

請教一下,這個RDL是指頂層加厚銅還是厚鋁?

A

通常是Cu RDL。

Q15

bump表面出現較多黑絲狀物可能的原因是什么,會不會是出現了腐蝕現象?光刻膠的殘留有沒有常發生的位置呢?

A

邊緣位置的最好在電鏡下看一下,表面有異常元素,導致反應。有可能是F或Cl,金屬顆粒大、光刻膠殘留的可能性比較大,但不排除corrosion的可能,要確認是什么東西,只能SEM或光學顯微鏡下去看。

一般沒有,要看 Ashing 前后的工序對不對 notch了。另外,也不一定是光刻膠殘留,也可能是鈍化層或刻蝕中間反應物的殘留,要結合前后工序看。

Q16

CS測試是什么測試?

A

CS測試方法:https://re.sru.baidu.com/r/vUCkjRagSc?f=wf&u=7577c3cbc4a367a1。

編輯:jq

-

soc

+關注

關注

38文章

4190瀏覽量

218629 -

ECC

+關注

關注

0文章

97瀏覽量

20598

原文標題:季豐電子IC運營工程技術知乎 – 21W45

文章出處:【微信號:zzz9970814,微信公眾號:上海季豐電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

可靠性測試:HAST與PCT的區別

什么是芯片的HAST測試?

package里面有Cl元素,除了對hast有影響還有啥風險

package里面有Cl元素,除了對hast有影響還有啥風險

評論