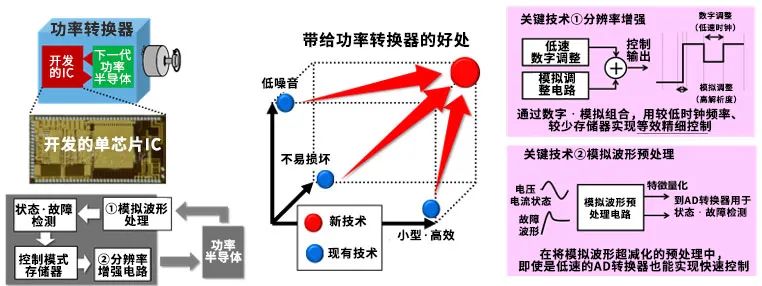

在控制下一代功率半導(dǎo)體的驅(qū)動(dòng)IC方面,株式會(huì)社東芝(下稱“東芝”)成功實(shí)現(xiàn)了將模擬與數(shù)字高性能電路集成到單個(gè)芯片中*1。該混合IC能夠以2微秒甚至更短的超高速檢測(cè)功率半導(dǎo)體的電壓和電流狀態(tài),發(fā)生短路等故障時(shí),可迅速反應(yīng),保護(hù)功率半導(dǎo)體免遭損壞。

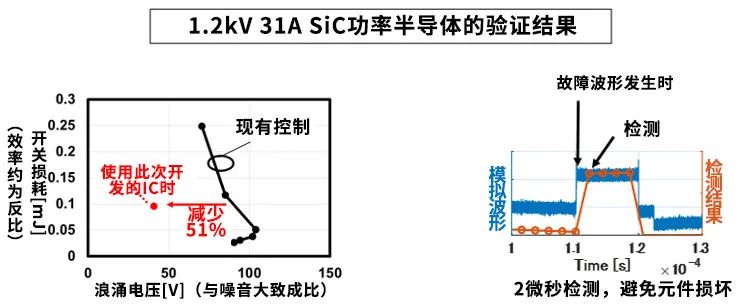

并且通過(guò)精細(xì)控制,可將功率半導(dǎo)體產(chǎn)生的噪聲降低51%。此外,經(jīng)理論計(jì)算證實(shí),與常規(guī)方法下的同等降噪效果相比,電機(jī)驅(qū)動(dòng)時(shí)的功率損耗可減少25%。

本技術(shù)通過(guò)最大限度地發(fā)揮下一代功率半導(dǎo)體的性能,推動(dòng)廣泛用于電動(dòng)汽車、工業(yè)設(shè)備、智能電網(wǎng)等應(yīng)用中的電機(jī)驅(qū)動(dòng)電路、直流·交流轉(zhuǎn)換器向小型化、高效化和高可靠性的方向發(fā)展,為實(shí)現(xiàn)碳中和社會(huì)做出貢獻(xiàn)。

研發(fā)背景

功率半導(dǎo)體是控制電壓和電流的半導(dǎo)體,用于電機(jī)的驅(qū)動(dòng),以及直流·交流等功率轉(zhuǎn)換。由于其應(yīng)用場(chǎng)景多,功率半導(dǎo)體和功率轉(zhuǎn)換器的小型化、高效化對(duì)實(shí)現(xiàn)碳中和社會(huì)而言必不可少。隨著功率半導(dǎo)體市場(chǎng)逐年擴(kuò)大,控制功率半導(dǎo)體的驅(qū)動(dòng)器IC其全球市場(chǎng)規(guī)模也從2017年的約1400億日元增長(zhǎng)到2021年的約1800億日元*2,預(yù)計(jì)未來(lái)還將繼續(xù)擴(kuò)大。

目前市面上一般使用IGBT*3和Si-MOSFET*4等作為功率半導(dǎo)體元件。如何降低功率轉(zhuǎn)換時(shí)所產(chǎn)生的損耗成為課題。為此,具有低損耗特性的SiC-MOSFET*5等下一代功率半導(dǎo)體正在開發(fā)中。下一代功率半導(dǎo)體可降低功率轉(zhuǎn)換器所產(chǎn)生的損耗,在實(shí)現(xiàn)高效化的同時(shí)便于散熱,且更小型化、輕型化。可是如采用與常規(guī)相同的電路方式進(jìn)行控制,雖然降低了功率損耗,但更容易產(chǎn)生噪音。另外,由于散熱路徑變短小,萬(wàn)一發(fā)生短路等故障,溫度瞬間升高,易導(dǎo)致半導(dǎo)體損壞。

有研究通過(guò)改進(jìn)控制方法來(lái)降低下一代功率半導(dǎo)體的噪聲,但其靈活性有問(wèn)題,因?yàn)楣β拾雽?dǎo)體元件的電壓和電流狀態(tài)不同,降噪的最佳方法也不盡相同。另外,在常規(guī)方法中,對(duì)短路等故障檢測(cè)·保護(hù)功能需要系統(tǒng)設(shè)計(jì)者通過(guò)微處理機(jī)實(shí)現(xiàn),存在固有的延遲而導(dǎo)致元件被損壞的風(fēng)險(xiǎn)。

本技術(shù)特點(diǎn)

東芝開發(fā)的混合模擬·數(shù)字電路的高性能單芯片柵極驅(qū)動(dòng)IC來(lái)解決以上問(wèn)題。一般,要實(shí)現(xiàn)與該IC同樣的高性能,需要使用信號(hào)轉(zhuǎn)換器、存儲(chǔ)器、運(yùn)算電路、放大器電路等多個(gè)單獨(dú)的半導(dǎo)體元件。而該模擬·數(shù)字混合電路,使用模擬電路檢測(cè)功率半導(dǎo)體元件的電壓·電流,再根據(jù)檢測(cè)結(jié)果用數(shù)字電路切換控制方法,只需一個(gè)芯片即可實(shí)現(xiàn)最佳控制。且還搭載具有存儲(chǔ)控制方法的存儲(chǔ)器。

此外,在控制過(guò)程中,通過(guò)組合低速數(shù)字電路和高速模擬電路的分辨率來(lái)增強(qiáng)電路,僅在需要高速控制的部分使用模擬,實(shí)現(xiàn)了等效、精細(xì)的控制。

通過(guò)開發(fā)模擬波形預(yù)處理技術(shù),從功率半導(dǎo)體的高速電壓·電流波形中,僅提取控制和故障檢測(cè)所需的特征,即便是低速模擬·數(shù)字轉(zhuǎn)換器也可快速完成故障檢測(cè)。由此,可以在不通過(guò)微機(jī)的情況下,檢測(cè)短路和其它故障并立即啟動(dòng)保護(hù)。并且還可通過(guò)使用現(xiàn)有設(shè)備的低成本CMOS*6工藝技術(shù)來(lái)實(shí)現(xiàn)。

浪涌電壓是產(chǎn)生噪音的主要因素之一。使用該IC控制1.2 kV的SiC-MOSFET功率半導(dǎo)體,在不增加功率損耗的情況下,可將浪涌電壓成功降低51%。理論上,若采用常規(guī)方法實(shí)現(xiàn)相同效果,電機(jī)驅(qū)動(dòng)時(shí)的損耗就會(huì)增加;如果使用該IC,則可以降低25%的功率損耗。另外,在不使用微機(jī)的情況下,可用最短2微秒的速度成功檢測(cè)出故障。有望最大限度地提高下一代功率半導(dǎo)體的性能。

圖1:開發(fā)的單芯片控制IC的概述、效果及主要技術(shù)

圖2:控制SiC-MOSFET功率半導(dǎo)體時(shí)的降噪效果和快速故障檢測(cè)結(jié)果

未來(lái)展望

東芝的目標(biāo)是在2025年將該IC投入實(shí)際應(yīng)用。功率半導(dǎo)體業(yè)務(wù)是集團(tuán)的重點(diǎn)發(fā)展領(lǐng)域,今后東芝也將繼續(xù)開發(fā)該IC的相關(guān)技術(shù),推進(jìn)下一代功率半導(dǎo)體在各類功率轉(zhuǎn)換系統(tǒng)中的應(yīng)用。通過(guò)功率半導(dǎo)體的高效化,降低CO2排放量,從而為實(shí)現(xiàn)碳中和社會(huì)做出貢獻(xiàn)。

*1:本技術(shù)于2021年10月10日至14日,在IEEE ECCE 2021(2021 IEEE Energy Conversion Congress and Exposition)在線會(huì)議上發(fā)表。

*2:出處:

https://s3.i-micronews.com/uploads/2019/01/YDPE17009_Gate_Driver_Market_and_Technology_Trends_Report_2017_Flyer.pdf(英文頁(yè)面)

*3:IGBT:Insulated Gate Bipolar Transistor的簡(jiǎn)稱。指基極內(nèi)置MOSFET的雙極晶體管。

*4:Si-MOSFET:Silicon MOSFET的簡(jiǎn)稱。晶體管的一種,與IGBT相比,適用于低功耗和高速工作。

*5:SiC-MOSFET:使用新材料SiC(碳化硅)的功率半導(dǎo)體。

*6:CMOS:半導(dǎo)體電路的一種。用于多種電子設(shè)備,包括個(gè)人電腦等。

編輯:jq

-

芯片

+關(guān)注

關(guān)注

456文章

50908瀏覽量

424484 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27475瀏覽量

219561 -

IGBT

+關(guān)注

關(guān)注

1267文章

3800瀏覽量

249264 -

驅(qū)動(dòng)IC

+關(guān)注

關(guān)注

9文章

305瀏覽量

33846

原文標(biāo)題:創(chuàng)新求變|東芝成功將控制下一代功率半導(dǎo)體的高性能驅(qū)動(dòng)IC單芯片化

文章出處:【微信號(hào):toshiba_semicon,微信公眾號(hào):東芝半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

意法半導(dǎo)體下一代汽車微控制器的戰(zhàn)略部署

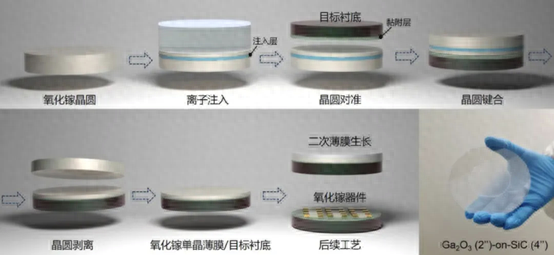

異質(zhì)集成氧化鎵:下一代高性能功率半導(dǎo)體器件的新基石

控制當(dāng)前和下一代功率控制器的輸入功率

類比半導(dǎo)體發(fā)布三款汽車智能驅(qū)動(dòng)芯片

IaaS+on+DPU(IoD)+下一代高性能算力底座技術(shù)白皮書

納微半導(dǎo)體下一代GaNFast氮化鎵功率芯片助力聯(lián)想打造全新氮化鎵快充

豐田、日產(chǎn)和本田將合作開發(fā)下一代汽車的AI和芯片

煜輝半導(dǎo)體獲近億元A輪融資,用于下一代半導(dǎo)體設(shè)備研發(fā)制造

意法半導(dǎo)體將推出基于新技術(shù)的下一代STM32微控制器

半導(dǎo)體IC設(shè)計(jì)是什么 ic設(shè)計(jì)和芯片設(shè)計(jì)區(qū)別

東芝半導(dǎo)體將加快開發(fā)下一代功率器件及SiC和GaN第三代半導(dǎo)體

全新潛力:金剛石作為下一代半導(dǎo)體的角逐者

東芝成功將控制下一代功率半導(dǎo)體的高性能驅(qū)動(dòng)IC單芯片化

東芝成功將控制下一代功率半導(dǎo)體的高性能驅(qū)動(dòng)IC單芯片化

評(píng)論