電源設計者如今面臨兩個主要問題:消除有害的輸入諧波電流和確保功率因數(shù)盡可能地接近于1。有害的諧波電流會導致傳輸設備過熱,并帶來后續(xù)必須解決的干擾難題;這兩者也會對電路的尺寸和/或效率產(chǎn)生不利影響。如果施加在線路上的負載不是純電阻性的,輸入電壓和電流波形之間將產(chǎn)生相移,從而增加視在功率并降低傳輸效率。如果非線性負載使輸入電流波形失真,則會引起電流諧波,從而進一步降低傳輸效率并將干擾引入市電電網(wǎng)。

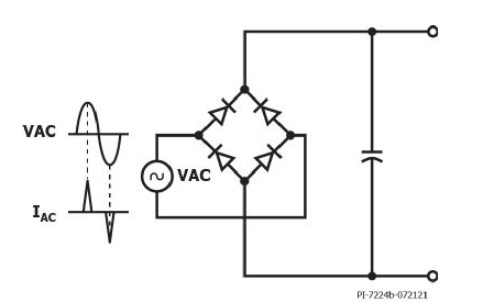

如果我們回到原來的整流級看波形,輸入交流電壓是一個傳統(tǒng)的正負極交替的對稱正弦波。然而,輸入電流表現(xiàn)為一系列尖峰,隨著輸入電壓的升高而增大。這是因為二極管導通(因此電流流動)只會在大電容充電時發(fā)生,此時VAC輸入電壓超過存儲在電容上的DC電壓。當VAC低于存儲的電容電壓時,存儲在大電容上的電荷將支持電源的輸出。在此期間,能量從電容轉移到負載,這會導致電容電壓下降。一旦AC電壓再次超過儲能電容上的(現(xiàn)在較低的)電壓,電容就會重新充電。這種短的充電窗口意味著輸入電流以三角形脈沖而不是正弦波的形式提供。

圖1:整流級的輸入電流表現(xiàn)為一系列包含大量諧波成分的尖峰信號,

這會污染AC線路

這種尖峰電流波形由一系列工頻諧波組成。諧波含量受到為保護配電網(wǎng)絡而制定的各種國家和國際法規(guī)的限制。圖1所示電路的功率因數(shù)往往非常低,約為0.5,與理想的1相去甚遠。

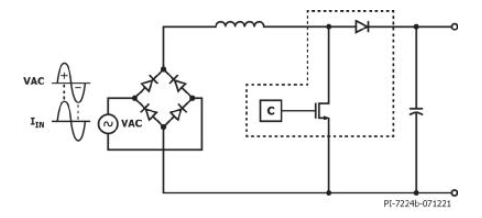

這個問題可以通過幾種不同的方式來解決。最簡單的方法是添加一個電感來抵消電路的電容分量 - 這種技術稱為無源功率因數(shù)校正。然而,無源功率校正的作用有限。在具有高功率輸出的應用中,所需電感的物理尺寸使其不切實際。在這種情況下,通常使用有源PFC電路來使電路的功率因數(shù)更接近于1,而不會對電路的尺寸產(chǎn)生負面影響。有源功率因數(shù)校正由PFC二極管、電感和MOSFET組成。MOSFET用作高頻開關,由執(zhí)行功率因數(shù)校正算法的控制器驅動。

開關電路強制輸入電流跟隨整流后的VAC輸入,并再次變?yōu)檫m當?shù)恼也ā@硐肭闆r下,正弦波具有低失真,以消除可污染AC線路的諧波電流。由于電壓和電流波形同相,功率因數(shù)也上升到接近理想值1。

圖2:具有有源功率因數(shù)校正功能的整流級將輸入電流變?yōu)檎也?/p>

實現(xiàn)有源PFC電路的一個簡單方法是使用Power Integrations的HiperPFS-4解決方案(見圖3)。HiperPFS-4器件包括一個超低反向恢復電荷二極管,通過最大限度地減少二極管的轉換損耗來實現(xiàn)高效率。它還具有可降低導通損耗的低RDS(ON)MOSFET和集成了許多安全功能的高級連續(xù)導通模式控制器。

圖3:Power IntegraTIons的HiperPFS-4

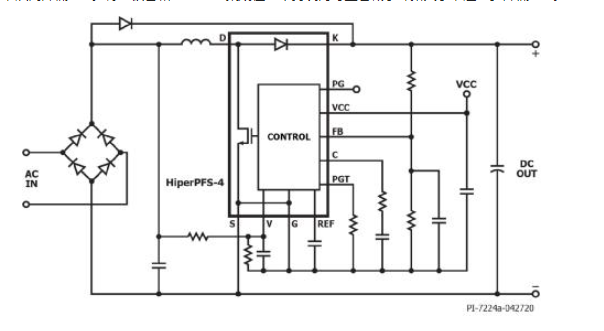

HiperPFS-4器件同時集成了功率因數(shù)校正二極管、MOSFET和控制器,這種高集成度有助于縮短開發(fā)時間并加快上市速度。將關鍵元件集成在一個封裝內(nèi)的另一個優(yōu)勢是最大限度地減少連線中的寄生電感。電路電感的降低有助于降低PFC二極管兩端的電壓應力和MOSFET的峰值漏源極電壓,從而提高電路的可靠性。此外,所使用的二極管具有軟恢復特性,可減少振鈴,從而降低EMI。將二極管和MOSFET集成在一個封裝內(nèi)可顯著減小環(huán)路大小,進一步降低EMI。

圖4:HiperPFS-4器件在同一個封裝內(nèi)集成了用于有源功率因數(shù)校正的關鍵元件,

以最大限度地減少連線中的寄生電感,從而降低功率開關上的di/dt感應電壓應力

總結

有源功率因數(shù)校正是減少有害的輸入諧波電流和提高功率因數(shù)的最佳方法。Power IntegraTIons開發(fā)了HiperPFS-4解決方案,將有源功率因數(shù)校正所需的關鍵元件集成到同一個封裝內(nèi)。這種方案可大幅減少輸入電流諧波并提高功率因數(shù),同時解決了在傳統(tǒng)電路設計常見的許多布局問題,例如降低電壓應力、EMI和寄生損耗。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17774瀏覽量

250767 -

功率因數(shù)

+關注

關注

10文章

567瀏覽量

39386

原文標題:【有獎直播】創(chuàng)客盛會——海內(nèi)外頂級Maker齊聚于直播間

文章出處:【微信號:gh_9b9470648b3c,微信公眾號:電子發(fā)燒友論壇】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

如何計算感性負載的功率因數(shù)?

功率因數(shù)補償?shù)姆椒ê图夹g

功率因數(shù)低的原因及解決方案

功率因數(shù)優(yōu)化方法 提高功率因數(shù)的好處

使用電力電容器提高功率因數(shù)

如何提高感性負載的功率因數(shù)

感性負載功率因數(shù)提高的特點

功率因數(shù)0.89被罰款如何解決

為什么要提高功率因數(shù)?提供功率因數(shù)的方法有哪些?

并聯(lián)電容對電路功率因數(shù)的影響

基于HiperPFS-4解決方案減少輸入電流諧波并提高功率因數(shù)

基于HiperPFS-4解決方案減少輸入電流諧波并提高功率因數(shù)

評論