“九層之臺,起于壘土”,基礎知識的重要性再怎么強調都不為過。在電路設計中也是如此,例如PCB,作為在幕后默默付出的無名英雄,往往容易被忽略,最終成為很多設計中的限制因素。這次,小編整理了關于PCB接地和去耦的相關文章,意在幫助各位工程師們查漏補缺,不斷完善電路設計知識哦。

JIE DI關于接地

完美接地vs.不完美接地

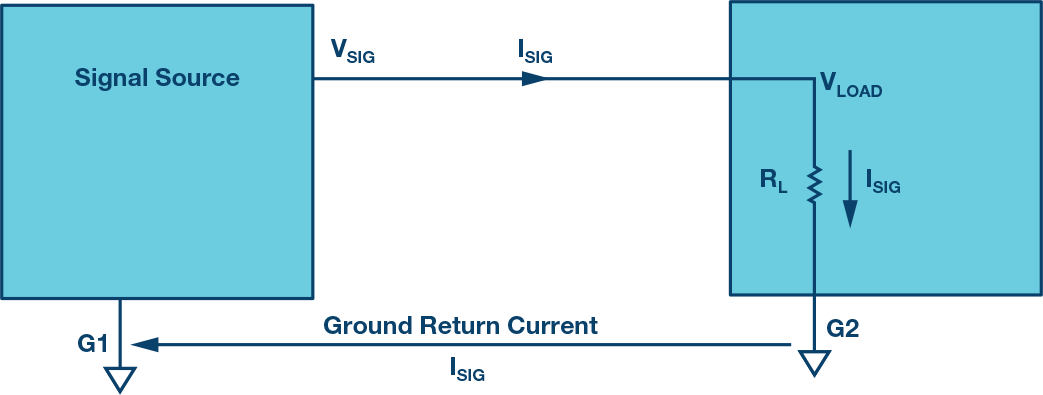

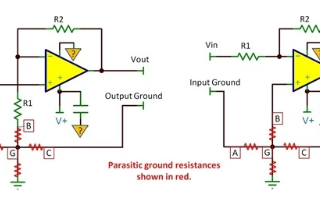

圖1a顯示信號源與負載之間隔開了一段距離,接地G1和G2通過一個回路連接起來。理想情況下,G1和G2之間的接地阻抗為0,因此接地回路電流不會在G1和G2之間產生一個差分電壓。

圖1a. 在電路中的任何一點,電流的算術和為0,或者說流出去的必會流回來。若G1和G2之間的阻抗為0,則G1和G2之間無差分電壓。

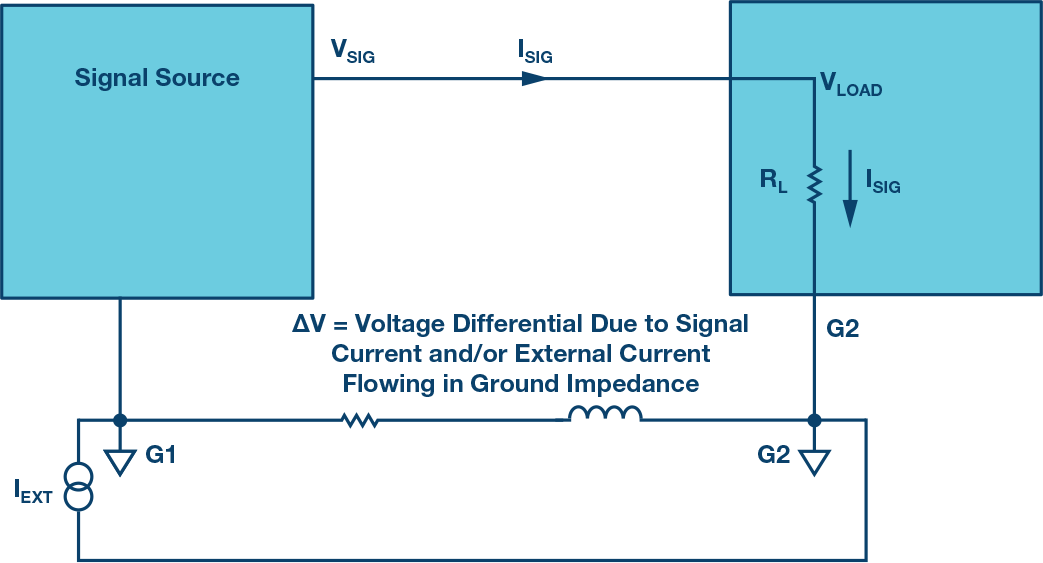

遺憾的是,讓回流路徑保持零阻抗是不可能的,接地回路阻抗在接地電流作用下,會在G1和G2之間產生一個誤差電壓ΔV。G1和G2之間的連接不僅有電阻,還有電感,這里忽略雜散電容的影響。但在本文“關于去耦”部分,您會了解到電源層和接地層之間的電容是如何幫助高頻去耦的。

圖1b. 接地阻抗中流動的信號和/或外部電流產生誤差電壓ΔV。

G1和G2之間流動的電流可以是信號電流或其他電路引起的外部電流。

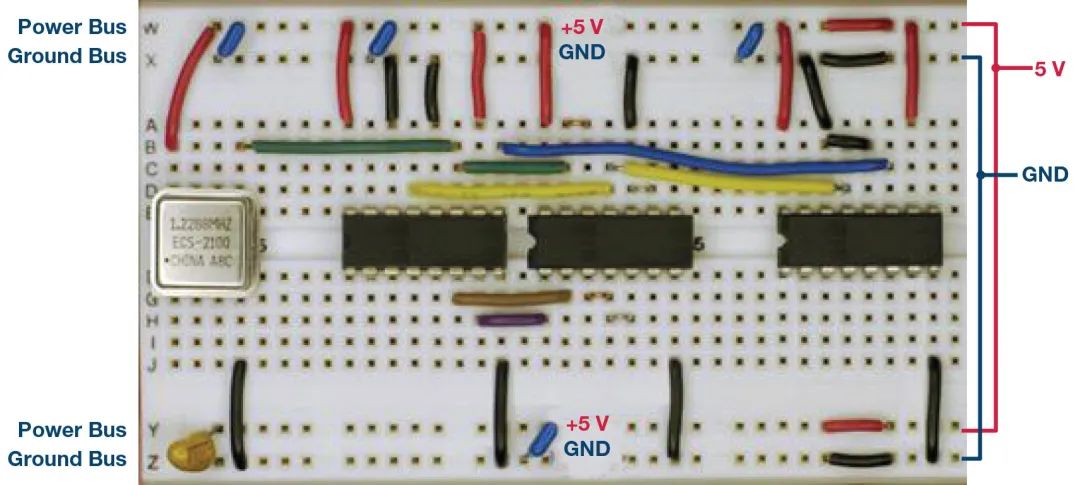

可以看到圖2試驗板中的總線阻抗如何既有阻性元件又有感性元件。接地總線阻抗是否會影響電路運行,不僅取決于電路的直流精度要求,而且取決于模擬信號頻率和電路中數字開關元件產生的頻率分量。

圖2. 采用無焊試驗板的電路

如果最大信號頻率為1 MHz,并且電路僅需要幾毫安(mA)電流,那么接地總線阻抗可能不是問題。然而,如果信號為100 MHz,并且電路驅動一個需要100 mA的負載,那么阻抗很可能會成為問題。

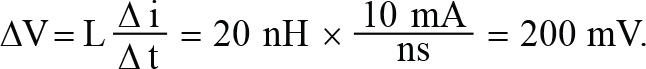

大部分情況下,由于"母線(buss wire)"在大多數邏輯轉換等效頻率下具有阻抗,將其用作數字接地回路是不能接受的。例如,#22標準導線具有約20 nH/英寸的電感和1 mΩ/英寸的電阻。由邏輯信號轉換產生的壓擺率為10 mA/ns的瞬態電流,在此頻率下流經1英寸的該導線,將形成200 mV的無用壓降:

對于具有2 V峰峰值范圍的信號,此壓降會轉化為約10%的誤差(大約3.5位精度)。即使在全數字電路中,該誤差也會大幅降低邏輯噪聲裕量。

對于低頻信號,該1 mΩ/英寸電阻也會產生一個誤差。例如,100 mA電流流過1英寸的#22標準導線時,產生的壓降約為:

一個2 V峰峰值范圍的信號數字化到16位精度時,其1 LSB = 2 V/216= 30.5 μV。因此,導線電阻引起的100 μV誤差約等于16位精度水平的3.3 LSB誤差。

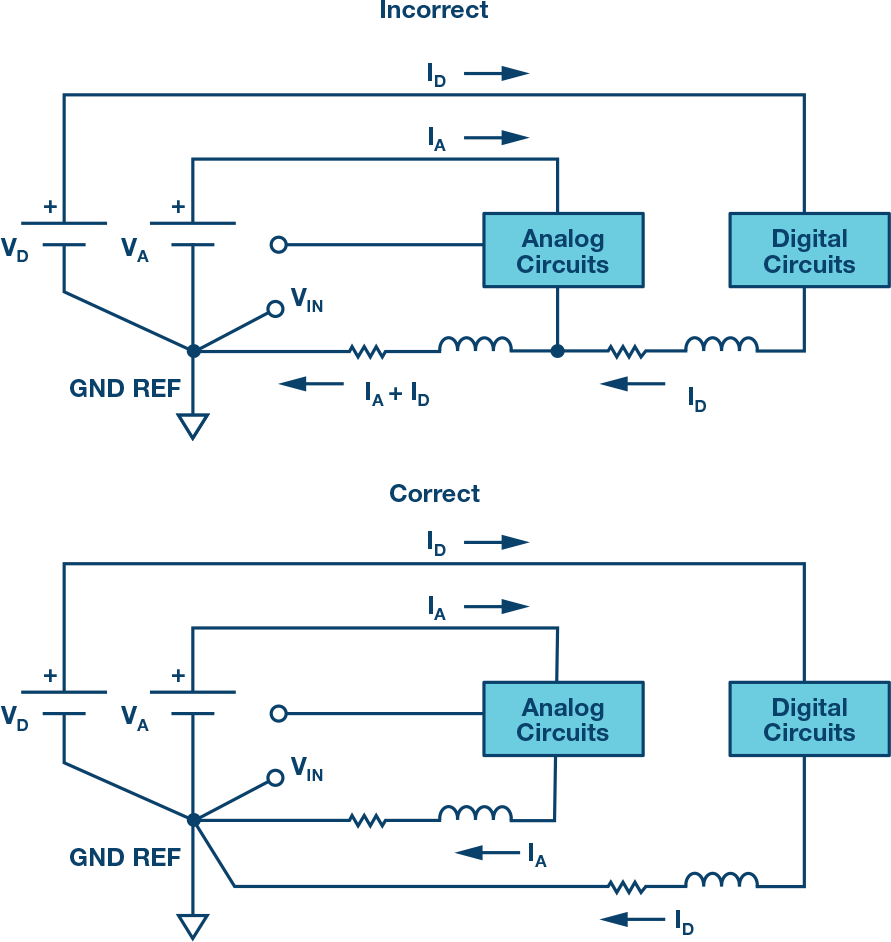

圖3顯示了模擬接地回路中流動的高噪聲數字電流如何在輸入模擬電路的電壓VIN中產生誤差。將模擬電路地和數字電路地連接在同一點(如下方的正確電路圖所示),可以在某種程度上緩解上述問題。

圖3.模擬電路和數字電路使用單點接地可降低高噪聲數字電路引起的誤差效應。

接地層在當今系統中必不可少

在無焊試驗板中,甚至在圖2所示的采用總線結構的電路板中,能夠用來降低接地阻抗的手段并不多。無焊試驗板在工業系統設計中是非常罕見的。實接地層是提供低阻抗回流路徑的工業標準方法。生產用印刷電路板一般有一層或多層專門用于接地。這種方法相當適合最終生產,但在原型系統中較難實現。關于將接地層運用到原型中的一些技術,請參見ADI官網上的文章《試驗板和原型制作技術》。

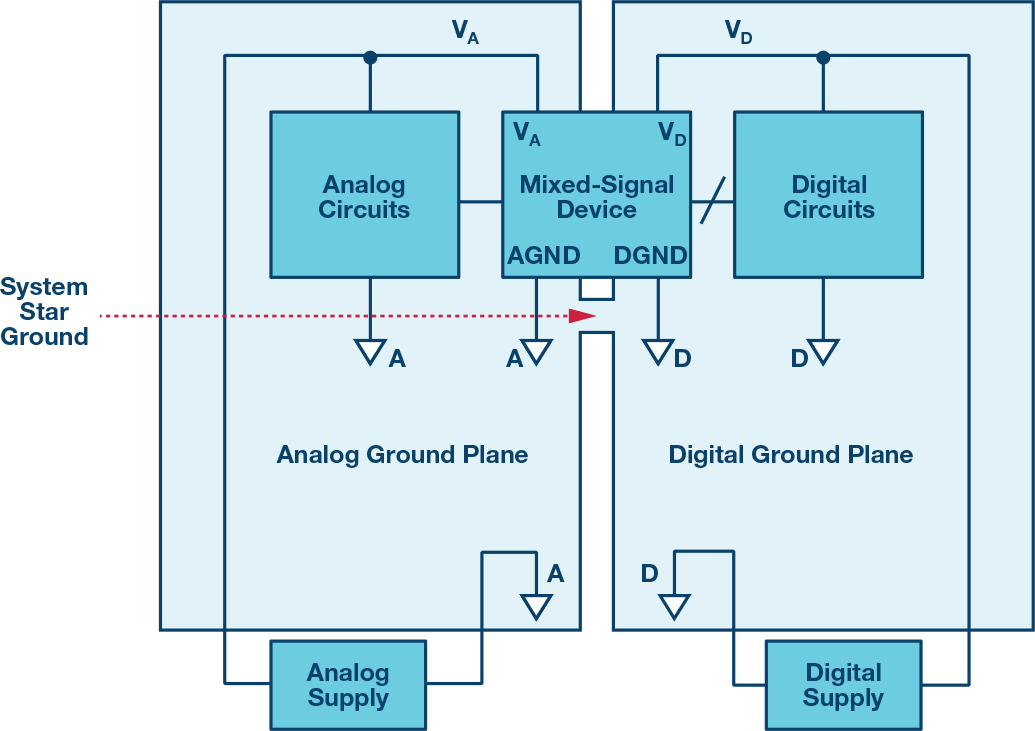

圖4.顯示了一個包含模擬電路、數字電路以及一個混合信號器件(模數轉換器或數模轉換器等)并針對PCB的典型接地安排。

圖4. 針對混合信號系統PCB的良好接地解決方案。

模擬電路和數字電路在物理上相隔離,分別位于各自的接地層上。混合信號器件橫跨兩個接地層,系統單點或星形接地是兩個接地層的連接點。

您應當知道,關于模擬接地和數字接地,還有其他已被證明有效的接地原理。建議您下載《PCB設計秘籍》了解更多詳情,當然,這些原理全都基于同樣的概念——分析模擬和數字電流路徑,然后采取措施以較大限度地減少它們之間的相互影響。

QU OU關于去耦

了解基于電源抑制參數的去耦需求

放大器和轉換器等模擬集成電路具有至少兩個或兩個以上電源引腳。對于單電源器件,其中一個引腳通常連接到地。諸如ADC和DAC等混合信號器件可以具有模擬和數字電源電壓以及I/O電壓。像FPGA這樣的數字IC還可以具有多個電源電壓,例如內核電壓、存儲器電壓和I/O電壓。

不管電源引腳的數量如何,IC數據手冊都詳細說明了每路電源的的允許范圍,包括推薦工作范圍和最大絕對值,而且為了保持正常工作和防止損壞,必須遵守這些限制。

然而,由于噪聲或電源紋波導致的電源電壓的微小變化—即便仍在推薦的工作范圍內—也會導致器件性能下降。

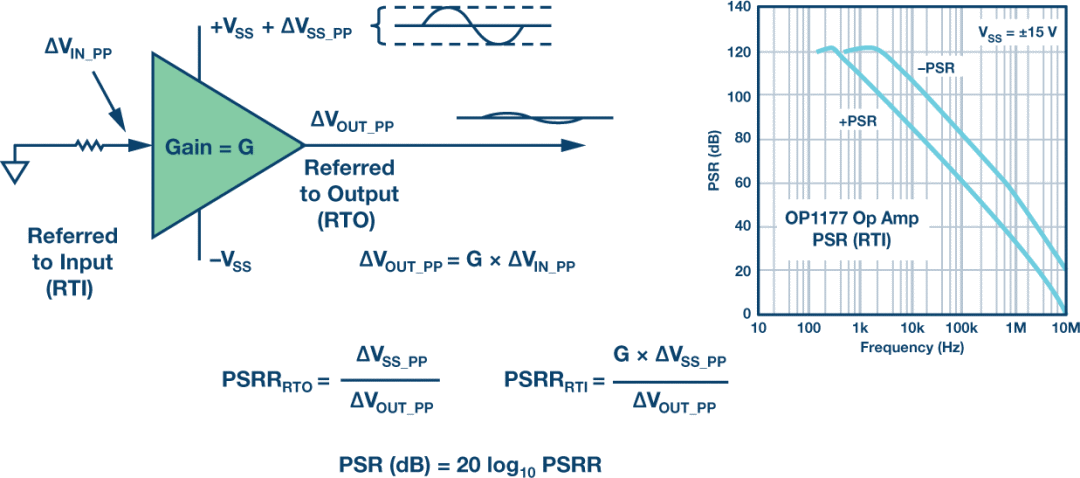

例如在放大器中,微小的電源變化會產生輸入和輸出電壓的微小變化,如圖5所示。

圖5.放大器的電源抑制顯示輸出電壓對電源軌變化的靈敏度。

放大器對電源電壓變化的靈敏度通常用電源抑制比(PSRR)來量化,其定義為電源電壓變化與輸出電壓變化的比值。

圖5顯示了典型高性能放大器(OP1177)的PSR隨頻率以大約6dB/8倍頻程(20dB/10倍頻程)下降的情況。圖中顯示了采用正負電源兩種情況下的曲線圖。盡管PSRR在直流下是120dB,但較高頻率下會迅速降低,此時電源線路上有越來越多的無用能量會直接耦合至輸出。

如果放大器正在驅動負載,并且在電源軌上存在無用阻抗,則負載電流會調制電源軌,從而增加交流信號中的噪聲和失真。

盡管數據手冊中可能沒有給出實際的PSRR,數據轉換器和其他混合信號IC的性能也會隨著電源上的噪聲而降低。電源噪聲也會以多種方式影響數字電路,包括降低邏輯電平噪聲容限,由于時鐘抖動而產生時序錯誤。

適當的局部去耦在PCB上是必不可少的

典型的4層PCB通常設計為接地層、電源層、頂部信號層和底部信號層。表面貼裝IC的接地引腳通過引腳上的過孔直接連接到接地層,從而較大限度地減少接地連接中的無用阻抗。

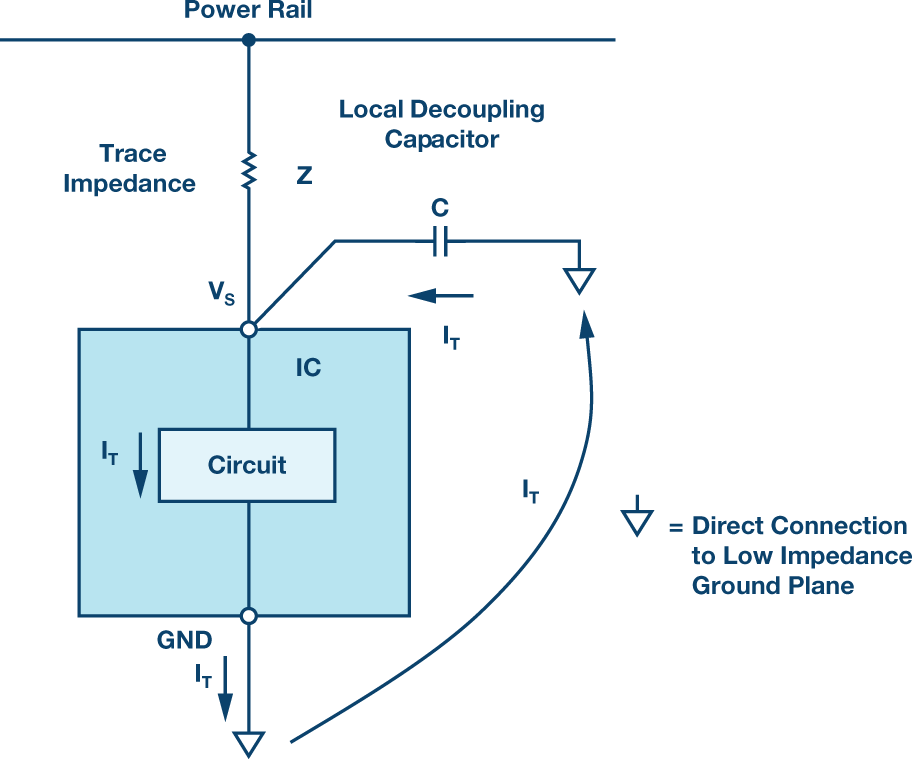

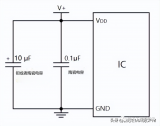

電源軌通常位于電源層,并且路由到IC的各種電源引腳。顯示電源和接地連接的簡單IC模型如圖6所示。

圖6. 顯示走線阻抗和局部去耦電容的IC模型。

IC內產生的電流表示為IT。流過走線阻抗Z的電流產生電源電壓VS的變化。如上所述,根據IC的PSR,這會產生各種類型的性能降低。

通過使用盡可能短的連接,將適當類型的局部去耦電容直接連接到電源引腳和接地層之間,可以較大限度地降低對功率噪聲和紋波的靈敏度。去耦電容用作瞬態電流的電荷庫,并將其直接分流到地,從而在IC上保持恒定的電源電壓。雖然回路電流路徑通過接地層,但由于接地層阻抗較低,回路電流一般不會產生明顯的誤差電壓。

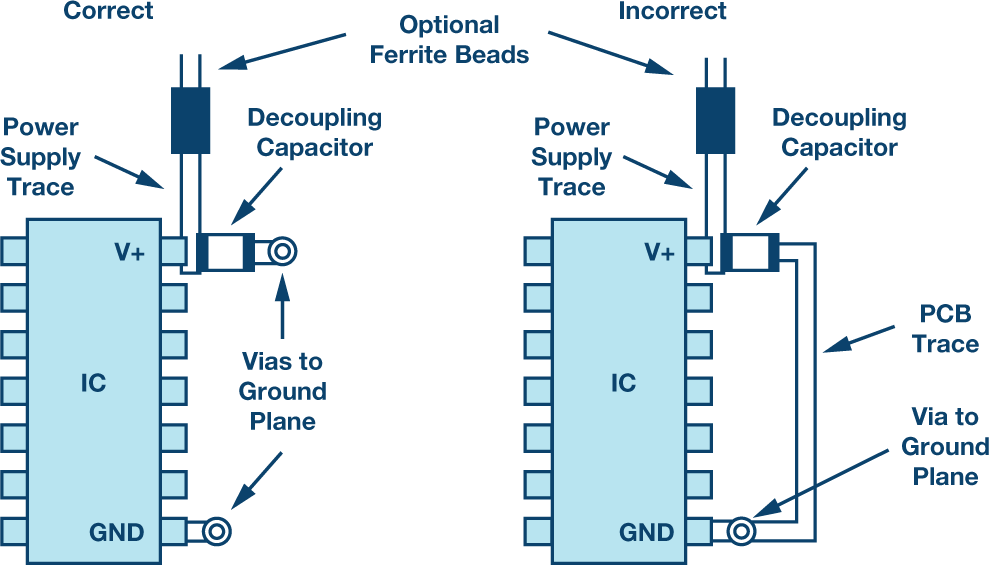

圖7顯示了高頻去耦電容必須盡可能靠近芯片的情況。否則,連接走線的電感將對去耦的有效性產生不利影響。

圖7. 高頻去耦電容的正確和錯誤放置。

圖7左側,電源引腳和接地連接都可能短,所以是有效的配置。然而在圖7右側中,PCB走線內的額外電感和電阻將造成去耦方案的有效性降低,且增加封閉環路可能造成干擾問題。

選擇正確類型的去耦電容

低頻噪聲去耦通常需要用電解電容(典型值為1μF至100μF),以此作為低頻瞬態電流的電荷庫。將低電感表面貼裝陶瓷電容(典型值為0.01μF至0.1μF)直接連接到IC電源引腳,可較大程度地抑制高頻電源噪聲。所有去耦電容必須直接連接到低電感接地層才有效。此連接需要短走線或過孔,以便將額外串聯電感降至低點。

大多數IC數據手冊在應用部分說明了推薦的電源去耦電路,用戶應始終遵循這些建議,以確保器件正常工作。

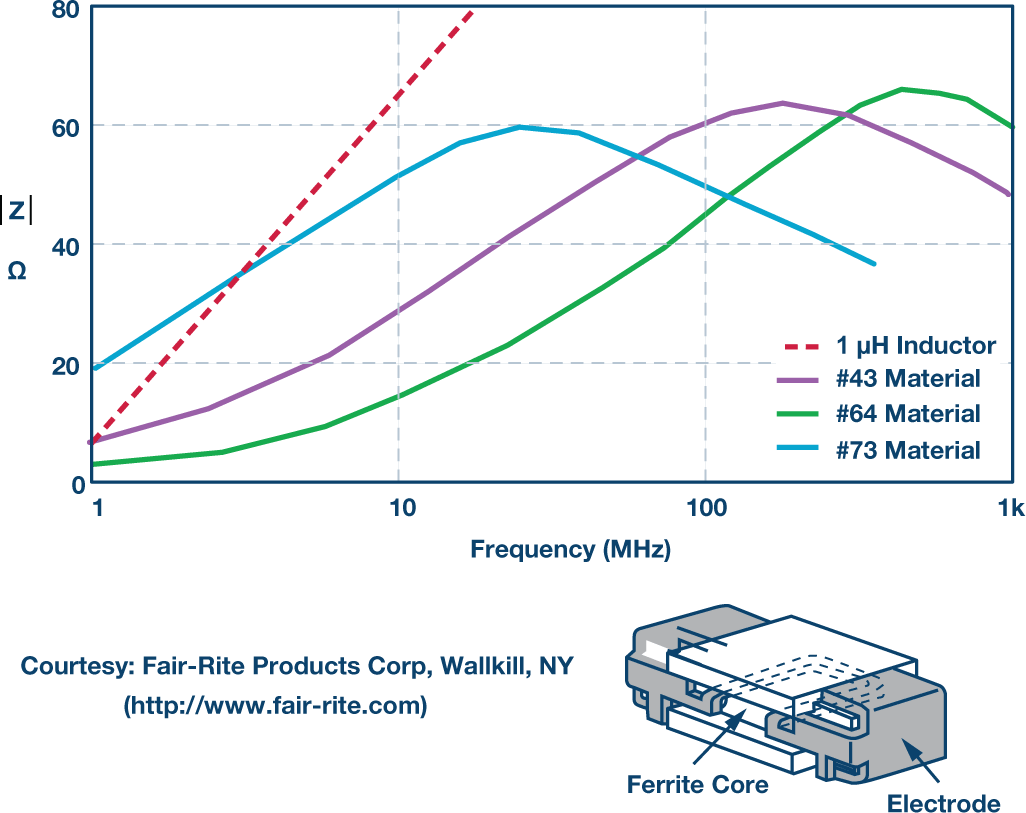

鐵氧體磁珠(以鎳、鋅、錳的氧化物或其他化合物制造的絕緣陶瓷)也可用于在電源濾波器中去耦。鐵氧體在低頻下(<100kHz)為感性—因此對低通LC去耦濾波器有用。100kHz以上,鐵氧體成阻性(低Q)。鐵氧體阻抗與材料、工作頻率范圍、直流偏置電流、匝數、尺寸、形狀和溫度成函數關系。

鐵氧體磁珠并非始終必要,但可以增強高頻噪聲隔離和去耦,通常較為有利。這里可能需要驗證磁珠永遠不會飽和,特別是在運算放大器驅動高輸出電流時。當鐵氧體飽和時,它就會變為非線性,失去濾波特性。

請注意,某些鐵氧體甚至可能在完全飽和前就是非線性。因此,如果需要功率級,以低失真輸出工作,當原型在此飽和區域附近工作時,應檢查其中的鐵氧體。典型鐵氧體磁珠阻抗如圖8所示。

圖8. 鐵氧體磁珠的阻抗。

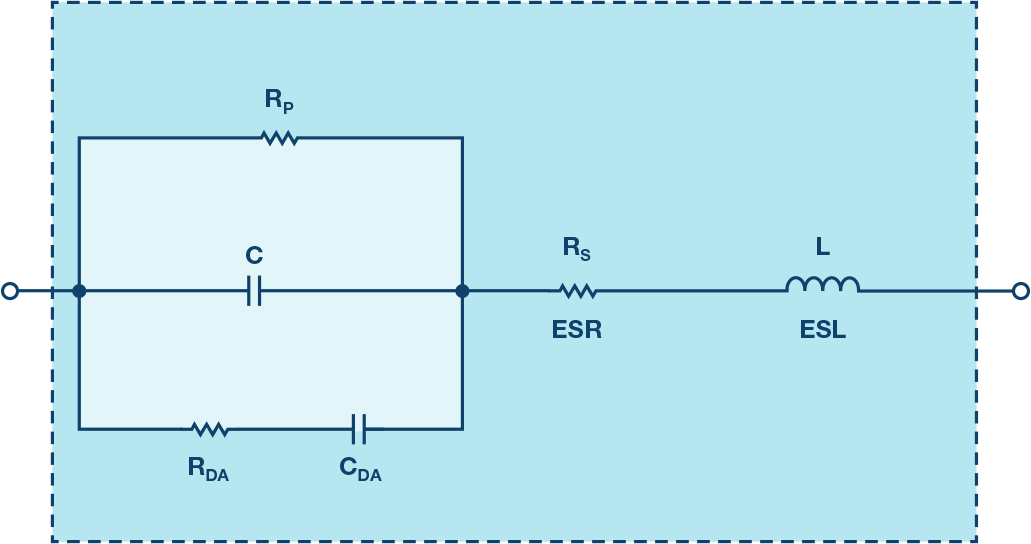

在為去耦應用選擇合適的類型時,需要仔細考慮由于寄生電阻和 電感產生的非理想電容性能。

實際電容及其寄生效應

圖9所示為實際電容的模型。電阻RP代表絕緣電阻或泄漏,與標稱電容(C)并聯。第二個電阻RS(等效串聯電阻或ESR)與電容串聯,代表電容引腳和電容板的電阻。

圖9.實際電容等效電路包括寄生元件。

電感L(等效串聯電感或ESL)代表引腳和電容板的電感。最后,電阻RDA和電容CDA一起構成稱為電介質吸收(DA)現象的簡化模型。在采樣保持放大器(SHA)之類精密應用中使用電容時,DA可造成誤差。但在去耦應用中,電容的DA不重要,予以忽略。

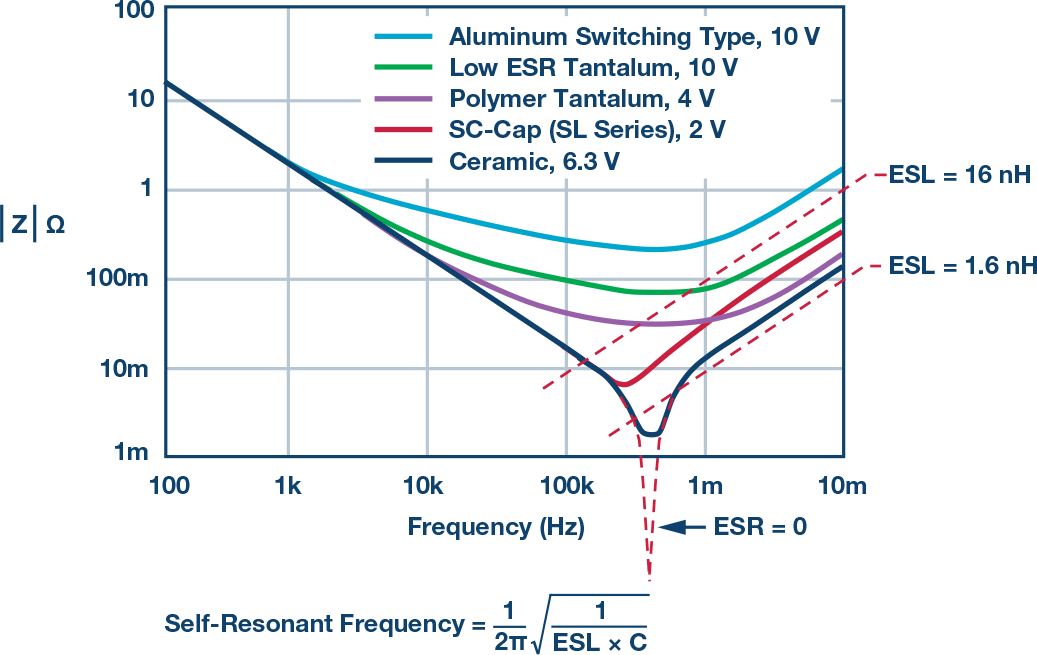

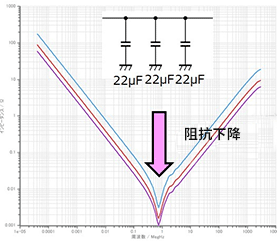

圖10顯示了不同類型的100 μF電容的頻率響應。理論上,理想電容的阻抗隨著頻率提高而單調降低。實際操作中,ESR使阻抗曲線變得平坦。隨著頻率不斷升高,阻抗由于電容的ESL而開始上升。"膝部"的位置和寬度將隨著電容結構、電介質和電容值而變化。因此,在去耦應用中,常常可以看到較大值電容與較小值電容并聯。較小值電容通常具有較低ESL,在較高頻率時仍然像一個電容。電容并聯組合覆蓋的頻率范圍比組合中任何一個電容的頻率范圍都要寬。

圖10. 各種100μF電容的阻抗

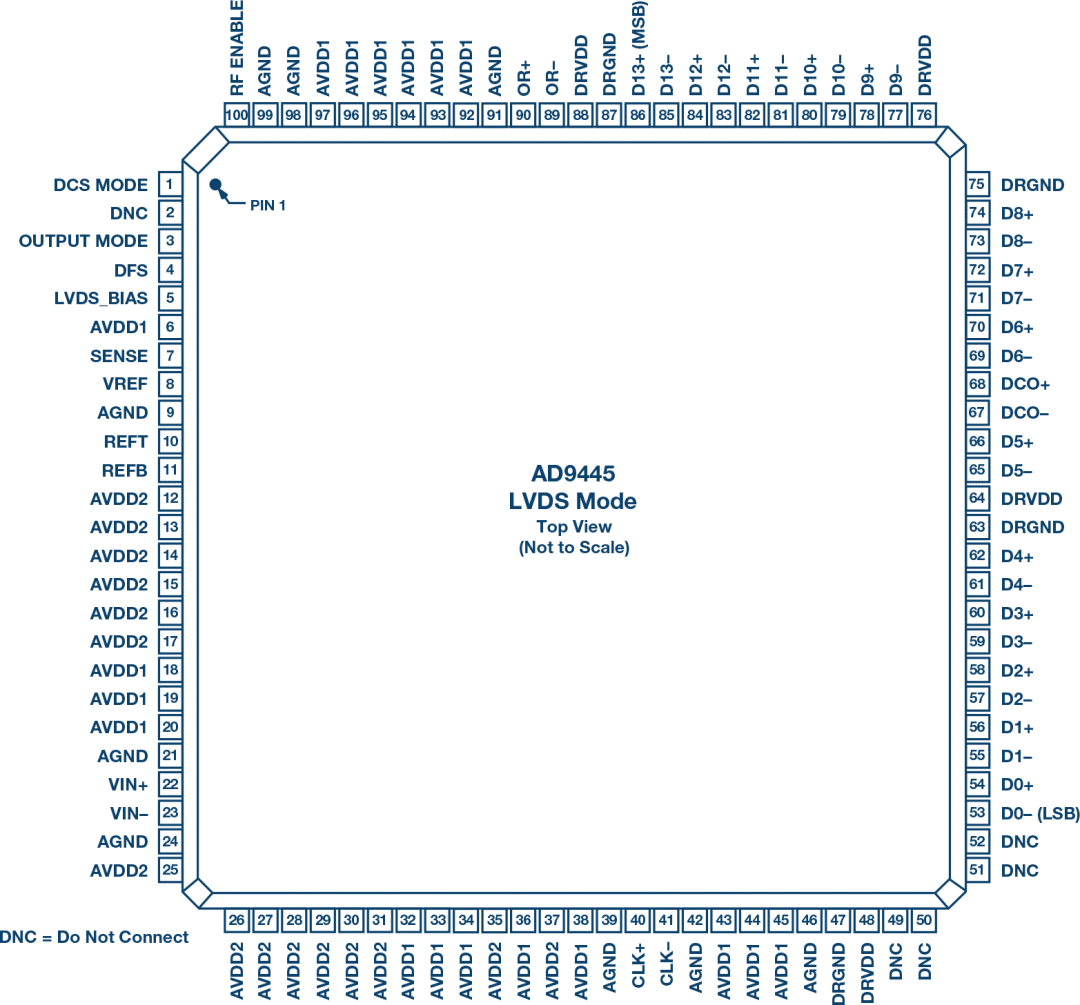

電容自諧振頻率就是電容電抗(1/ωC)等于ESL電抗(ωESL)時的頻率。對這一諧振頻率等式求解得到下式:

所有電容的阻抗曲線都與圖示的大致形狀類似。雖然實際曲線圖有所不同,但大致形狀相同。最小阻抗由ESR決定,高頻區域由ESL決定,而后者在很大程度上受封裝樣式影響。

去耦電容類型

電解電容系列具有寬值范圍、高電容體積比和廣泛的工作電壓,是極佳的高性價比低頻濾波器元件。該系列包括通用鋁電解開關類型,提供10 V以下直至約500 V的工作電壓,大小為1 μF至數千μF不等(以及成比例的外形尺寸)。

所有電解電容均有極性,因此無法耐受約1 V以上的反向偏置電壓而不造成損壞。此類元件具有相對較高的漏電流(可能為數十μA),具體漏電流在很大程度上取決于特定系列的設計、電氣尺寸、額定電壓及施加電壓。不過,漏電流不可能是基本去耦應用的主要因素。

大多數去耦應用不建議使用通用鋁電解電容。不過,鋁電解電容有一個子集是"開關型",其設計并規定用于在最高達數百kHz的頻率下處理高脈沖電流,且損耗很低。此類電容在高頻濾波應用中可直接媲美固態鉭電容,且具有更廣泛的可用值。

固態鉭電解電容一般限于50 V或更低的電壓,電容為500 μF或更低。給定大小時,鉭電容比鋁開關電解電容呈現出更高的電容體積比,且具有更高的頻率范圍和更低的ESR。鉭電容一般也比鋁電解電容更昂貴,對于浪涌和紋波電流,必須謹慎處理應用。

使用有機或聚合物電解質的高性能鋁電解電容也已問世。這些電容系列擁有略低于其他電解類型的ESR和更高的頻率范圍,另外低溫ESR下降也較小。此類元件使用鋁聚合物、特殊聚合物、POSCAP和OS-CON等標簽。

陶瓷或多層陶瓷(MLCC)具有尺寸緊湊和低損耗特性,通常是數MHz以上的優選電容材料。不過,陶瓷電介質特性相差很大。對于電源去耦應用,一些類型優于其他類型。采用X7R的高K電介質配方時,陶瓷電介質電容的值最高可達數μF。Z5U和Y5V型的額定電壓最高可達200 V。X7R型在直流偏置電壓下的電容變化小于Z5U和Y5V型,因此是較佳選擇。

NP0(也稱為COG)型使用介電常數較低的配方,具有標稱零TC和低電壓系數(不同于較不穩定的高K型)。NP0型的可用值限于0.1 μF或更低,0.01 μF是更實用的上限值。

多層陶瓷(MLCC)表面貼裝電容的極低電感設計可提供近乎較優的RF旁路,因此越來越頻繁地用于10 MHz或更高頻率下的旁路和濾波。更小的陶瓷芯片電容工作頻率范圍可達1 GHz。對于高頻應用中的這些及其他電容,通過選擇自諧振頻率高于最高目標頻率的電容,可確保有用值符合需要。

薄膜型電容一般使用繞線,增加了電感,因此不適合電源去耦應用。此類型更常用于音頻應用,此時需要極低電容和電壓系數。

最后,務必選擇擊穿電壓至少為電源電壓兩倍的電容,否則當電路上電時,可能會發生意外。

不良去耦技術對性能的影響

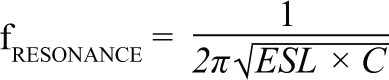

圖11顯示了1.5 GHz高速電流反饋運算放大器AD8000的脈沖響應。兩幅示波器圖均是利用評估板獲得。左側曲線顯示正確去耦的響應,右側曲線顯示同一電路板上去除去耦電容后的響應。兩種情況中,輸出負載均為100 Ω。

圖11. 去耦對AD8000運算放大器性能的影響

示波器圖說明,沒有去耦時,輸出表現出不良響鈴振蕩,這主要是因為電源電壓隨負載電流變化而偏移。

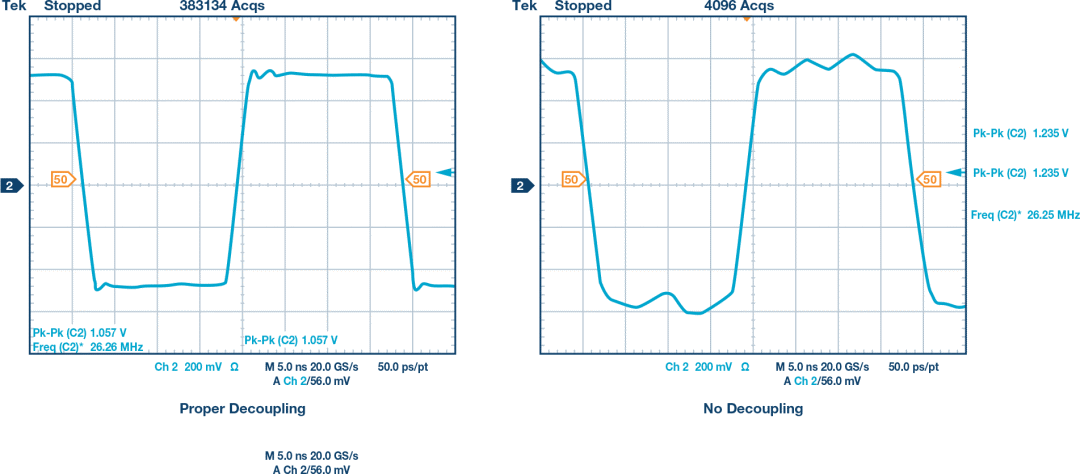

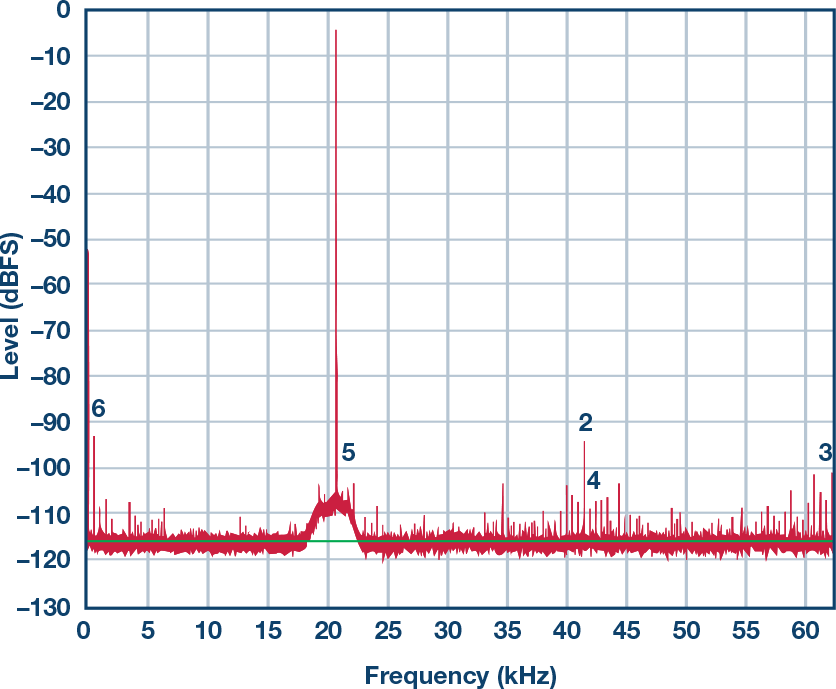

現在考察正確及錯誤去耦對14位、105 MSPS/125 MSPS高性能數據轉換器ADC AD9445 的影響。雖然轉換器通常無PSRR規格,但正確去耦仍非常重要。圖12顯示正確設計電路的FFT輸出。這種情況下,我們使用AD9445的評估板——注意頻譜很干凈。

圖12. 正確去耦時AD9445評估板的FFT圖

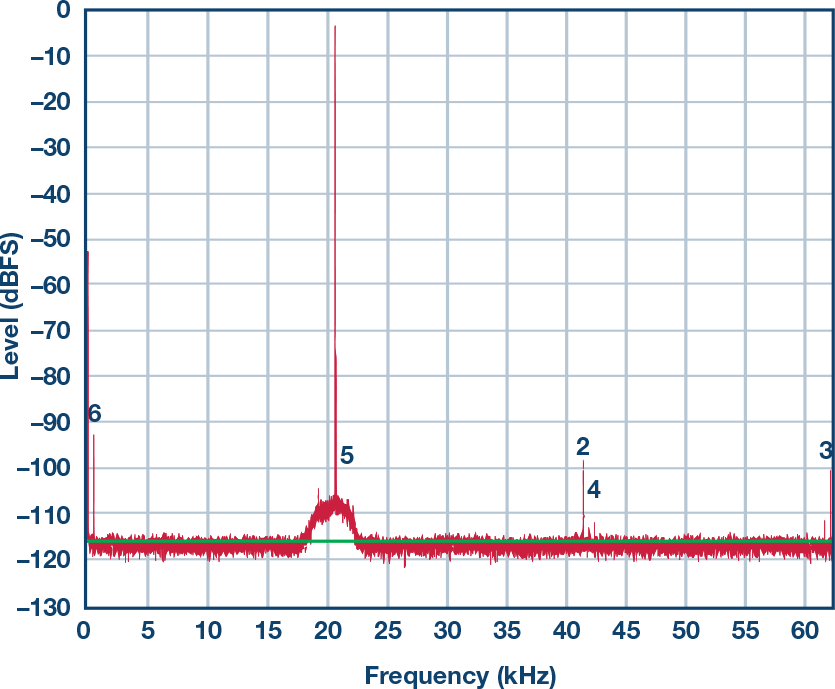

AD9445的引腳排列如圖12所示。請注意,電源和接地引腳有多個。這是為了降低電源阻抗(并聯引腳)。

圖13. AD9445引腳排列圖

模擬電源引腳有33個。18個引腳連接到AVDD1(電壓為3.3 V ± 5%),15個引腳連接到AVDD2(電壓為5 V ± 5%)。DVDD(電壓為5 V ± 5%)引腳有4個。在本實驗所用的評估板上,每個引腳有0.1 μF陶瓷去耦電容。此外,沿電源走線還有數個10 μF電解電容。

圖14顯示了從模擬電源去除去耦電容后的頻譜。請注意,高頻雜散信號增加了,還出現了一些交調產物(低頻成分)。信號SNR已顯著降低。本圖與上圖的差異是去除了去耦電容。

圖14. 從模擬電源去除去耦電容后AD9445評估板的FFT圖

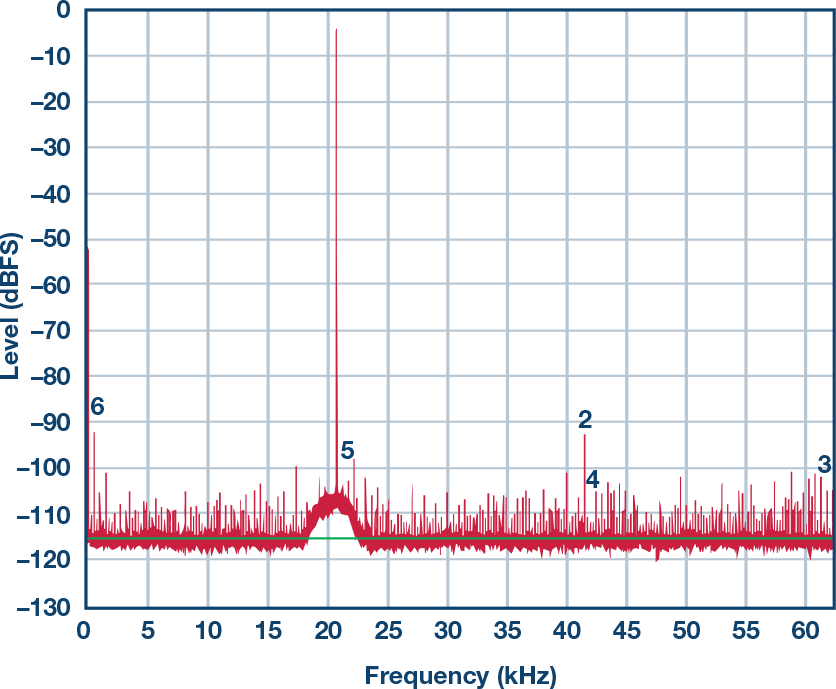

圖15顯示從數字電源去除去耦電容的結果。注意雜散同樣增加了。另外應注意雜散的頻率分布。這些雜散不僅出現在高頻下,而且跨越整個頻譜。本實驗使用轉換器的LVDS版本進行。可以想象,CMOS版本會更糟糕,因為LVDS的噪聲低于飽和CMOS邏輯。

圖15. 從數字電源去除去耦電容后AD9445評估板的SNR圖

這些實驗表明,除去大多數或所有去耦電容會導致性能降低,但要分析或預測除去一兩個去耦電容的影響是很困難的。當拿不定主意時,優質策略是放上電容。雖然成本略有增加,但消除了性能降低的風險,這樣做通常是值得的。

6分鐘帶您了解電量計產品MAX17260你留“”,我送禮▽▽▽ 小編將從視頻的點贊粉絲中隨機抽取5位幸運兒送出ADI幸運小獎品 查看往期內容↓↓↓

原文標題:聚焦PCB基礎知識,“接地和去耦”的問題你搞清楚了嗎?

文章出處:【微信公眾號:亞德諾半導體】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

pcb

+關注

關注

4319文章

23099瀏覽量

397892 -

電流

+關注

關注

40文章

6860瀏覽量

132194 -

接地

+關注

關注

7文章

767瀏覽量

45669

原文標題:聚焦PCB基礎知識,“接地和去耦”的問題你搞清楚了嗎?

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

接地和去耦的基礎知識:去耦的基本電路元件電容

旁路電容和去耦電容基礎知識

去耦電容的接地原則

接地和去耦:現在就開始學習基礎知識, 為日后鋪平道路!第三部分:去耦續篇資料下載

關于PCB接地和去耦的基礎知識

關于PCB接地和去耦的基礎知識

評論