緩沖區其實就是一個存儲區域,它是由專門的硬件寄存器所組成的。

緩沖區根據其對應的輸入設備和輸出設備,分為輸入緩沖區和輸出緩沖區。

使用硬件作為緩沖區的成本較高,容量也較小,一般僅用在對速度非常高的場合(存儲器管理寄存器,有對頁表訪問的頻率較高,因此使用速度很快的聯想寄存器來存放頁表項的副本)。

一般情況下更多的是使用內存作為緩沖區,緩沖區就是一塊內存區。

緩沖區的作用

減少對CPU的中斷頻率,放寬對CPU中斷相應的時間限制;

解決數據粒度不匹配的問題;

提高CPU和IO設備之間的并行性;

緩和CPU和IO設備之間速度不匹配矛盾。

緩沖區的作用就是為了解決速度不匹配的問題,高速的cpu與內存,內存與硬盤,cpu與io等速度不匹配的問題。

還有在一些廠商資料中還被寫為CacheBuffer。緩沖區的基本作用是平衡內部與外部的DTR。

本文綜合整理自百度百科、雪V歌、亓旎豆晗琴

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

緩沖區

+關注

關注

0文章

33瀏覽量

9138 -

寄存器

+關注

關注

31文章

5357瀏覽量

120689 -

緩沖

+關注

關注

0文章

52瀏覽量

17837

發布評論請先 登錄

相關推薦

AMD Zen 4處理器悄然禁用循環緩沖區

近日,AMD在更新BIOS后,對Zen 4架構的處理器進行了一項未公開說明的更改:禁用了循環緩沖區(Loop Buffer)功能。這一變化引發了業界和用戶的廣泛關注。 循環緩沖區作為CPU前端的一個

單片機中的幾種環形緩沖區的分析和實現

單片機中的幾種環形緩沖區的分析和實現一、簡介環形緩沖區(RingBuffer)是一種高效的使用內存的方法,它將一段固定長度的內存看成一個環形結構,用于存儲數據,能夠避免使用動態申請內存導致的內存碎片

ESP8266是否可以添加AT命令并使接收緩沖區大小可調?

是否可以添加 AT 命令并使接收緩沖區大小可調?

在Arduino上,我總是丟棄數據字節,而arduino硬件串行只有64字節的緩沖區,看起來ESP8266有256個字節。

發表于 07-17 07:36

ESP8266有雙緩沖區嗎?

我想實時傳輸一些信號的測量數據。信號的采樣周期為 1 ms。我想每 500 毫秒發送 2048 字節(一個數據包)。ESP8266有雙緩沖區(2x 2048字節)嗎?其想法是計數填充一個緩沖區(周期

發表于 07-16 07:29

創建DMA通道時,能否將DMA緩沖區的大小指定為8字節,并將DMA緩沖區的編號指定為1?

創建 DMA 通道時,能否將 DMA 緩沖區的大小指定為 8 字節,并將 DMA 緩沖區的編號指定為 1?

發表于 05-31 07:46

stm32野火開發板上做USB通信,PC端USB的緩沖區和串口緩沖區的大小是多少?

ADC采集的波形還原,也就是畫圖。

我就不明白,安裝的驅動作用是?修改了PID和VID。

還有PC端的USB作用不是太明白?是一下那種情況:

1、stm32端傳過來的數據根本沒有經過USB的緩沖區,而是

發表于 05-17 14:02

實現穩健的微控制器到FPGA SPI接口: 雙緩沖區!

在介紹雙緩沖器之前,我們將簡要探討Verilog 脈寬調制器 (PWM) 的工作原理。這一點很重要,因為雙緩沖區最好被看作是硬件模塊 (如 PWM) 的可尋址接口。

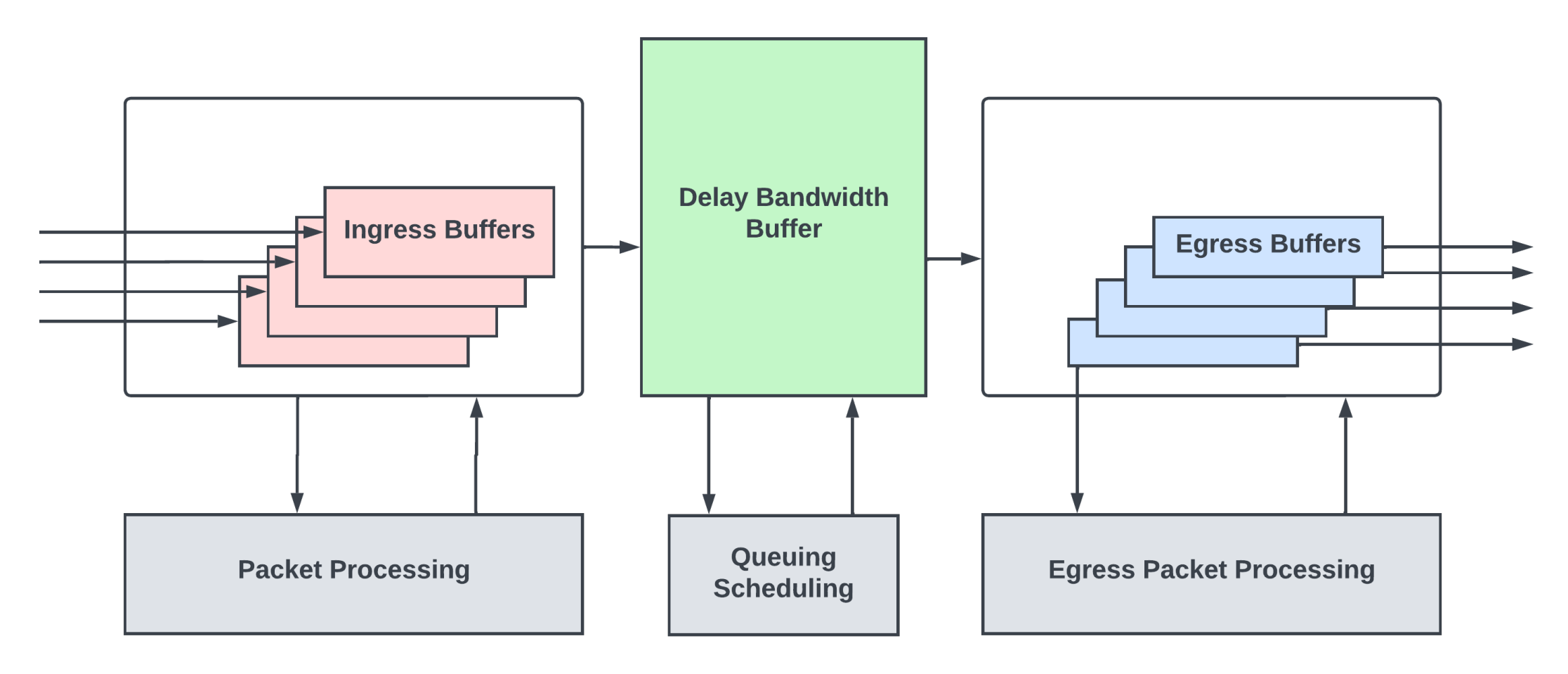

交換機與路由器緩沖區:尋找完美大小

*本文系SDNLAB編譯自瞻博網絡技術專家兼高級工程總監Sharada Yeluri領英 在路由器和交換機中,緩沖區至關重要,可以防止網絡擁塞期間的數據丟失。緩沖區到底要多大?這個問題在

交換芯片緩沖區大小是什么

交換芯片緩沖區大小并不一定是固定的。緩沖區的設計和實現會根據芯片的具體型號、規格以及應用場景的不同而有所差異。一些交換芯片可能具有固定大小的緩沖區,以滿足特定的性能需求或成本限制。然而,隨著技術

使用UART FIFO緩沖區時,緩沖區中的數據有時會損壞的原因?

= XMC_USIC_CH_PARITY_

MODE_NONE

兩個 UART 通道都使用 FIFO 緩沖區,沒有任何中斷。

緩沖區每 1 毫秒 TLE9243QK_BASE_BOARD 檢查一次標志是否有可供讀取

發表于 03-06 06:59

沒有辦法通過FX3固件檢查緩沖區是卡住了還是已滿?

我正在嘗試通過多通道 DMA 緩沖區直播 1080p60 視頻,但是我們遇到了一個問題,即在向 FX3 寫入一定數量的緩沖區之后,我們看到當前線程 WATERMARK 和 READY 標志保持不變

發表于 02-23 08:01

什么是緩沖區?有什么作用

什么是緩沖區?有什么作用

評論