這篇文章獻給那些剛開始或即將開始設計硬件電路的人,剛剛開始接觸電路板的時候,你可能充滿了疑惑同時又帶著些興奮。

在網上許多關于硬件電路的經驗知識讓人目不暇接,像信號完整性、EMI準會把你搞暈,別急,一切要慢慢來。

01. 總體思路

設計硬件電路,大的框架和架構要搞清楚,但要做到這一點還真不容易。

有些大框架也許自己的老板、老師已經想好,自己只是把思路具體實現。

但也有些要自己設計框架的,那就要搞清楚要實現什么功能,然后找找有否能實現同樣或相似功能的參考電路板

要懂得盡量利用他人的成果,越是有經驗的工程師越會懂得借鑒他人的成果。

02. 理解電路

如果你找到了的參考設計,那么恭喜你,你可以節約很多時間了,包括前期的設計和后期的調試。

馬上就copy?NO,還是先看懂并理解了再說,一方面能提高我們的電路理解能力,而且能避免設計中的錯誤。

03. 沒有找到參考設計?

沒關系,先確定大IC芯片找datasheet,看其關鍵參數是否符合自己的要求,哪些才是自己需要的關鍵參數,以及能否看懂這些關鍵參數,都是硬件工程師的能力的體現,這也需要長期地慢慢地積累。

這期間要善于提問,因為自己不懂的東西,別人往往一句話就能點醒你,尤其是硬件設計。

04. 設計硬件電路

硬件電路設計主要是三個部分原:理圖、pcb 以及物料清單(BOM)表。

原理圖設計就是將前面的思路轉化為電路原理圖,它很像我們教科書上的電路圖。

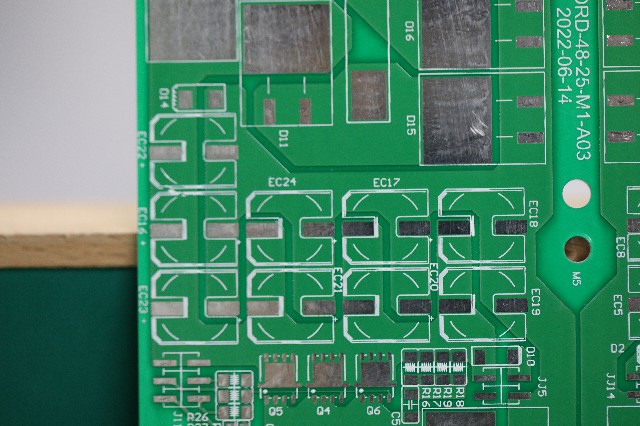

pcb涉及到實際的電路板,它根據原理圖轉化而來的網表(網表是溝通原理圖和pcb之間的橋梁),而將具體的元器件的封裝放置(布局)在電路板上,然后根據飛線(也叫預拉線)連接其電信號(布線)。

完成了pcb布局布線后,要用到哪些元器件應該有所歸納,所以我們將用到BOM表。

05. 用什么工具?

Protel,也就是altimum,容易上手,在國內也比較流行,應付一般的工作已經足夠,適合初入門的設計者使用。

其實無論用簡單的protel或者復雜的cadence工具,硬件設計大環節是一樣的。

protel上的操作類似windwos,是post-command型的。

而cadence的產品conceptallegro是pre-command型的,用慣了protel突然轉向cadence的工具,會不習慣就是這個原因。

現在談一下設計流程

01. 原理圖庫建立

要將一個新元件擺放在原理圖上,我們必須得建立元件的庫。

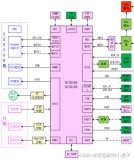

庫中主要定義了該新元件的管腳定義及其屬性,并且以具體的圖形形式來代表。

我們常常看到的是一個矩形(代表其IC BODY),周圍許多短線(代表IC管腳)。

protel創建庫及其簡單,而且因為用的人多,許多元件都能找到現成的庫,這一點對使用者極為方便。

應搞清楚ic body、ic pins、input pin、output pin、analog pin、digital pin、power pin等區別。

02. 畫原理圖

有了充足的庫之后,就可以在原理圖上畫圖了,按照datasheet和系統設計的要求,通過wire把相關元件連接起來,在相關的地方添加line和text注釋。

wire和line的區別在于,前者有電氣屬性,后者沒有。

wire適用于連接相同網絡,line適用于注釋圖形。

這個時候,應搞清一些基本概念,如:wire、line、bus、part、footprint等等。

例如,post-command,例如我們要拷貝一個object(元件),我們要先選中這個object,然后按ctrl+C,然后按ctrl+V(copy命令發生在選中object之后)。

這種操作windows和protel都采用的這種方式,但是concept就是另外一種方式,我們叫做pre-command。

同樣我們要拷貝一個東西,先按ctrl+C,然后再選中object,再在外面單擊(copy命令發生在選中 object之前)。

03. 生成netlist

做完上一步,我們就可以生成netlist了,這個netlist是原理圖與pcb之間的橋梁。

原理圖是我們能認知的形式,電腦要將其轉化為pcb,就必須將原理圖轉化它認識的形式netlist,然后再處理、轉化為pcb。

04. 電氣規則檢查

得到netlist馬上畫pcb?別急,先做ERC先,ERC是電氣規則檢查的縮寫。

它能對一些原理圖基本的設計錯誤進行排查,如多個output接在一起等問題。

但是一定要仔細檢查自己的原理圖,不能過分依賴工具,畢竟工具并不能明白你的系統,它只是純粹地根據一些基本規則排查。

05. 獲得pcb

從netlist得到了pcb,一堆密密麻麻的元件,和數不清的飛線是不是讓你嚇了一跳?別急還得慢慢來。

06. 確定板框大小

在keepout區(或mechanic區)畫個板框,這將限制了你布線的區域。需要根據需求好考慮板長,板寬(有時,還得考慮板厚)。

當然了,疊層也得考慮好,疊層的意思就是,板層有幾層,怎么應用,比如板總共4層,頂層走信號,中間第一層鋪電源,中間第二層鋪地,底層走信號。

07. 布局

確定完板框之后,就該元件布局(擺放)了,布局這步極為關鍵。

它往往決定了后期布線的難易,哪些元器件該擺正面,哪些元件該擺背面,都要有所考量。

但是這些都是一個仁者見仁,智者見智的問題,從不同角度考慮擺放位置都可以不一樣。

其實自己畫了原理圖,明白所有元件功能,自然對元件擺放有清楚的認識,如果讓一個不是畫原理圖的人來擺放元件,其結果往往會讓你大吃一驚^_^。

對于初入門的,注意模擬元件,數字元件的隔離,以及機械位置的擺放,同時注意電源的拓撲就可以了。

08. 布線

接下來就是布線,這與布局往往是互動的,有經驗的人往往在開始就能看出哪些地方能布線成功,如果有些地方難以布線還需要改動布局。

對于fpga設計來說往往還要改動原理圖來使布線更加順暢。

布線和布局問題涉及的因素很多,對于高速數字部分,因為牽扯到信號完整性問題而變得復雜,但往往這些問題又是難以定量或即使定量也難以計算的。

所以,在信號頻率不是很高的情況下,應以布通為第一原則。

09. 布局布線之后需要注意的問題

OK了?別急,用DRC檢查檢查先,這是一定要檢查的。

DRC對于布線完成覆蓋率以及規則違反的地方都會有所標注,按照這個再一一的排查,修正。

有些pcb還要加上敷銅(可能會導致成本增加),將出線部分做成淚滴(工廠也許會幫你加),最后的pcb文件轉成gerber文件就可交付pcb生產了。

有些直接給pcb也成,工廠會幫你轉gerber。

要裝配pcb準備bom表,一般能直接從原理圖中導出。

但是需要注意的是,原理圖中哪些部分元件該上,哪些部分元件不該上,要做到心理有數。

對于小批量或研究板而言,用excel自己管理倒也方便(大公司往往要專業軟件來管理)。

而對于新手而言,第一個版本,不建議直接交給裝配工廠或焊接工廠將bom的料全部焊上,這樣不便于排查問題。

最好的方法就是,根據bom表自己準備好元件,等到板來了之后,一步步上元件、調試。

現在談一下調試問題

拿到板第一步做什么,不要急急忙忙供電看功能,硬件調試不可能一步調試完成的。

先拿萬用表看看關鍵網絡是否有不正常,主要是看電源與地之間有否短路。

盡管生產廠商已經幫你做過測試,這一步還是要自己親自看看,有時候看起來某些步驟挺繁瑣,但是可以節約你后面不少時間!

其實短路與否不光pcb有關,在生產制作的任何一個環節可能導致這個問題,IO短路一般不會造成災難性的后果,但是電源短路就......

電源網絡沒短路?

那么好,那就看看電源輸出是否是自己理想的值,對于初學者,調試的時候最好IC一件件芯片上,第一個要上的就是電源芯片。

電源網絡短路了?

這個比較麻煩,不過要仔細看看自己原理圖是否有可能這樣的情況,同時結合割線的方法一步步排查到底是什么地方短路了。

是pcb的問題(一般比較爛的pcb廠就可能出現這種情況),還是裝配的問題,還是自己設計的問題。

電源芯片沒有輸出?

檢查檢查你的電源芯片輸入是否正常吧,還需要檢查的地方有使能信號、分壓電阻、反饋網絡等等。

電源芯片輸出值不在預料范圍?

如果超過很離譜,比如到了10%,那么看看分壓電阻先,這兩個分壓電阻一般要用1%的精度,這個你做到了沒有,同時看看反饋網絡吧,這也會影響你的輸出電源的范圍。

電源的輸出跳變是否正常?

電源輸出正常了,別高興,如果有條件的話,拿示波器看看吧,看看電源的輸出跳變是否正常,也就是抓取開電的瞬間,看看電源從無到有的情況。

現在談一下電源問題

無疑電源設計是整個電路板最重要的一環,電源不穩定,其他啥都別談。

在電源設計我們用得最多的場合是,從一個穩定的“高”電壓得到一個穩定的“低”電壓。

這也就是經常說的DC-DC(直流-直流),而直流-直流中用得最多的電源穩壓芯片有兩種,一種叫LDO(低壓差線性穩壓器,我們后面說的線性穩壓電源,也是指它),另一種叫PWM(脈寬調制開關電源,我們在本文也稱它開關電源)。

我們常常聽到PWM的效率高,但是LDO的響應快,這是為什么呢?別著急,先讓我們看看它們的原理。

下面會涉及一些理論知識,但是依然非常淺顯易懂,如果你不懂,嘿嘿,得檢查一下自己的基礎了。

01. 線性穩壓電源的工作原理:

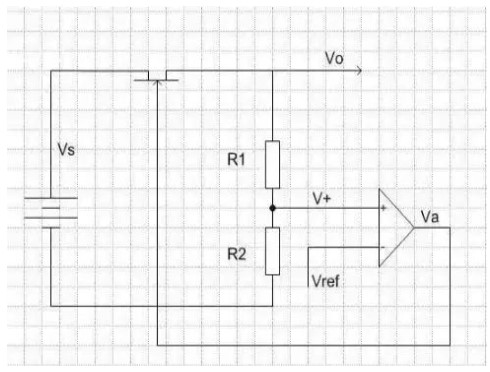

如上圖是線性穩壓電源內部結構的簡單示意圖,我們的目的是從高電壓Vs得到低電壓Vo。

在圖中Vo經過兩個分壓電阻分壓得到V+,V+被送入放大器(我們把這個放大器叫做誤差放大器)的正端,而放大器的負端Vref是電源內部的參考電平(這個參考電平是恒定的)。

放大器的輸出Va連接到MOSFET的柵極來控制MOSFET的阻抗。

Va變大時,MOSFET的阻抗變大;Va變小時,MOSFET的阻抗變小,MOSFET上的壓降將是Vs-Vo。

現在我們來看Vo是怎么穩定的,假設Vo變小,那么V+將變小,放大器的輸出Va也將變小,這將導致MOSFET的阻抗變小,這樣經過同樣的電流,MOSFET的壓差將變小,于是將Vo上抬來抑制Vo的變小。

同理,Vo變大,V+變大,Va變大,MOSFET的阻抗變大,經過同樣的電流,MOSFET的壓差變大,于是抑制Vo變大。

02. 開關電源的工作原理:

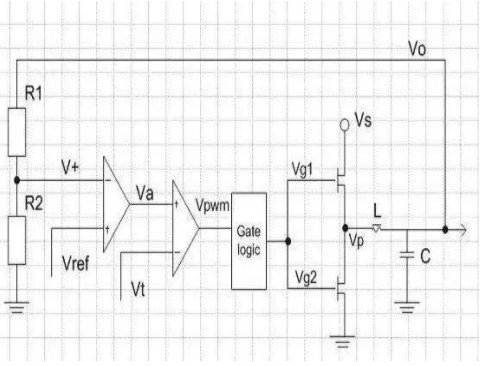

如上圖,為了從高電壓Vs得到Vo,開關電源采用了用一定占空比的方波Vg1、Vg2推動上下MOS管,Vg1和Vg2是反相的,Vg1為高,Vg2為低。

上MOS管打開時,下MOS管關閉;下MOS管打開時,上MOS管關閉。

由此在L左端形成了一定占空比的方波電壓,電感L和電容C我們可以看作是低通濾波器,因此方波電壓經過濾波后就得到了濾波后的穩定電壓Vo。

Vo經過R1、R2分壓后送入第一個放大器(誤差放大器)的負端V+,誤差放大器的輸出Va做為第二個放大器(PWM放大器)的正端,PWM放大器的輸出Vpwm是一個有一定占空比的方波,經過門邏輯電路處理得到兩個反相的方波Vg1、Vg2來控制MOSFET的開關。

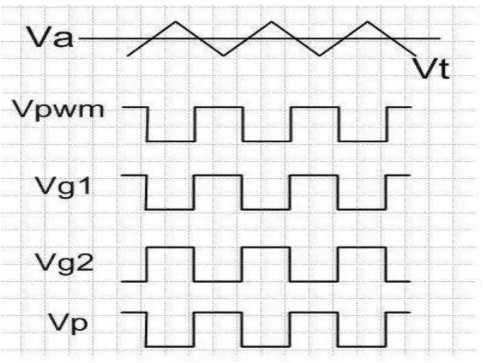

誤差放大器的正端Vref是一恒定的電壓,而PWM放大器的負端Vt是一個三角波信號,一旦Va比三角波大時,Vpwm為高;Va比三角波小時,Vpwm為低,因此Va與三角波的關系,決定了方波信號Vpwm的占空比;Va高,占空比就低,Va低,占空比就高。

經過處理,Vg1與Vpwm同相,Vg2與 Vpwm反相;最終L左端的方波電壓Vp與Vg1相同。如下圖:

當Vo上升時,V+將上升,Va下降,Vpwm占空比下降,經過門邏輯之后,Vg1的占空比下降,Vg2的占空比上升,Vp占空比下降,這又導致Vo降低,于是Vo的上升將被抑制。反之亦然。

線性穩壓電源和開關電源的比較

懂得了線性穩壓電源和開關電源的工作原理之后,我們就可以明白為什么線性穩壓電源有較小的噪聲,較快的瞬態響應,但是效率差。

而開關電源噪聲較大,瞬態響應較慢,但效率高了。

線性穩壓電源內部結構簡單,反饋環路短,因此噪聲小,而且瞬態響應快(當輸出電壓變化時,補償快)。

但是因為輸入和輸出的壓差全部落在了MOSFET上,所以它的效率低。

因此,線性穩壓一般用在小電流,對電壓精度要求高的應用上。

而開關電源,內部結構復雜,影響輸出電壓噪聲性能的因數很多,且其反饋環路長,因此其噪聲性能低于線性穩壓電源,且瞬態響應慢。

但是根據開關電源的結構,MOSFET處于完全開和完全關兩種狀態,除了驅動MOSFET,和MOSFET自己內阻消耗的能量之外,其他能量被全部用在了輸出。

理論上L、C是不耗能量的,盡管實際并非如此,但這些消耗的能量很小。

高速信號認識的一些誤區

高速看的是信號沿,不是時鐘頻率。

一般而言,時鐘頻率高的,其信號上升沿快,因此一般我們把它們當成高速信號。

但反過來不一定成立,時鐘頻率低的,如果信號上升沿依然快的,一樣要把它當成高速信號來處理。

根據信號理論,信號上升沿包含了高頻信息(用傅立葉變換,可以找出定量表達式)。

因此,一旦信號上升沿很陡,我們應該按高速信號來處理,設計不好很可能出現上升沿過于緩慢、有過沖、下沖、振鈴的現象。

比如,I2C信號,在超快速模式下,時鐘頻率為1MHz,但是其規范要求上升時間或下降時間不超過120ns。

因此,我們更應該關注的是信號帶寬。根據經驗公式,帶寬與上升時間(10%~90%)的關系為 Fw * Tr = 3.5。

示波器選擇

注意示波器的帶寬,很多人注意到了示波器的采樣率,沒有注意到示波器的帶寬,但往往示波器帶寬是一個更重要的參數。

一些人以為只要示波器采樣率滿足超過信號時鐘頻率的兩倍就行了,這是大錯特錯,錯誤的原因是錯誤的理解了采樣定理。

采樣定理說明了當采樣頻率大于信號最大帶寬的兩倍,就能完美地恢復原信號。

但是,采樣定理指的信號是帶限信號(帶寬是有限的),與現實中的信號嚴重不符。

我們一般的數字信號,除了時鐘之外都不是周期的,從長時間來看,其頻譜是無限寬的,要能捕獲到高速信號,就不能對其高頻分量太多的失真。

示波器帶寬指標與此息息相關,因此,真正要注意的依然是用示波器捕獲的信號的上升沿失真在我們可接受的范圍。

那么選多高帶寬的示波器才合適

理論上5倍于信號帶寬的示波器捕獲的信號比原信號損失不到3%。

如果要求損失更寬松,那就可以選擇更低端的示波器。

用到3倍于信號帶寬的示波器應該能滿足大多數要求,但是不要忘了你探頭的帶寬。

審核編輯:湯梓紅

-

電路

+關注

關注

172文章

5920瀏覽量

172285 -

硬件

+關注

關注

11文章

3337瀏覽量

66234 -

BOM

+關注

關注

5文章

256瀏覽量

40199

發布評論請先 登錄

相關推薦

硬件電路的設計思路

硬件電路設計的思路介紹

硬件電路設計的一般思路

電源升壓模塊電路安裝操作步驟

pytorch環境搭建詳細步驟

電路板檢修的方法及步驟

電路板測試步驟有哪些

電路板測試步驟有哪些 電路板測試儀器有哪些

M8_6pin母頭使用步驟有哪些

電路板 PCBA打樣包括哪些主要步驟?

硬件電路詳細設計步驟和思路

硬件電路詳細設計步驟和思路

評論