一、前言

無(wú)論是FPGA應(yīng)用開發(fā)還是數(shù)字IC設(shè)計(jì),時(shí)序約束和靜態(tài)時(shí)序分析(STA)都是十分重要的設(shè)計(jì)環(huán)節(jié)。在FPGA設(shè)計(jì)中,可以在綜合后和實(shí)現(xiàn)后進(jìn)行STA來(lái)查看設(shè)計(jì)是否能滿足時(shí)序上的要求。本文闡述基本的時(shí)序約束和STA操作流程。內(nèi)容主要來(lái)源于《Vivado從此開始》這本書,我只是知識(shí)的搬運(yùn)工。

二、時(shí)序約束與XDC腳本

時(shí)序約束的目的就是告訴工具當(dāng)前的時(shí)序狀態(tài),以讓工具盡量?jī)?yōu)化時(shí)序并給出詳細(xì)的分析報(bào)告。一般在行為仿真后、綜合前即創(chuàng)建基本的時(shí)序約束。Vivado使用SDC基礎(chǔ)上的XDC腳本以文本形式約束。以下討論如何進(jìn)行最基本時(shí)序約束相關(guān)腳本。

1 時(shí)序約束首要任務(wù)是創(chuàng)建主時(shí)鐘,主時(shí)鐘即為時(shí)鐘引腳進(jìn)入時(shí)鐘信號(hào)或高速收發(fā)器生成時(shí)鐘。[create_clock]

create_clock -name clk_name -period N-waveform {pos_time neg_time}[get_ports port_name](劃線部分可選)

創(chuàng)建兩個(gè)異步的主時(shí)鐘:

create_clock -name clk_a -period 10 [get_ports clk_a]

create_clock -name clk_b -period 15 [get_ports clk_b]

set_clock_groups -asynchronous -group clk_a -group clk_b

當(dāng)兩個(gè)主時(shí)鐘是異步關(guān)系,它們生成時(shí)鐘同樣是異步關(guān)系:

set_clock_groups -asynchronous -group [get_clocks clk_a -include_generated_clocks]

-group [get_clocks clk_b -include_generated_clocks]

差分時(shí)鐘僅約束P端口:

create_clock -name clk -period 10 [get_ports clk_p]

高速收發(fā)器生成時(shí)鐘作為主時(shí)鐘:

create_clock -name gt0_txclk -period 8 [get_pins GT0/.../TXOUTCLK]

有一種特殊情況無(wú)需與具體引腳綁定,即創(chuàng)建虛擬時(shí)鐘。該約束用于設(shè)定輸入/輸出延遲。需要?jiǎng)?chuàng)建虛擬時(shí)鐘的場(chǎng)景是輸入FPGA的數(shù)據(jù)由FPGA內(nèi)部產(chǎn)生時(shí)鐘采樣,如串口通信。

create_clock -name clk_v -period 5

2 創(chuàng)建主時(shí)鐘后,需要約束生成時(shí)鐘:[create_generated_clock]

生成時(shí)鐘分為兩種。由PLL MMCM等專用時(shí)鐘單元生成產(chǎn)生的時(shí)鐘信號(hào),Vivado會(huì)自動(dòng)產(chǎn)生相關(guān)約束。還有一種是自定義生成時(shí)鐘,一般為邏輯分頻得到。

時(shí)鐘源是時(shí)鐘端口:

create_generated_clock -name clk_div -source [get_ports clk] -divide_by 2 [get_pins rega/Q] 意思是在rega單元的Q引腳上的時(shí)鐘信號(hào)clk_div是由clk經(jīng)過(guò)2分頻得到的生成時(shí)鐘。

時(shí)鐘源是引腳:

create_generated_clock -name clk_div -source [get_pins rega/C] -divide_by 2 [get_pins rega/Q]

除了使用-divide_by -multiply_by表示主時(shí)鐘和生成時(shí)鐘的頻率關(guān)系,也可以用 -edges實(shí)現(xiàn)更精確的表達(dá):

create_generated_clock -name clk_div -source [get_pins rega/C] -edges {1 3 5} [get_pins rega/Q]

相移關(guān)系使用-edge_shift命令描述。

該約束命令還常用于重命名時(shí)鐘信號(hào):

create_generated_clock -name clk_rename [get_pins clk_gen/.../CLKOUT0]

3 創(chuàng)建時(shí)鐘組:[set_clock_groups]

a. 異步時(shí)鐘情況:

set_clock_groups -asynchronous -group clk_a -group clk_b clk_a和clk_b是異步時(shí)鐘。

b. 物理互斥情況:

create_clock -name clk_a -period 10 [get_ports clk]

create_clock -name clk_b -period 8 [get_ports clk] -add

create_clock -name clk_c -period 5 [get_ports clk] -add

set_clock_groups -physically_exclusive -group clk_a -group clk_b -group clk_c

該種情況僅是為了觀察clk引腳時(shí)鐘信號(hào)周期依次為10ns 8ns和5ns時(shí),時(shí)序是否收斂。因此這三個(gè)時(shí)鐘物理上不同時(shí)存在。

c. 邏輯互斥情況:

set_clock_groups -logically_exclusive

-group [get_clocks -of [get_pins clk_core/.../CLKOUT0]] -group [get_clocks -of [get_pins clk_core/.../CLKOUT1]]

clkout0和clkout1送入到BUFGMUX中,后續(xù)根據(jù)sel信號(hào)確定選擇哪一個(gè)作為工作時(shí)鐘。此時(shí)clkout0和clkout1同時(shí)存在電路中,但僅有一個(gè)會(huì)作為后續(xù)電路工作時(shí)鐘,因此邏輯上互斥。

特殊用法:當(dāng)asynchronous 的group只有一個(gè),說(shuō)明改組內(nèi)時(shí)鐘是同步的,但與其他所以時(shí)鐘異步。

4 設(shè)置偽路徑:[set_false_path]

設(shè)置偽路徑后,不再對(duì)特殊路徑進(jìn)行時(shí)序分析。特殊路徑如測(cè)試邏輯、添加同步電路后的跨時(shí)鐘域路徑等。在兩個(gè)時(shí)鐘域之間應(yīng)該相互設(shè)置為set_false:

set_false_path -from [get_clocks clk_a] -to [get_clocks clk_b]

set_false_path -from [get_clocks clk_b] -to [get_clocks clk_a]

5 常用時(shí)鐘相關(guān)命令:

report_clocks:查看創(chuàng)建的所有時(shí)鐘

report_property [get_clocks

report_clock_network:查看時(shí)鐘的生成關(guān)系網(wǎng)絡(luò)

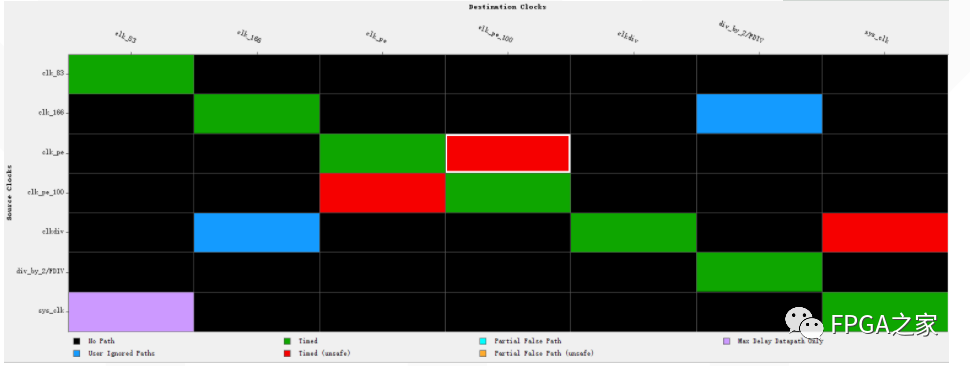

report_clock_interaction:查看時(shí)鐘交互關(guān)系

其中最后一項(xiàng)非常重要,經(jīng)常被用于查看異步時(shí)鐘域之間的路徑是否安全。若存在不安全路徑,需要添加同步、握手或FIFO后,設(shè)置為異步時(shí)鐘組或false_path。

鍵入該命令后,會(huì)生成時(shí)鐘交互矩陣。對(duì)角線是每個(gè)時(shí)鐘內(nèi)部路徑,其他非黑色部分即為存在對(duì)應(yīng)兩個(gè)時(shí)鐘的跨時(shí)鐘域路徑。紅色部分是非安全路徑,若不處理會(huì)產(chǎn)生亞穩(wěn)態(tài)。

三、查看時(shí)序報(bào)告(STA)

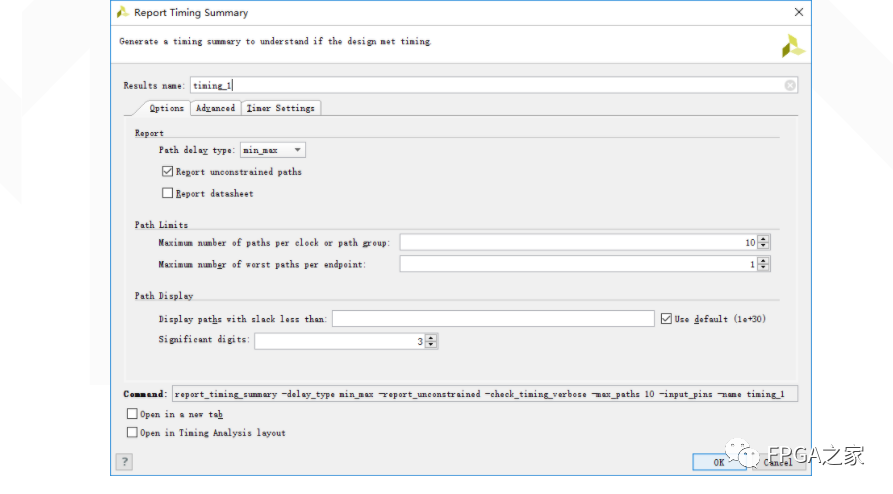

本節(jié)以一個(gè)有很多時(shí)序問題的工程為例進(jìn)行講解。在綜合后即可打開時(shí)序概要查看時(shí)序報(bào)告。

打開后有如下界面:

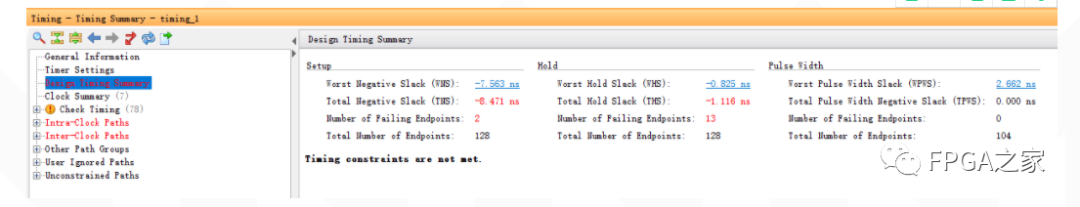

其中Design Timing Summary是時(shí)序概況,包括最大延遲分析、最小延遲分析以及脈沖寬度三個(gè)部分。其中WNS或WHS為負(fù)數(shù),說(shuō)明當(dāng)前設(shè)計(jì)無(wú)法滿足建立時(shí)間或保持時(shí)間要求,也就是說(shuō)數(shù)據(jù)無(wú)法被穩(wěn)定采樣。

Clock Summary內(nèi)的信息與使用report_clocks TCL腳本調(diào)出來(lái)的信息相似,包含了全部已創(chuàng)建的時(shí)鐘信號(hào)。Check Timing部分則包含了未被約束的部分,我們可以根據(jù)該部分信息進(jìn)一步添加必要的約束。Intra-Clock Paths和Inter-Clock Paths則分別描述了同步和異步電路時(shí)序路徑的裕量參數(shù)。

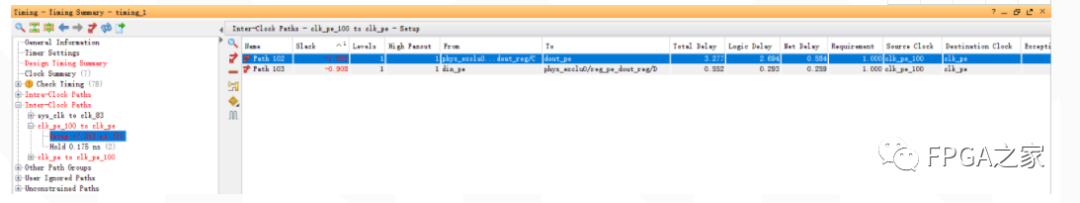

點(diǎn)擊WNS或WHS后的數(shù)值可以直接找到時(shí)序裕量最差的路徑:

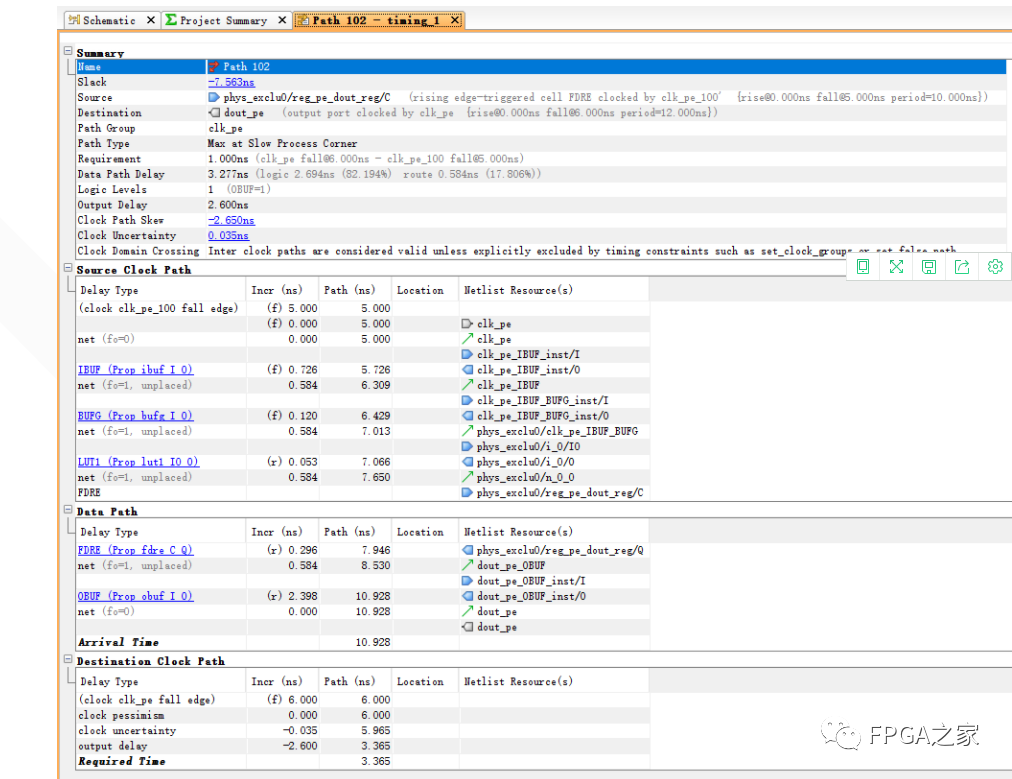

雙擊路徑信息所在行任意位置,界面會(huì)跳轉(zhuǎn)到該路徑的詳細(xì)信息界面:

四類時(shí)序路徑中,除了FPGA輸入端口到輸出端口這一特殊情況外,其他時(shí)序路徑均由源時(shí)鐘路徑、數(shù)據(jù)路徑和目的時(shí)鐘路徑三部分構(gòu)成。上表中各項(xiàng)的具體解釋見官方文檔UG908.

本文說(shuō)明了時(shí)序約束和STA的關(guān)系,基本時(shí)序約束情形及相應(yīng)的XDC腳本。之后簡(jiǎn)單介紹了如何在VIVADO中查看時(shí)序報(bào)告來(lái)分析時(shí)序問題。后續(xù)會(huì)以網(wǎng)絡(luò)通信中常見的RGMII接口設(shè)計(jì)實(shí)例闡述I/O延遲約束部分。

審核編輯 :李倩

-

時(shí)序

+關(guān)注

關(guān)注

5文章

392瀏覽量

37577 -

Vivado

+關(guān)注

關(guān)注

19文章

820瀏覽量

67511

原文標(biāo)題:VIVADO時(shí)序約束及STA基礎(chǔ)

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA主時(shí)鐘約束詳解 Vivado添加時(shí)序約束方法

一文詳解Vivado時(shí)序約束

時(shí)序約束與時(shí)序分析 ppt教程

Xilinx時(shí)序約束培訓(xùn)教材

Vivado中的靜態(tài)時(shí)序分析工具Timing Report的使用與規(guī)范

【時(shí)序約束資料包】培訓(xùn)課程Timing VIVADO

FPGA時(shí)序約束的建立和保持時(shí)間方法

Vivado進(jìn)行時(shí)序約束的兩種方式

基本的時(shí)序約束和STA操作流程

縮短Vivado編譯時(shí)間之審視時(shí)序約束描述

如何在Vivado中添加時(shí)序約束

評(píng)論