沒有任何寄存器邏輯,RTL設計是不完整的。RTL是寄存器傳輸級或邏輯,用于描述依賴于當前輸入和過去輸出的數字邏輯。

同步和異步復位

在ASIC/FPGA設計中,何時使用異步復位或同步復位總是導致設計者頭腦混亂。同步復位信號在時鐘邊緣和數據路徑的一部分進行采樣,而異步復位信號的采樣與時鐘信號無關,而與數據路徑或數據輸入邏輯的一部分無關。本節介紹使用異步和同步復位的Verilog RTL for 觸發器。

D觸發器異步復位

異步復位不是數據路徑的一部分,用于初始化觸發器,而不考慮時鐘邊沿,因此稱為異步復位。這種初始化觸發器的技術不推薦用于生成內部復位信號,因為它容易出現故障。設計者需要注意在內部同步該復位信號,以避免出現故障。內部同步復位信號應用于存儲元件。復位解除(reset deassertion)是異步復位信號的主要問題,采用兩級同步器可以克服這一問題。兩級同步器(Level synchronizer)避免了復位解除期間的繞線情況。

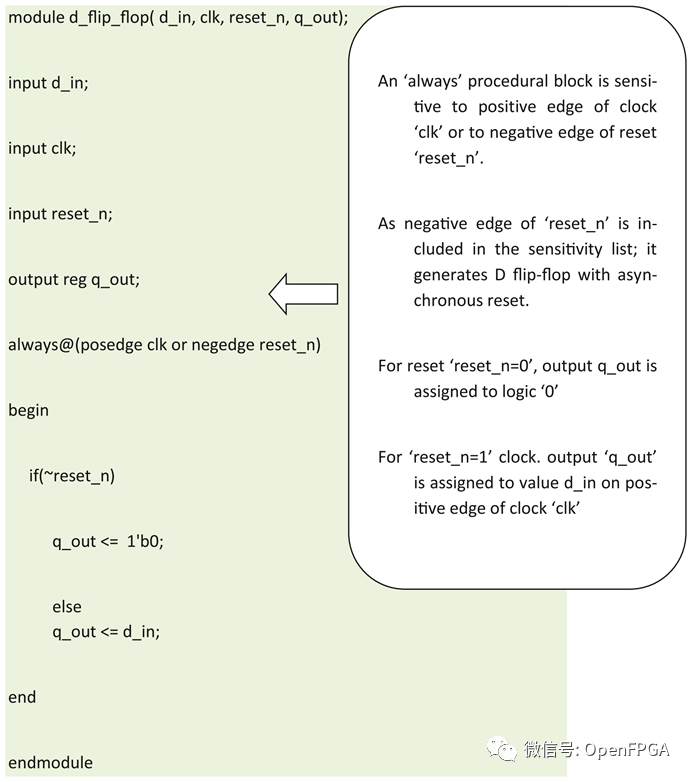

Verilog RTL如圖所示,使用低電平異步復位信號“reset_n”(示例5.3)。

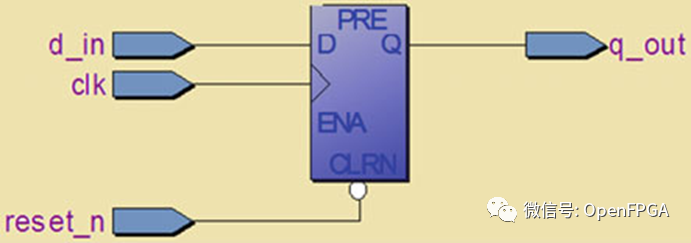

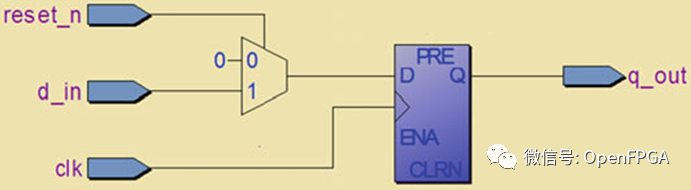

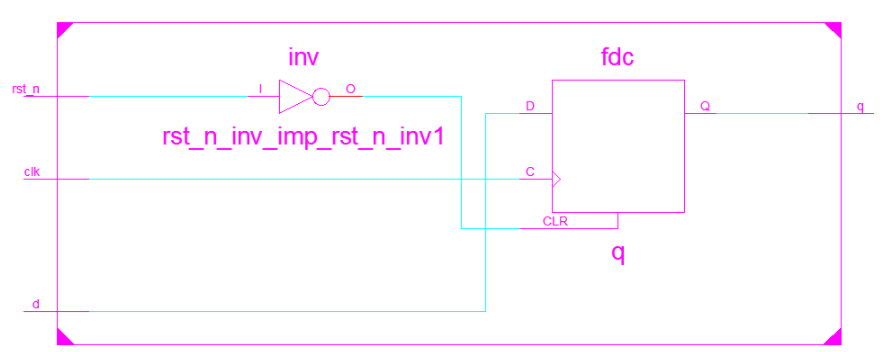

圖5.10顯示了具有異步復位“reset_n”的D觸發器的綜合邏輯。

示例5.3 D觸發器,帶低電平異步復位信號“reset_n”輸入

圖5.10 帶低電平異步復位信號輸入的綜合D觸發器

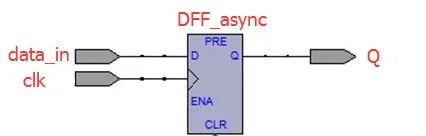

D觸發器同步復位

在同步復位中,復位信號是作為數據路徑的數據輸入的一部分,取決于活動時鐘邊沿。同步復位不存在故障或危險(glitches or hazards)問題,因此這種方法最適合設計。該機制不需要額外的同步電路。

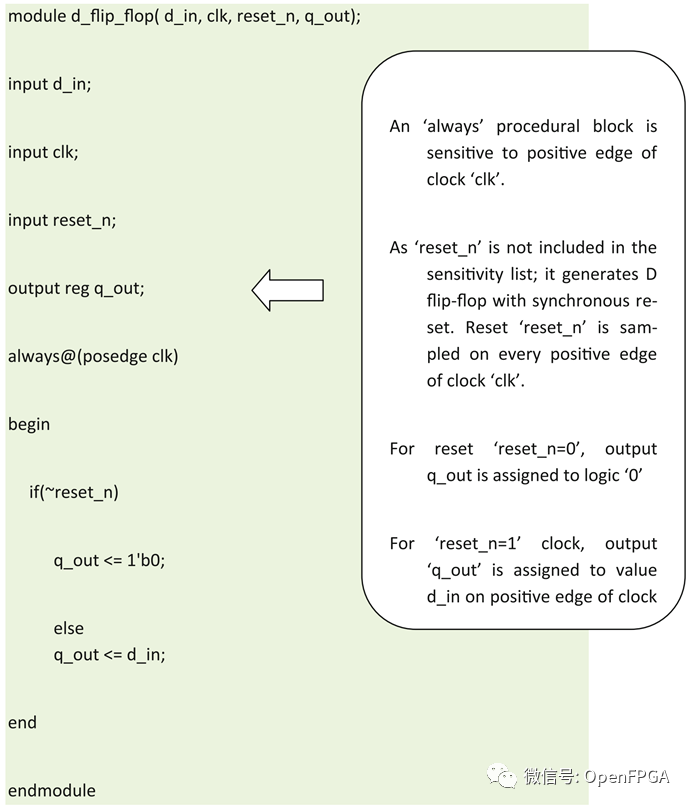

例5.4中描述了Verilog RTL,它使用低電平同步復位信號“reset_n”。

示例5.4 D觸發器,帶有源低同步復位輸入

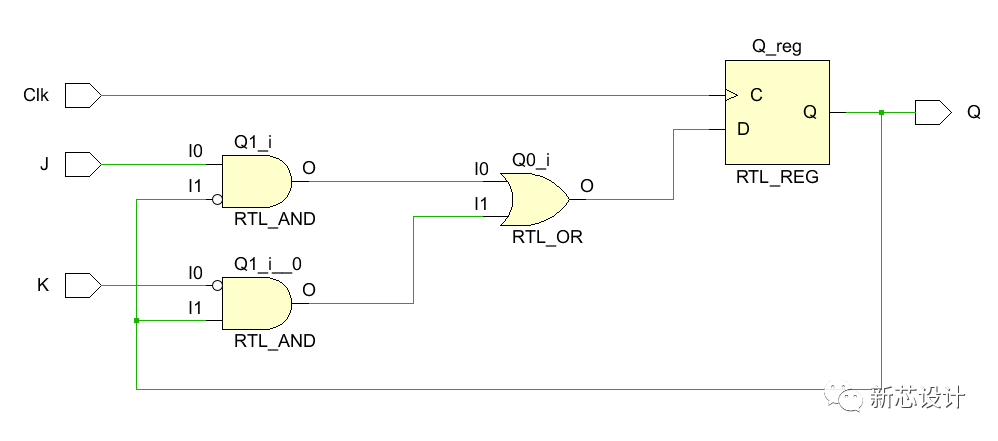

圖5.11同步復位D觸發器的綜合邏輯

帶同步復位輸入的正邊沿觸發D觸發器的綜合邏輯如圖5.11所示。

帶使能異步復位的觸發器

在大多數實際應用中,需要多個異步輸入。考慮一個應用程序,當激活輸入時,它需要加載輸入數據。即使在復位信號激活且有效時,也必須等待初始化寄存器。如果兩個異步輸入同時到達,則輸出應取決于這些信號的優先級分配。

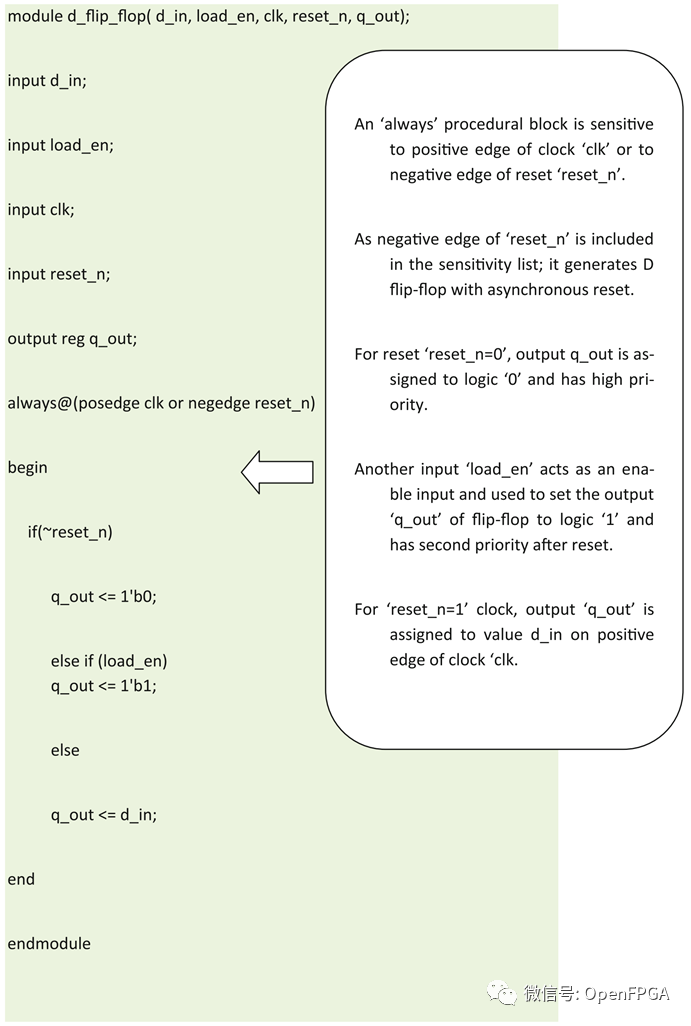

如示例5.5所示,兩個異步輸入被命名為“reset_n”和“load_en”。“ reset_n”具有最高優先級,“load_en”具有最低優先級。使用“if-else”構造優先級。

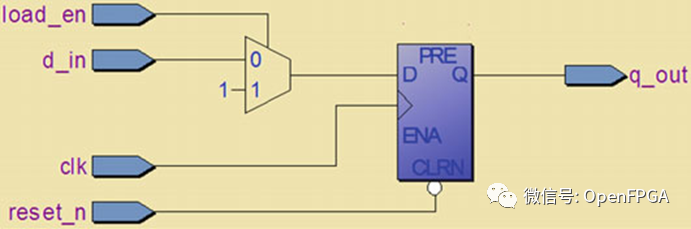

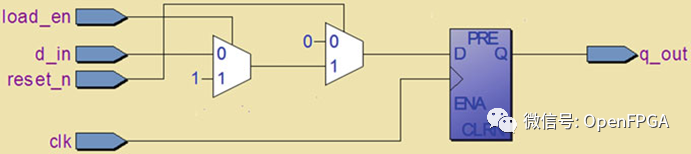

綜合邏輯如圖5.12所示。

示例5.5帶異步“reset_n”和“load_en”的D觸發器的Verilog RTL

圖5.12異步復位D觸發器的綜合輸出

帶使能同步復位的觸發器

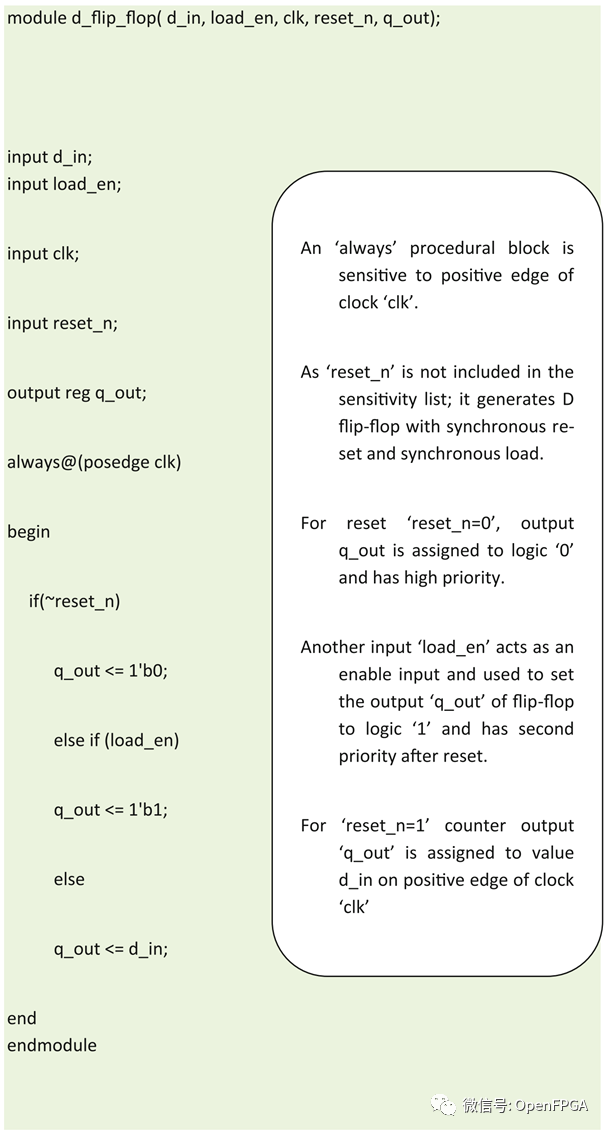

如果多個信號或輸入是數據路徑的一部分,并且在時鐘的活動邊沿上采樣,則在時鐘的活動邊緣上分配時序單元的輸出。考慮示例5.6中所示的Verilog RTL,輸入“reset_n”和“load_en”是同步輸入并在時鐘的正邊上采樣。同步輸入“reset_n”具有最高優先級,“load_en”具有最低優先級。

綜合邏輯如圖5.13所示,“reset_n”和“load_en”是數據路徑的一部分。

示例5.6帶同步“reset_n”和“load_en”的D觸發器

圖5.13帶同步“reset_n”和“load_en”的綜合邏輯

審核編輯:郭婷

-

FPGA

+關注

關注

1630文章

21769瀏覽量

604639 -

asic

+關注

關注

34文章

1205瀏覽量

120600 -

觸發器

+關注

關注

14文章

2000瀏覽量

61255

原文標題:Verilog時序邏輯硬件建模設計(二)同步和異步復位

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

verilog描述異步置0,異步置1功能的D觸發器

同步復位和異步復位的比較(轉載)

FPGA的復位設計分析(Verilog HDL與RTL圖)

D觸發器中PRN與CLRN區別在哪

異步復位信號亞穩態的原因與D觸發器的Verilog描述

Verilog RTL和觸發器中的同步和異步復位功能分析

Verilog RTL和觸發器中的同步和異步復位功能分析

評論