導讀

CPU(中央處理器),也被稱為微處理器,是計算機的心臟和/或大腦。本文讓我們一起深入了解計算機的核心,以幫助我們高效地編寫計算機程序。

以下為譯文:

“工具通常比機器簡單,通常用手來使用,而機器通常由動物或蒸汽動力驅動。”

——查爾斯·巴貝奇

計算機是一種機器,主要由電力驅動,但其靈活性和可編程性幫助實現了其作為一種工具的簡單性。CPU是計算機的心臟和/或大腦。負責執行提供給它們的指令。它的主要任務是執行算術和邏輯運算,并將指令協調在一起。在深入到本文的主要部分之前,讓我們先看看CPU的主要組成部分,以及它們的作用分別是什么。

1、CPU的兩個主要組成部分

控制單元?—?CU控制單元(CU)是CPU的一部分,它幫助協調指令的執行。它告訴CPU應該做什么。它的主要職責是根據指令,幫助激活連接CPU和計算機其他不同部件(包括ALU)的線路。控制單元是CPU的第一個接收處理指令的部件。

控制單元有兩種類型:

硬接線控制單元。

微型可編程(微編程)控制單元。

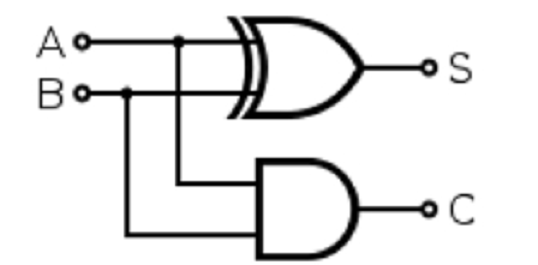

硬接線控制單元是一種硬件,它需要在硬件上進行更改以實現對其工作方式的修改,而微型可編程控制單元則可以進行編程以更改其工作方式。硬接線控制單元在處理指令方面更快,而微型可編程控制單元則更靈活。算術邏輯單元 —? ALU算術邏輯單元(ALU),顧名思義,就是負責所有的算術和邏輯運算。算術邏輯單元執行加法運算,減法運算等操作。算術邏輯單元是由執行這些操作的邏輯電路或邏輯門組成。大多數邏輯門接受兩個輸入并產生一個輸出。下面是一個半加法器電路的例子,它接受兩個輸入并輸出結果。這里A和B是輸入,S是輸出,C是進位。

半加法器電路圖

2、存儲 - 寄存器和存儲器

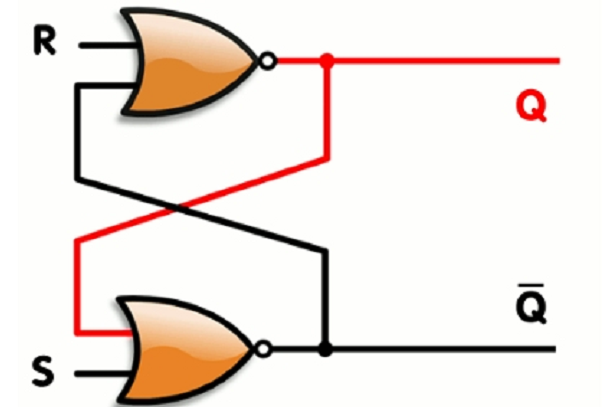

CPU的主要任務是執行提供給它的指令。在大多數情況下,為了處理這些指令,它需要數據。有些數據是中間數據,有些是輸入,另一些是輸出。這些數據連同指令一起存儲在下列存儲器中:寄存器寄存器是一組可以存儲數據的小地方。寄存器是鎖存器(Latches)的組合。鎖存器也稱為觸發器(flip-flops),是存儲1位信息的邏輯門的組合。鎖存器有一條輸入線,一條寫入和輸入線,和一條輸出線。我們可以啟用寫入線對存儲的數據進行更改。當寫入線被禁用時,輸出始終保持不變。

SR鎖存器,由一對交叉耦合的或非門(NOR Gates)構成。CPU由寄存器來存儲輸出數據。由于是中間數據,它們被發送到主存儲器(RAM)的速度會慢。這些數據被發送到由總線連接的其它寄存器。寄存器可以存儲指令、輸出數據、存儲地址或任何類型的數據。存儲器(RAM)RAM - 隨機存取存儲器是寄存器的集合,它們以優化的方式排列和壓縮在一起,以便存儲更多的數據。隨機存取存儲器(RAM)是易失性的,當我們關閉電源時,它存儲的數據會丟失。由于RAM是用于讀/寫數據的寄存器的集合,因此RAM可以用于存儲8位地址的輸入、用于存儲實際數據的數據輸入,和用于儲存最后的和鎖存器一樣工作的讀寫啟用碼。

3、什么是指令

指令是計算機可以執行的最小粒度運算。CPU可以處理各種類型的指令

指令類型包括:

算術運算指令,如加法和減法運算

邏輯運算指令,如邏輯與(AND)、邏輯或(OR)和邏輯非(NOT)運算

數據傳送指令,如數據移動、輸入、輸出、加載和存儲

程序控制指令,如條件/無條件轉移指令(if…goto,goto),轉子指令和轉移指令(call,return)

通知CPU程序已結束的Halt指令

指令通過以下方式提供給計算機:使用匯編語言直接提供,或由編譯器生成,或用某些高級語言解釋給出。這些指令在CPU內部是硬連線的。算術和邏輯運算指令包括在ALU(算術邏輯單元)中,而程序控制指令由CU(控制單元)管理。通常在一個時鐘周期(clock cycle)內,計算機可以執行一個指令,但是現代的計算機可以同時執行多個指令。計算機可以執行的一組指令稱為指令集。

4、CPU時鐘

時鐘周期計算機的速度由其時鐘周期(Clock cycle)衡量。它是指計算機每秒工作的時鐘周期數。單個時鐘周期非常小,大約250*10^(-12)秒。每秒時鐘周期數越高,處理器速度越快。CPU時鐘頻率(clock rate)的測量單位為GHz(千兆赫茲)。1Ghz等于10 ?Hz(赫茲)。一赫茲意味著一秒鐘。所以一千兆赫茲意味著每秒10 ?個時鐘周期。時鐘周期越小,CPU可以執行的指令數量越多。時鐘周期等于時鐘頻率的倒數,而CPU時間=時鐘周期數/時鐘頻率這意味著為了改進(減少)CPU時間,我們可以通過提高時鐘頻率,或優化我們提供給CPU的指令來減少指令需要的時鐘周期的數量。一些處理器提供了提高時鐘頻率的能力,但由于這是一個物理變化,可能會出現過熱,甚至冒煙/起火。

5、指令是如何執行的

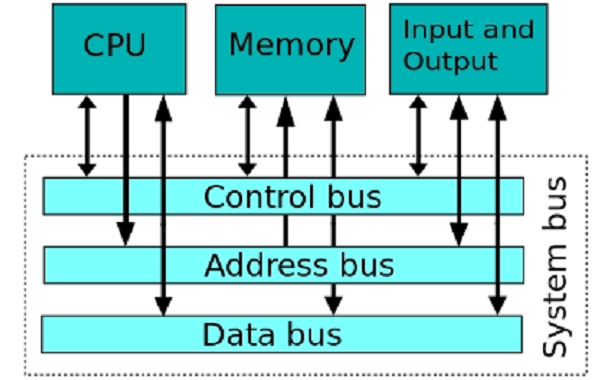

指令按順序存儲在隨機存取存儲器(RAM)上。對于一個假設的CPU指令,它由操作碼(OP code)和存儲器或寄存器地址組成。控制單元(CU)內有兩個寄存器:用于加載指令操作碼的指令寄存器(IR),和用于加載當前正在執行的指令地址的指令地址寄存器。CPU中還有其他寄存器,用于存儲一個指令的最后4位的地址中存儲的值。讓我們以一組實現兩個數字相加操作的指令為例。下面是這些指令及其說明:第一步 - LOAD_A 8該指令最初保存在RAM中,比如說指令<1100 1000>。它的前4位是操作碼。這決定了這個指令要做什么。然后該指令被讀取到控制單元的指令寄存器(IR)中。指令被譯碼為load_A,這意味著它需要加載地址1000中的數據,地址1000是存儲在寄存器A中的指令的后4位。第二步 - LOAD_B 2與上面類似,它將內存地址2(0010)中的數據加載到CPU的寄存器B中。第三步 – ADD B A接下來的這條指令是把這兩個數字相加。在這里,控制單元(CU)告訴算術邏輯單元(ALU)執行加法操作并將結果保存回寄存器A中。第4步 – STORE_A 23將結果保存回寄存器A中。這是一組非常簡單的指令,實現了兩個數字的相加操作。現在,我們成功地得到了兩個數字相加的和值!總線CPU,寄存器,存儲器和IO設備之間的所有數據都通過總線傳輸。要將剛才兩數相加得到的和數保存到存儲器中,CPU將存儲器地址放入地址總線,將得到的結果(和數)放入數據總線,然后在控制總線中啟用正確的信號。這樣,數據在總線的幫助下被保存到存儲器中。

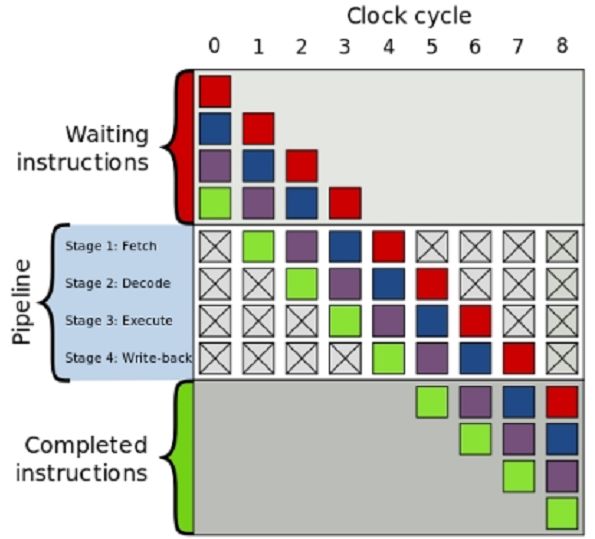

計算機系統總線緩存CPU還具有將指令預取到其緩存中的機制。我們知道,一個處理器可以在一秒鐘內完成數百萬條指令。這意味著從存儲器(RAM)中獲取指令所花費的時間比執行指令所花費的時間要多。所以CPU會預取一些指令和數據到其緩存中,以加快執行速度。如果緩存中的數據和操作內存中的數據不同,則將數據標記為臟位(dirty bit)。指令流水線現代CPU在指令執行中采用指令流水線技術實現取指(FI)、譯碼(DI)、執行(EI)的并行化。當一條指令完成“取指”后進入“譯碼”的同時,下一條指令就可以進行“取指”了,這樣就提高了指令的執行效率。

指令流水線技術然而,當一條指令和另一條指令有依賴關系時,這種技術會產生問題。所以,指令流水線技術只能夠讓處理器以不同的順序執行相互之間沒有依賴關系的指令。多核計算機它基本上是有不同的CPU,但是有一些共享資源,比如緩存等。

6、性能

CPU的性能取決于它的執行時間。性能=1/執行時間假設一個程序執行需要20毫秒。CPU性能為1/20=0.05ms。相對性能=執行時間1/執行時間2影響CPU性能的因素是指令執行時間和CPU的時鐘速度(時鐘頻率)。因此,為了提高程序的性能,我們要么提高CPU的時鐘速度(時鐘頻率),要么減少程序中的指令數量。處理器的速度有限,現代多核計算機每秒可以支持數百萬條指令。但是,如果我們編寫的程序有太多的指令,就將導致整體性能的降低。大O符號(Big O notation)計算方法可以用來確定在給定輸入的情況下CPU的性能將如何受到影響。為了盡可能地提高CPU的速度,很多優化工作已經在CPU中進行。而我們在編寫任何程序時,都需要考慮如何盡可能地減少我們提供給CPU的指令數量,以提高計算機程序的性能。

原文標題:CPU 是如何工作的?

文章出處:【微信公眾號:Imagination Tech】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19347瀏覽量

230244 -

cpu

+關注

關注

68文章

10879瀏覽量

212184 -

計算機

+關注

關注

19文章

7519瀏覽量

88202

原文標題:CPU 是如何工作的?

文章出處:【微信號:Imgtec,微信公眾號:Imagination Tech】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CPU(中央處理器)的組成部分及工作原理

CPU(中央處理器)的組成部分及工作原理

評論