關于SiC功率元器件中柵極-源極間電壓產生的浪涌,在之前發布的TechWeb基礎知識SiC功率元器件應用篇的“SiCMOSFET:橋式結構中柵極-源極間電壓的動作”中已進行了詳細說明,如果需要了解,請參閱這篇文章。

關于浪涌抑制電路的電路板布局注意事項

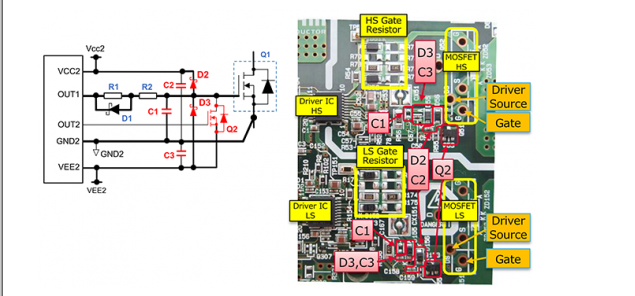

浪涌抑制電路的元器件布局和焊盤布局會直接影響浪涌抑制效果,因此為了獲得理想的效果,在此介紹幾點需要著重注意的問題。首先,請看浪涌抑制電路和電路板布局的示例。該電路圖是此前用過的電路圖的一部分。電路板上配置了HS和LS兩個電路。

在這塊電路板上,橋式結構的HSMOSFET配置在上方,LSMOSFET配置在下方,柵極引腳和驅動器源極引腳被配置在各MOSFET的下方。VGS浪涌電壓抑制電路緊靠各柵極引腳配置,是以最短距離連接的。這種精心的布局旨在更大程度地降低寄生電容、電感和電阻。

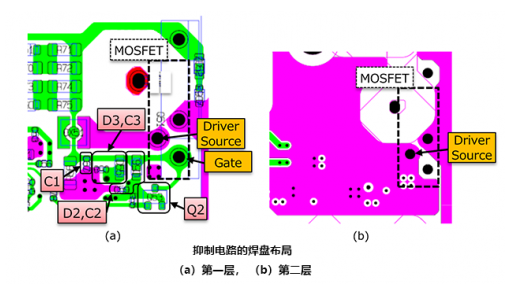

接下來,請看浪涌抑制電路的焊盤圖案布局。

如果具有多個浪涌抑制電路,那么應當優先確定米勒鉗位用MOSFET(Q2)的安裝位置。其次時配置負浪涌鉗位SBD(D2)及其旁路電容(C2),并按正浪涌鉗位SBD(D3)、旁路電容(C3)和誤導通抑制電容(C1)的順序決定配置位置。這樣做的原因是由于布線電感的影響,會導致浪涌抑制效果大大降低,尤其是當米勒鉗位MOSFET距離只有幾厘米時。

另外,非常重要的一點是,要盡量縮短由浪涌抑制電路的回流線(從驅動器源極引腳返回的線)和浪涌抑制電路的布線所形成的環路。由于SiCMOSFET的高速開關,ID中的di/dt會引起較大的EMI,所以其布線環路應盡量避免受ID產生的EMI的影響。這次評估的電路板是4層結構,第2層全為回流線。因此,可以將回流線直接置于浪涌抑制電路正下方,從而可以更大程度地縮小環路面積。

如果來自驅動電源的阻抗足夠小,那么就不需要與鉗位SBD并設的旁路電容器,但是由于驅動電源通常距離較遠,所以需要在SBD附近安裝一個旁路電容器,以便SBD能夠以低阻抗工作。此外,在選擇電容器時,請充分考慮阻抗特性并選擇在幾十MHz頻段上具有諧振點的電容器(0.1μF,1.0×0.5mm尺寸)。

-

電路板

+關注

關注

140文章

4960瀏覽量

97831 -

浪涌

+關注

關注

3文章

255瀏覽量

28520 -

電路板布局

+關注

關注

0文章

4瀏覽量

1317

發布評論請先 登錄

相關推薦

極好的模擬/數字混合信號的電路板布局布線注意事項資料下載

布局浪涌抑制電路板的注意事項

布局浪涌抑制電路板的注意事項

評論