1 Xilinx FFT IP介紹

Xilinx快速傅立葉變換(FFT IP)內核實現了Cooley-Tukey FFT算法,這是一種計算有效的方法,用于計算離散傅立葉變換(DFT)。

1)正向和反向復數FFT,運行時間可配置。

2)變換大小N = 2m,m = 3–16

3)數據采樣精度bx = 8–34

4)相位系數精度bw = 8–34

5)算術類型:

°無標度(全精度)定點

°定標定點

°浮點數

6)定點或浮點接口

7)蝴蝶后舍入或截斷

8)Block RAM或分布式RAM,用于數據和相位因子存儲

9)可選的運行時可配置轉換點大小

10)可擴展的定點核心的運行時可配置擴展時間表

11)位/數字反轉或自然輸出順序

12)用于數字通信系統的可選循環前綴插入

13)四種架構在內核大小和轉換時間之間進行權衡

14)位精確的C模型和用于系統建模的MEX功能可供下載

15)有四種運算架構可供選擇

.Pipelined Streaming I/O

.Radix-4 Burst I/O

.Radix-2 Burst I/O

.Radix-2 Lite Burst I/O

2 FFT IP接口介紹

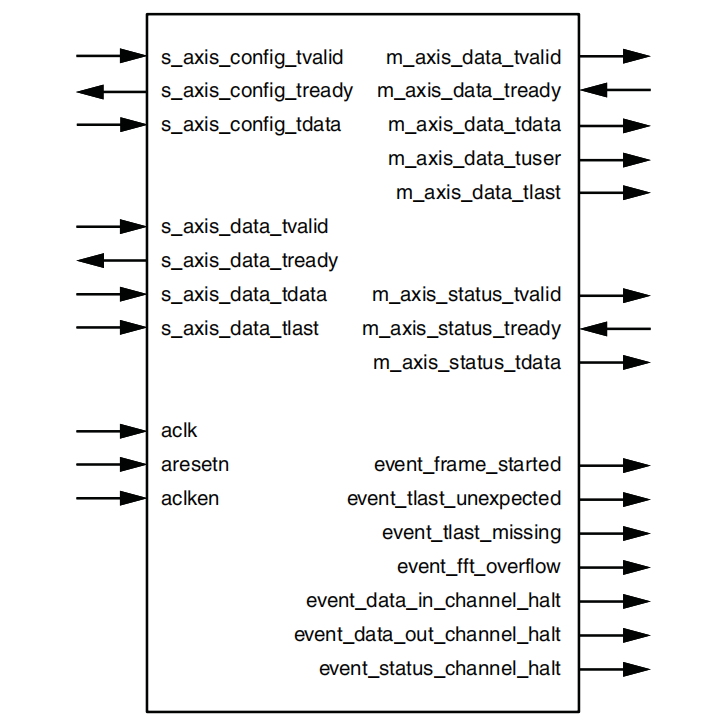

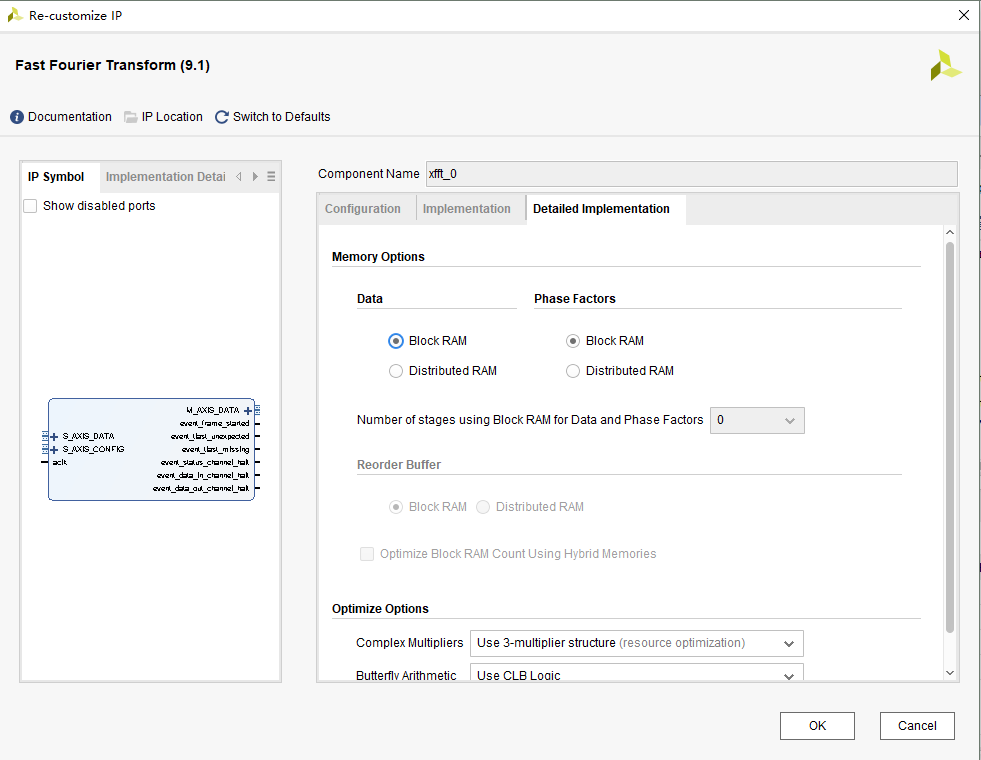

圖1 xilinx FFT IP

1)AXI4-Stream介紹

AXI4-Stream接口帶來了標準化,并增強了Xilinx IP LogiCORE解決方案的互操作性。除了諸如aclk,acclken和aresetn之類的常規控制信號以及事件信號之外,到內核的所有輸入和輸出都通過AXI4-Stream通道進行傳輸。通道始終由TVALID和TDATA以及必填字段和可選字段(如TREADY,TUSER和TLAST)組成。TVALID和TREADY一起執行握手以傳輸消息,其中有效負載為TDATA,TUSER和TLAST。內核對包含在TDATA字段中的操作數進行運算,并將結果輸出到輸出通道的TDATA字段中。

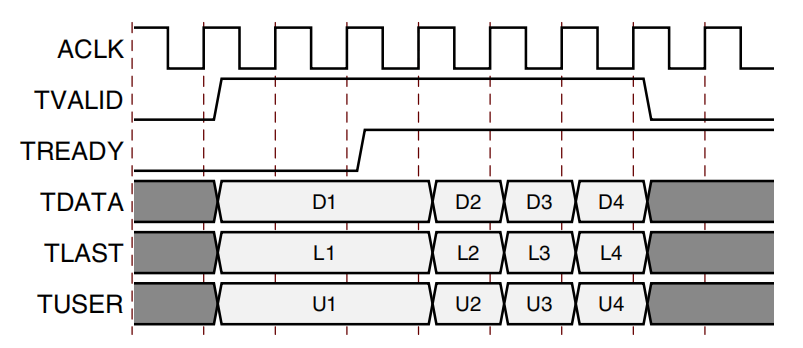

圖2 AXI4-Stream時序圖

圖2顯示了在AXI4-Stream通道中的數據傳輸。TVALID由通道的源(主)端驅動,而TREADY由接收器(從屬)驅動。TVALID指示有效負載字段(TDATA,TUSER和TLAST)中的值有效。TREADY表示從機已準備好接收數據。當一個周期中的TVALID和TREADY均為TRUE時,將發生傳輸。主機和從機分別為下一次傳輸分別設置TVALID和TREADY。

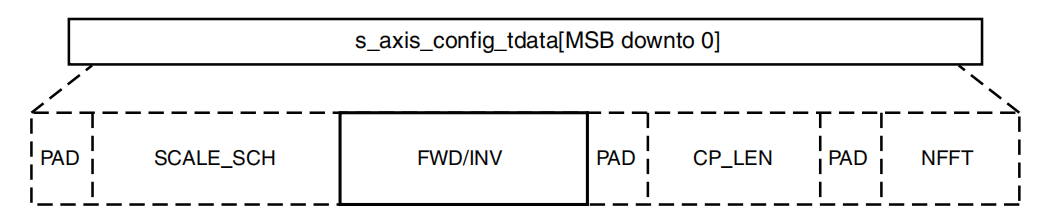

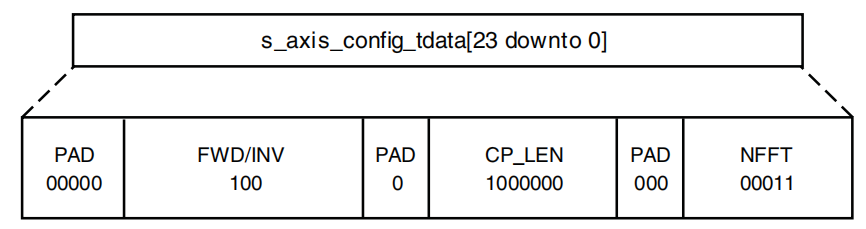

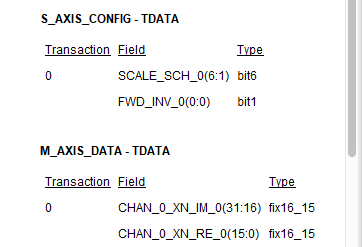

2)s_axis_config_tdata接口介紹

s_axis_config_tdata接口攜帶配置信息CP_LEN,FWD / INV,NFFT和SCALE_SCH。

NFFT(變換的點大小):NFFT可以是最大變換的大小或任何較小的點大小。例如,1024點FFT可以計算點大小1024、512、256等。NFFT的值為log2(點大小)。該字段僅在運行時可配置的轉換點大小時出現。

CP_LEN(循環前綴長度):從轉換結束起,在輸出整個轉換之前,最初作為循環前綴輸出的樣本數。CP_LEN可以是小于點大小的從零到一的任何數字。該字段僅在循環前綴插入時出現。

FWD_INV:指示是執行前向FFT變換還是逆向FFT變換(IFFT)。當FWD_INV = 1時,將計算前向變換。如果FWD_INV = 0,則計算逆變換。

SCALE_SCH伸縮時間表:對于突發I / O架構,伸縮時間表由每個階段的兩位指定,第一階段的伸縮由兩個LSB給出。縮放比例可以指定為3、2、1或0,代表要移位的位數。N = 1024,Radix-4 Burst I / O的示例縮放計劃是[1 0 2 3 2](從最后階段到第一階段排序)。對于N = 128,Radix-2 Burst I / O或Radix-2 Lite Burst I / O,一個可能的擴展時間表是[1 1 1 1 0 1 2](從最后階段到第一階段排序)。對于流水線I / O架構,從兩個LSB開始,每兩對Radix-2級用兩位指定擴展時間表。例如,N = 256的縮放時間表可以是[2 2 2 3]。當N不是4的冪時,最后一級的最大位增長為一位。例如,對于N = 512,[0 2 2 2 2]或[1 2 2 2 2]是有效的縮放時間表,但是[2 2 2 2 2]無效。對于此變換長度,SCALE_SCH的兩個MSB只能為00或01。此字段僅可用于縮放算法(非縮放,塊浮點或單精度浮點)。

s_axis_config_tdata接口格式:

1.(可選)NFFT加填充

2.(可選)CP_LEN加填充

3.前轉/后轉

4.(可選)SCALE_SCH

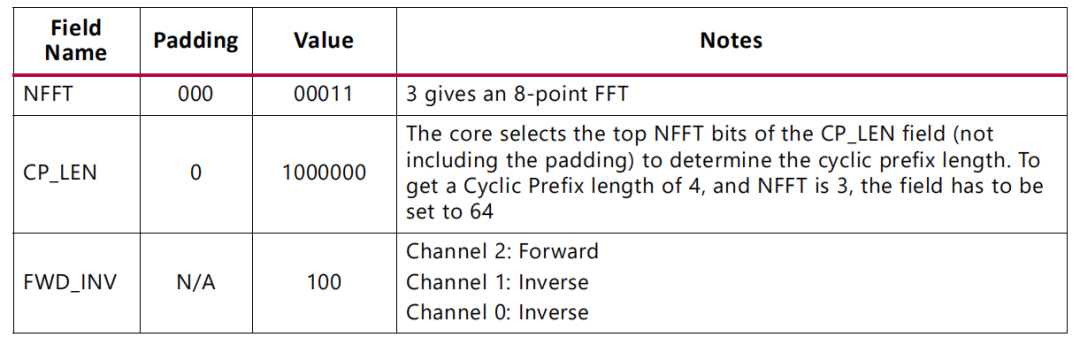

舉例:

內核具有可配置的轉換大小,最大大小為128點,具有循環前綴插入和3個FFT通道。內核需要配置為執行8點變換,并在通道0和1上執行逆變換,并在通道2上執行前向變換。需要4點循環前綴。這些字段采用表中的值。

這給出了19位的向量長度。由于所有AXI通道必須與字節邊界對齊,因此需要5個填充位,從而s_axis_config_tdata的長度為24位。

3)相關標志信號

3 xilinx FFT IP的仿真測試

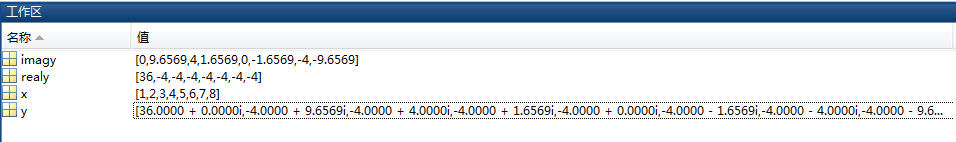

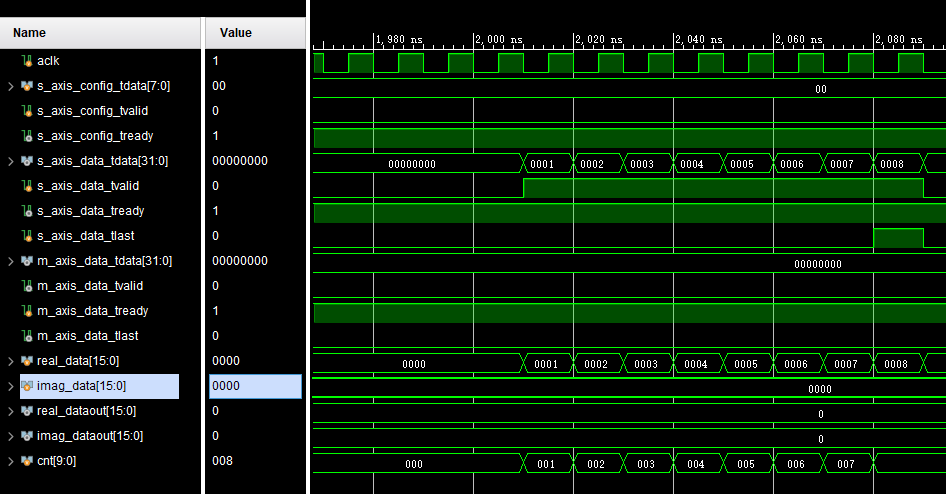

FFT的長度選擇8點,x輸入序列為x=[1,2,3,4,5,6,7,8];

Matlab驗證:

clear allclose allclcx = [1,2,3,4,5,6,7,8];y =fft(x,8);realy=real(y);imagy=imag(y);

Y的實部輸出為realy=[36,-4,-4,-4,-4,-4,-4,-4];

Y的虛部輸出為imagy=[0,9.6569,4,1.6569,0,-1.6569,-4,-9.6569];

FPGA仿真驗證:

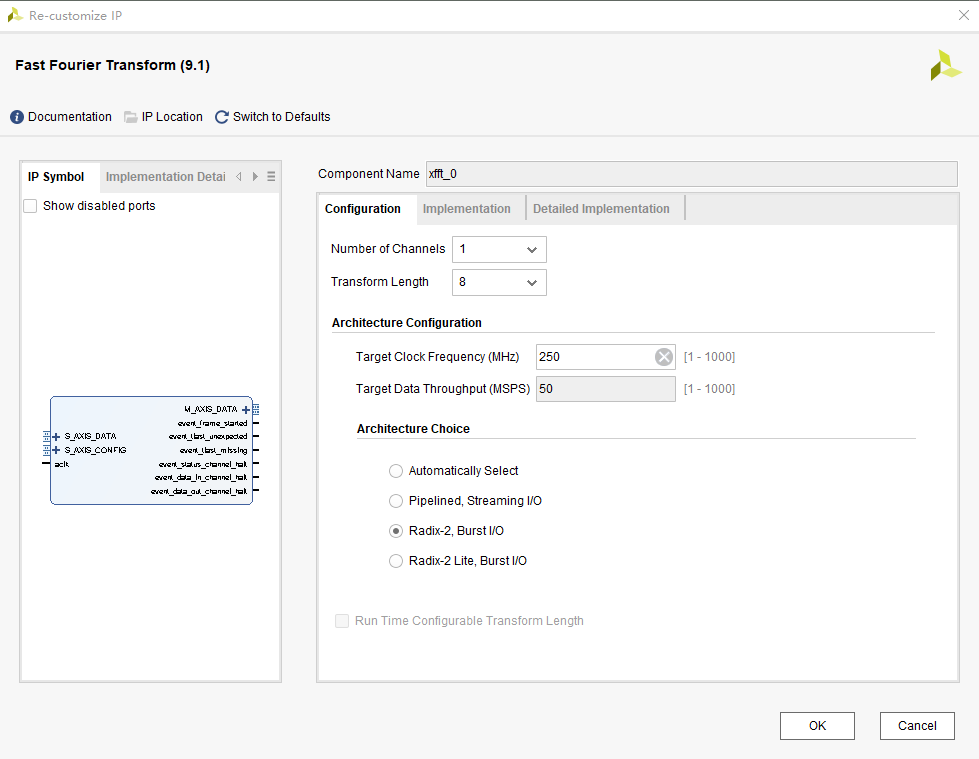

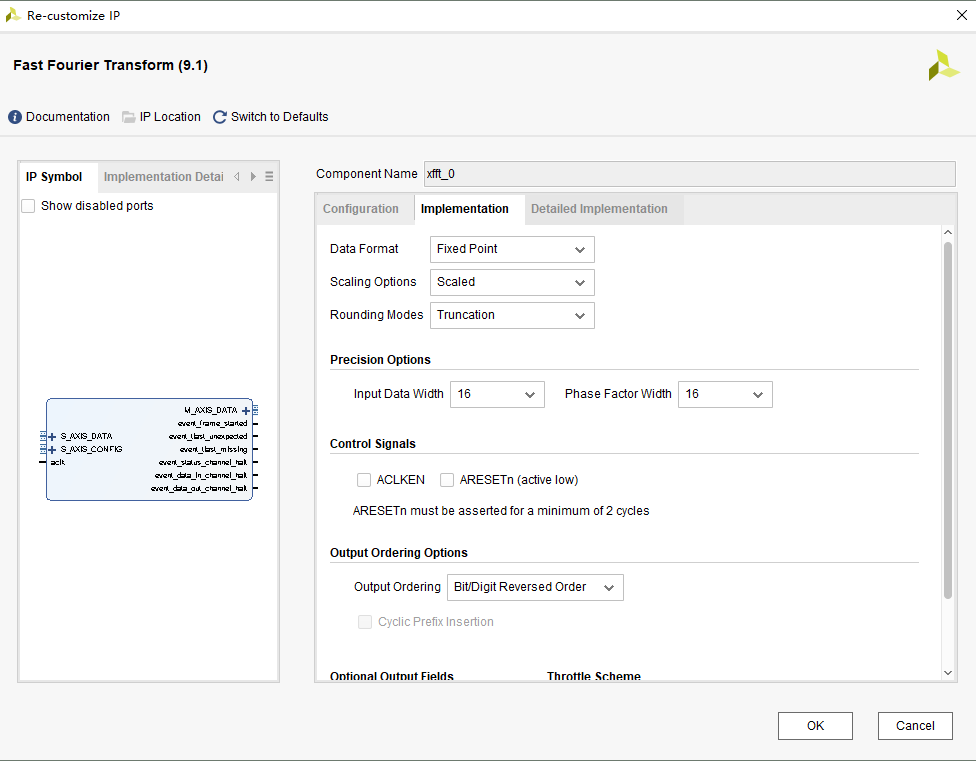

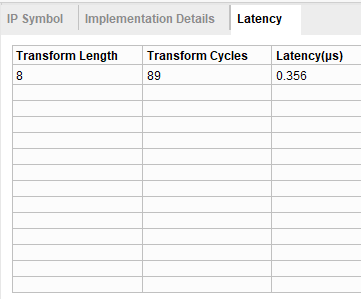

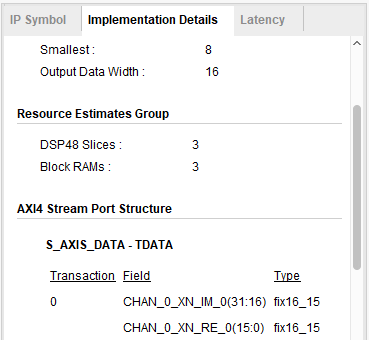

1)IP的設置

2)仿真頂層

1ns / 1psmodule tb_fft_top();reg aclk;reg [7 : 0] s_axis_config_tdata;reg s_axis_config_tvalid;wire s_axis_config_tready;wire [31 : 0] s_axis_data_tdata;reg s_axis_data_tvalid;wire s_axis_data_tready;reg s_axis_data_tlast;wire [31 : 0] m_axis_data_tdata;wire m_axis_data_tvalid;reg m_axis_data_tready;wire m_axis_data_tlast;reg [15:0] real_data;reg [15:0] imag_data;wire [15:0] real_dataout;wire [15:0] imag_dataout;reg [9:0] cnt;assign s_axis_data_tdata={real_data,imag_data};assign real_dataout = m_axis_data_tdata[31:16];assign imag_dataout = m_axis_data_tdata[15:0];initial beginaclk = 0;s_axis_config_tdata=8'b0;s_axis_config_tvalid=1'b0;s_axis_data_tvalid=1'b0;s_axis_data_tlast=1'b0;real_data=16'd0;imag_data=16'd0;cnt = 0;m_axis_data_tready=1'b1;#1000;s_axis_config_tdata=8'b0000_0001;s_axis_config_tvalid=1'b1;#10;s_axis_config_tdata=8'b0000_0000;s_axis_config_tvalid=1'b0;#1000;repeat(8)begins_axis_data_tvalid=1'b1;real_data=real_data+16'd1;cnt=cnt+1;==8) s_axis_data_tlast=1'b1;#10;ends_axis_data_tvalid=1'b0;s_axis_data_tlast=1'b0;real_data=16'd0;#1000;$stop;endalways #(5) aclk= ~aclk;fft_top Ufft_top(// input wire aclk// input wire [7 : 0] s_axis_config_tdata// input wire s_axis_config_tvalid// output wire s_axis_config_tready// input wire [31 : 0] s_axis_data_tdata// input wire s_axis_data_tvalid// output wire s_axis_data_tready// input wire s_axis_data_tlast// output wire [31 : 0] m_axis_data_tdata// output wire m_axis_data_tvalid// input wire m_axis_data_tready// output wire m_axis_data_tlast);endmodule

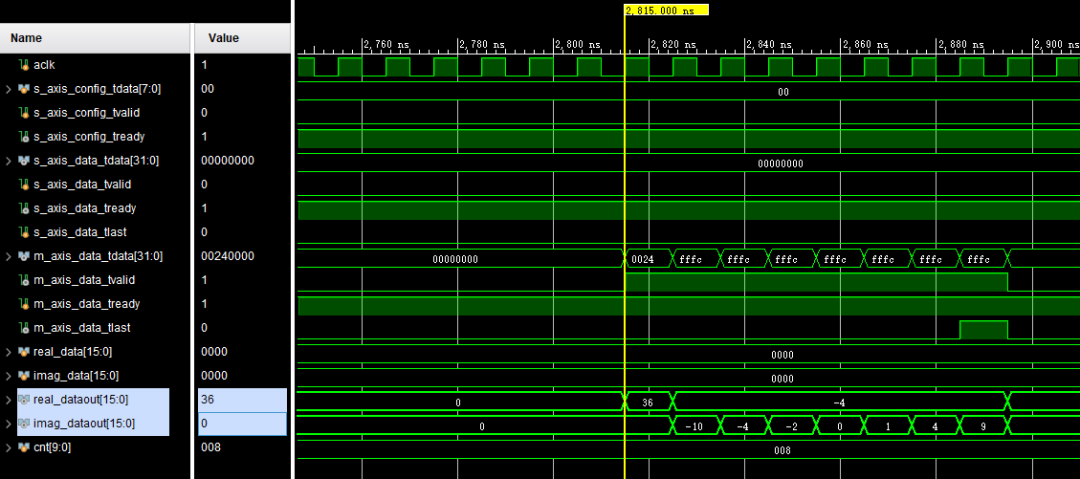

3)仿真結果

Vivado最終的仿真結果為

Real=[36,-4,-4,-4,-4,-4,-4,-4];

Imag=[0,-10,-4,-2,0,1,4,9];

與matlab的計算結果相比實部一樣,除虛部因為數據位的取舍問題以外,正數和負數部分順序相反。

原文標題:Xilinx FFT IP的介紹與仿真

文章出處:【微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

測試

+關注

關注

8文章

5357瀏覽量

126860 -

Xilinx

+關注

關注

71文章

2169瀏覽量

121782 -

IP

+關注

關注

5文章

1715瀏覽量

149715 -

仿真

+關注

關注

50文章

4111瀏覽量

133793

原文標題:Xilinx FFT IP的介紹與仿真

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

xilinx fft ip v7.1 仿真數據于matlab 仿真數據用很大差距,求指教

xilinx FPGA的FFT IP核的調用

xilinx FFT ip核仿真的誤差太大?

基于FPGA的FFT和IFFT IP核應用實例

【Mill】Xilinx ip FFT變換,為什么你的matlab數據無法嚴格比對?——無線通信連載

Modelsim仿真帶有Qsys的FFT和NCO的工程的方法

從Xilinx FFT IP核到FPGA實現OFDM

Xilinx FFT IP介紹與仿真測試

Xilinx FFT IP介紹與仿真測試

評論