數字硬件建模SystemVerilog(五)-文本值

System Verilog 擴展了 Verilog 的 教據類型 , 增強了指定文本值的方法。在介紹文本值之前我們先簡單回憶一下HDL中的四個狀態數據值。

四個狀態數據值

對于RTL建模,System Verilog使用硅中可能出現的值的四值表示。

- 0表示抽象數字低電平,沒有與之相關的電壓或電流。

- 1表示抽象數字高電平,無電壓或電流,

- Z表示抽象數字高阻抗,在多驅動器電路中,值為0或1將覆蓋Z。一些編程運算符和編程語句將Z值視為無關緊要的值。

- X表示多驅動器電路中的未初始化值、不確定值或值沖突。在某些RTL模型上下文中,綜合編譯器將X值視為不關心值。

0、1和Z的值是實際硅中可能存在的值的抽象。

X的值不是實際的硅值。仿真器使用X來表示物理硅在特定情況下的行為的不確定性程度,例如,當仿真無法預測實際硅值是0還是1(或三態器件的Z)時,對于綜合,X值還為設計工程師提供了一種方法來指定“don’t-care”條件,工程師不關心實際硅在特定條件下是否具有0值或1值。

文本值-Literal values (numbers)

System Verilog 擴 展 了 Verilog 的 教 據 類 型 , 增 強 了 指 定 文 本 值 的 方 法。這里的Literal values是直譯,即字面量或常量、文本值。在我理解來看,Literal是指某一數據類型的具體值。

文本值是整數或實數(浮點數)。SystemVerilog提供了幾種指定文本值的方法,還有一些文本值的語義規則,在編寫RTL模型時需要理解這些規則。

文本整數值-Literal integer values

文本整數值是一個整數,沒有小數點。(IEEE 1800 SystemVerilog標準使用術語“整數文本integer literal”而不是“文本整數literal integer”),文本整數可以通過多種方式指定:

- 簡單的十進制整數值

- 二進制、八進制、十進制或十六進制整數值

- 大小文本整數值

- 有符號或無符號文本整數值

仿真和綜合工具都需要知道或假設文本整數值的特定特征。這些特點是:

- 值的位寬度(向量大小)

- 值的有符號性(有符號或無符號)

- 值的基數(也稱為基數)

- 2-state or 4-state value

這些特征影響值的操作和賦值。

簡單的十進制文本整數

文本整數值可以指定為簡單的數字,如數字9,如以下代碼段所示:

result=d+9;

仿真和綜合將簡單的文本數視為:

- 32位寬的值

- 有符號

- 十進制值

- 2態值(沒有位可以是Z或X)

這些特征以及 d 的特征將影響加法的執行方式以及結果賦值的執行方式。

二進制、八進制、十進制和十六進制文本整數。可以為文本整數值指定二進制、八進制、十進制或十六進制的特定基數,該基數使用撇號(’)指定(有時稱為“勾號”),后跟一個字母:b或B表示二進制,o或O表示八進制,d或D表示十進制,h或H表示十六進制。一些示例包括:

result=‘d9+‘h2F+‘bl010;

仿真和綜合將未指定大小的顯式基本文本數視為:

- 32位寬的值

- 無符號值(注意與有符號的簡單文本整數的差異)

- 規定的基準值

- 4態值(任何或所有位可以是X或Z)

二進制值的每個位可以是0、l、X或Z;八進制值的每個3位組可以是0~7、X或Z;十進制值的每個位可以是0~9、X或Z;十六進制值的每個4位組可以是0~9、a~F、X或Z。

有符號文本整數。默認情況下,具有指定基的文本值在操作和賦值中被視為無符號值。可以通過在撇號之后和基本說明符之前添加字母s或S來覆蓋此默認值。

result=’sd9+‘sh2F+‘sbl0l0;

在某些操作和賦值語句中,有符號值與無符號值的處理方式不同。后面討論了有符號和無符號值對運算符和運算的影響。

調整文本整數的大小

默認情況下,在操作、編程語句和賦值語句中,簡單文本數和指定了基數的文本數被視為32位值。此默認值不能準確表示使用其他向量大小的硬件模型。

具有特定基的值也可以指定特定的位寬度。用于表示值的位數在撇號、有符號性和基本規范之前指定:

Result=16‘d9+8‘h2F+4‘bl010;

| 筆記 |

|---|

| 當文本值的大小與賦值語句左側的變量不同時,綜合編譯器和lint檢查器可能會生成警告消息。這些大小不匹配警告消息可能會隱藏其他需要注意的消息。使用顯式大小的文本值將防止大小不匹配警告。 |

| 最佳做法準則3-1 |

|---|

| 在RTL模型中僅使用二進制和十六進制文本整數。這些數字基在數字邏輯中具有直觀的意義 |

八進制值的使用已經過時幾十年了。文本十進制值很容易與其他數字混淆。

有個老工程笑話適用于這里。。。

Thereare10typesofpeopleintheworld,thosethatunderstandbinary,andthosethatdon’t

世界上有10種人,懂二進制的和不懂二進制的

不匹配的大小和值檢測規則

下面的規則是編寫HDL代碼中最難檢查的,也是大部分人不注意的!

指定一個位寬不同于表示該值所需位數的文本整數是合法的。例如:

SystemVerilog始終調整該值以匹配指定的大小。這些規則是:

- 當大小小于值的位時,值的最左邊位被截斷。

- 當大小大于該值的位數時,該值保持擴展。使用以下規則填充附加位:

- 如果值的最左邊位為0或l,則額外的高位用0填充。

- 如果該值的最左邊位為Z,則附加的高位用Z填充

- 如果該值的最左側位為X,則額外的高位用X填充。

請注意,即使將文本整數指定為有符號整數,該值也不會進行符號擴展。符號擴展發生在有符號文本值用于操作和賦值語句時,這將在后面中討論。

前面代碼段的值調整為:

4’hFACE//截斷為4’hE

16’sh8//延伸至16’sh0008

32’bZ//擴展到32’bZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZ

| 最佳做法準則3-2 |

|---|

| 在綜合RTL模型之前,將lint檢查程序(也稱為建模規則檢查器)與仿真結合使用。 |

當發生截斷時,仿真器可能會報告非致命警告消息,但不需要報告警告。仿真器將無聲地擴展文本值以匹配大小,而不會生成任何警告。存在在仿真中驗證設計功能而未意識到尺寸/值不匹配的風險。使用lint檢查器時將顯示文本值中的任何不匹配。

附加文本值規則

問號(?)可以用來代替Z來表示高阻抗。在大多數情況下,字母Z是表示高阻抗的更直觀的方式。然而,有些運算符和編程語句使用高阻抗值來表示不關心狀態。對于這些不關心的情況,使用問號表示高阻抗會更直觀。

在文本值中的任何位置都可以使用分割以下的字符(_),仿真、綜合編譯器等都可以解析,同時SystemVerilog代碼的工具會忽略下劃線。在數字中添加一個下劃線有助于使長數字更具可讀性,尤其是二進制值-下劃線也可用于顯示值中的子字段,

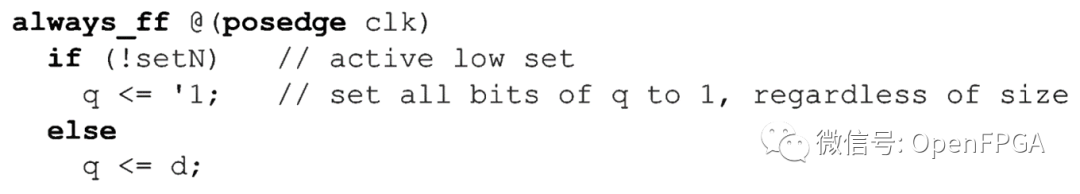

向量填充文本值

SystemVerilog提供了一種特殊形式的無大小文本整數,它將任何大小的向量的所有位設置為0、l、X或Z。文本值的向量大小根據其上下文自動確定。

- ‘0用0填充左側的所有位

- ‘1用1填充左側的所有位

- ‘z或’Z用z填充左側的所有位T

- ‘x或’X用x填充左側的所有位

使用向量填充文本整數的示例如下:

向量填充文本整數是建模可伸縮設計的一個重要構造,對于不同的設計配置,可具有不同的向量寬度。本章后面章節討論了可配置向量大小的建模。

這些向量填充文本整數不是傳統Verilog的一部分。它們是作為原始Verilog語言的SystemVeri1og擴展的一部分添加的。

浮點文本值(實數)

SystemVerilog將浮點值稱為實數。實數使用64位雙精度浮點表示。文本浮點值是通過在文本數字中使用小數點來指定的。必須在小數點的兩側指定一個值。

3.1567

5.0

0.5

| 筆記 |

|---|

| RTL綜合編譯器通常不支持實(浮點)表達式。高級綜合(HLS)工具可用于復雜的算法設計。浮點和定點設計不在本系列RTL建模的范圍之內- |

審核編輯 :李倩

-

Verilog

+關注

關注

28文章

1351瀏覽量

110100 -

System

+關注

關注

0文章

165瀏覽量

36943 -

整數

+關注

關注

0文章

13瀏覽量

6511

原文標題:SystemVerilog(五)-文本值

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog 與 ASIC 設計的關系 Verilog 代碼優化技巧

Verilog 測試平臺設計方法 Verilog FPGA開發指南

Verilog與VHDL的比較 Verilog HDL編程技巧

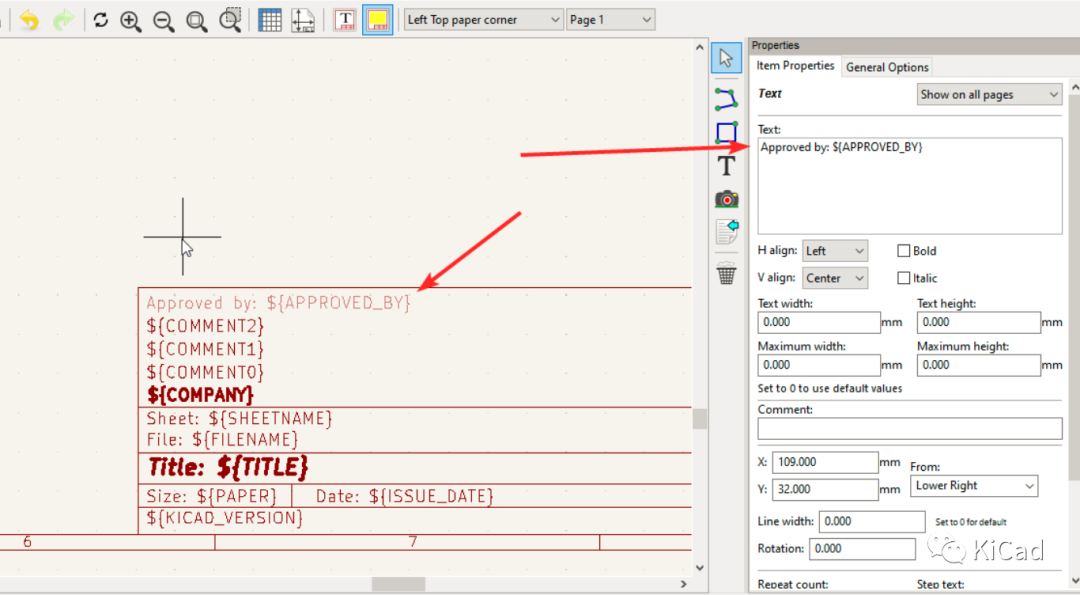

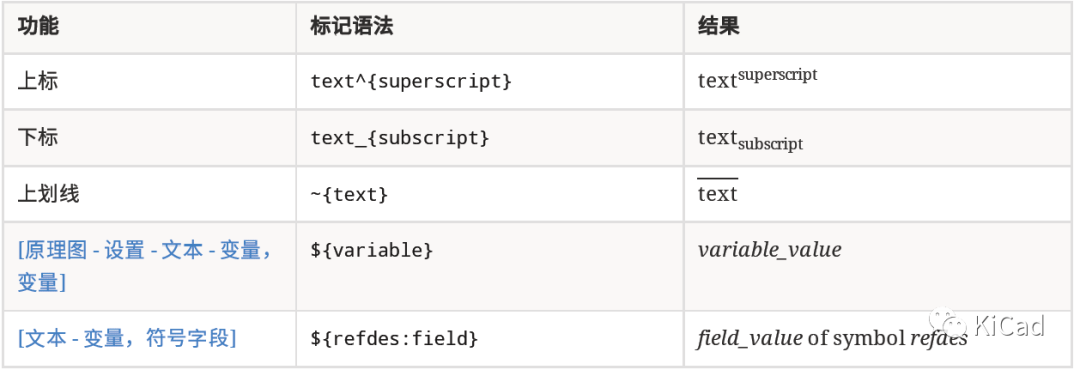

圖紙模板中的文本變量

Verilog硬件描述語言參考手冊

如何利用Verilog-A開發器件模型

verilog與其他編程語言的接口機制

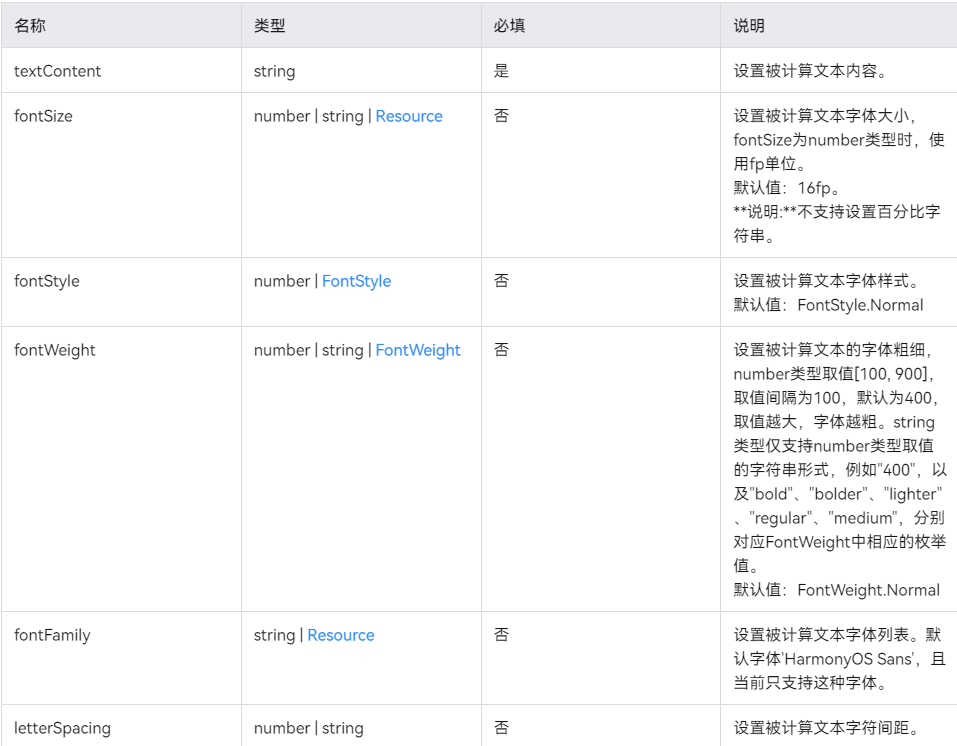

鴻蒙UI界面——@ohos.measure (文本計算)

System Verilog-文本值

System Verilog-文本值

評論