如何將總諧波畸變(THD)控制在10%以下,一直是LED照明領域普遍關心的問題。功率不僅可以作為非線性負載,還可以產生含有諧波的失真波形。這種諧波可能會影響其他電子系統的正常工作。所以測量這些諧波的整體效應很重要。總諧波失真可以為我們提供信號w.r.t.基波分量中諧波成分的相關信息。更高的THD意味著較大的失真或者輸入電源端的失真越大或電源質量越低。

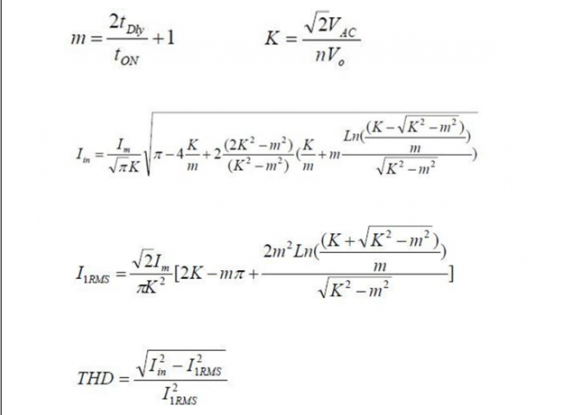

因此,我不得不使用15W射燈(絕緣)設計來測試一個設計方法,該設計方案采用針對7個串聯LED配置的TPS92314器件,可通過150~265VAC輸入提供3.1V正向電壓和0.7A額定電流。按照下列指示,我在240V的AC輸入電壓下實現了8.7%的THD在進行實際實施之前,請查閱應用手冊,了解完成該測試所需的兩個重要方程式。

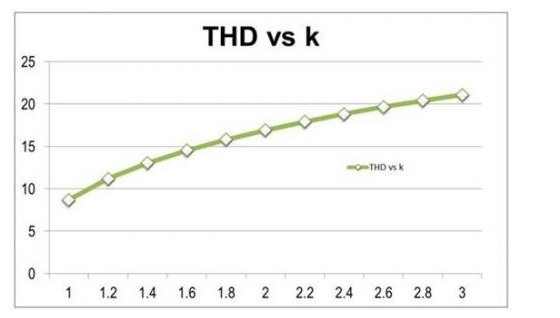

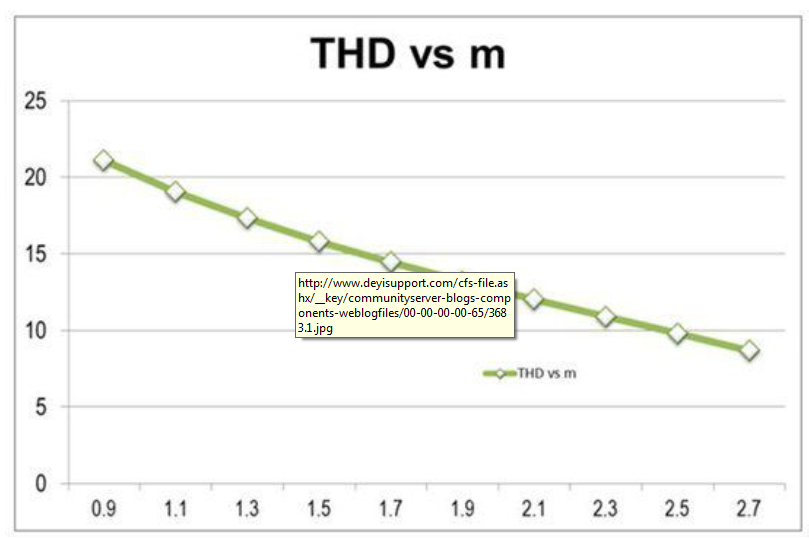

在本例中,k等于1.68,我們可通過上述方程繪制出當k=1.68時THD與“m”的關系曲線圖。

從下圖中我們可以看到,當k增大時(在m《k的一個具體“m”值下),THD也會增大。

因此,重新看一下“m”和“k”的定義,我們就會發現,增大匝數比(n=Np/Ns)及轉換器延遲時間,可降低THD。除這兩個參數外,EMI濾波器設計也可對THD的改善起到非常重要的作用。用來降低總諧波失真的三個設計注意事項包括:

1.增加變壓器匝數比(n=Np/Ns)可增大反射電壓。這會提高成本和開關FET的電壓應力。在本特例中,我們將匝數比調成近似于10,以保持反射電壓約為174V。FET額定值必須高于過沖電壓、(LED最大電壓+輸出二極管壓降)×匝數比加上峰值AC輸入電壓的總和。計算結果將近640V[=50V+(20+0.5)*10+1.414*265]。我使用的是700V額定FET以及約為16pF的低漏源極電容。

2.增加轉換器延遲時間可降低THD。我將電阻器從計算的5.6k變為6.2k。延遲時間取決于變壓器的初級線圈電感以及FET的漏源極電容。所得延遲時間約為280ns。

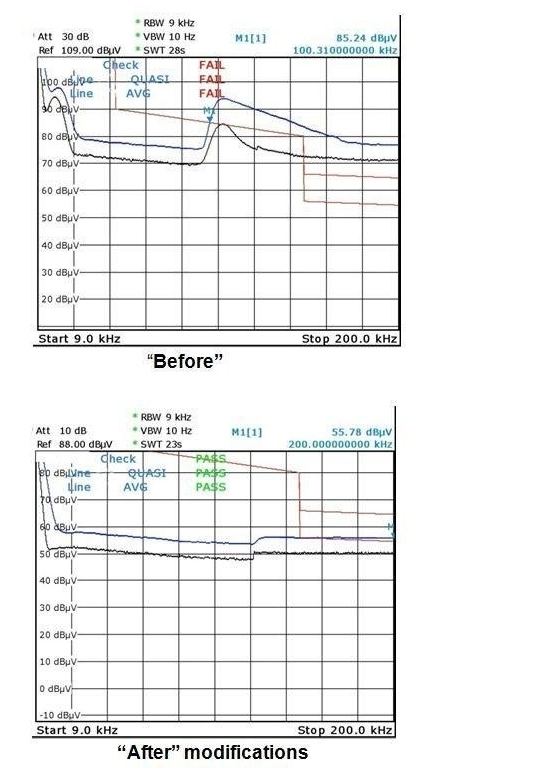

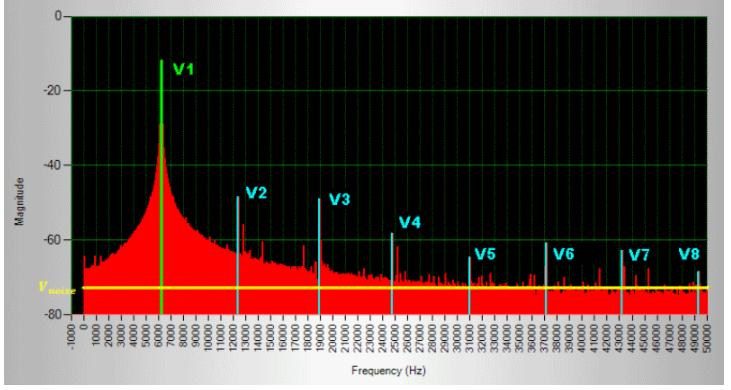

3.在輸入端添加EMI濾波器。在本例中,將帶有275VAC、68nF電容器的80mH共模線圈添加至輸入端,并在該橋接之后添加一個包含1mH鼓電感器和兩個400V、33nF電容器的π濾波器。這可幫助我們實現2.15kHz的差分濾波器轉角頻率。在線路阻抗穩定網絡和頻譜分析儀的幫助下,我在查看傳導EMI曲線后,在多次迭代中計算這些值。在最初沒有任何線路濾波器的情況下,峰值在100kHz(轉換器開關頻率)下約為85dBuV。該頻譜已經超出了CISPR15B類標準的限值,直到頻率為1MHz時才降至限值以內。因此不得不采用EMI濾波器。我逐步增加共模線圈值,并觀察其對THD性能的影響(將電容器增大到一定程度后會降低PF性能)。最后,該值達到了80mH和68nF左右,而截止頻率則為2.15kHz,衰減超過30dB,使100kHz下的峰值降至55.78dBuV。這樣,頻譜不僅下降了,而且它還使燈光達到了CISPR15標準(符合準峰值和平均限值兩種要求)。進行這一改變后,THD改善至大約9~10%。與共模線圈相關的漏電感幫我實現了差分濾波器。

通過進行上述改變,我才得以在240V的輸入電壓下實現8.5%的THD以及0.98的PF,輸出電壓為21.8V。在相同設計中的輸出端(18.8V輸出)使用六個LED,我們在240V電壓下實現了9%的THD。通過EE1685磁芯(匝數180)實現了80mH的EMI濾波器。主變壓器的初級電感為2mH,峰值主電流約為0.5A。

本試驗所用LED驅動裝置為TPS92314,此一次側控制離線LED驅動裝置主要用于低成本照明應用(少量的外部元件)。該系統采用固定導通時間結構,無需復雜的補償技術,即可實現自然功率因數校正。另外,諧振谷值開關還能降低電磁干擾,提高系統效率。其他優良的特性還包括一次側電流限制,VCC過壓保護和欠壓鎖定,輸出LED過壓保護,控制器關閉等。

-

led

+關注

關注

242文章

23277瀏覽量

660876 -

濾波器

+關注

關注

161文章

7817瀏覽量

178128 -

諧波

+關注

關注

7文章

824瀏覽量

41788

發布評論請先 登錄

相關推薦

總諧波失真和噪聲曲線詳解

理解總諧波失真和噪聲曲線

將LED總諧波失真降至10%以下的方法

將LED總諧波失真降至10%以下的方法

評論