PCB 設計指南被創建為電路設計工程師的基準,以滿足行業標準。遵循這些指南將確保更好的可制造性和強大的產品性能。

概述了設計指南以提高產品的可測試性和可制造性。它們提供了改善 PCB 信號完整性和電磁兼容性 (EMC) 的建議,從而提高產品的整體性能。

本文將概述各種 PCB 設計指南,以提高 PCB 的信號完整性。遵循這些指南將有助于工程師進行穩健的PCB制造。

PCB中的信號完整性

信號完整性是電信號通過傳輸線從驅動器傳輸到接收器而沒有任何失真的能力。失真的信號會對板上的相鄰信號產生噪聲,并降低電路操作的整體效率。在高速電路的情況下,信號失真會變得很明顯,并且會損害 PCB 的整體性能。

因此,設計符合必要監管標準的 PCB 非常重要。具有強大信號完整性的精心設計的 PCB 將避免由于衰減、接地反彈和阻抗中斷而導致的任何信號衰減。

如果電路設計僅包括低速信號,則幾乎沒有需要管理的信號完整性問題。但在高速設計中,由于上升時間要求較短,信號會失真。因此,我們需要了解某些信號完整性問題才能了解推薦的 PCB 設計指南。

- 反射

由源傳輸到接收器的部分信號功率通過跡線反射回源的過程稱為反射。它會導致振蕩,從而導致信號失真。每當電路中出現阻抗變化時,信號走線就會產生反射效應。這反過來又增加了過沖和下沖問題。

- 振鈴、過沖和下沖

振鈴是由于 PCB 走線中的信號反射而導致電壓或電流信號發生不希望的振蕩的過程。如果發送信號的值大于上升信號中的實際值,則發生過沖。類似地,當發送信號低于下降信號中的實際值時,就會發生下沖。所有這些過程都會使 PCB 中的傳輸信號失真。

- 相聲

在高速設計中,緊密布線的相鄰信號可能會在不經意間相互影響,從而導致信號失真。這種失真主要是由于 PCB 中電場或磁場的耦合造成的。在電路板相鄰層中路由的信號之間也可能發生串擾。

- 信號衰減

由于 PCB 的走線電阻和介電損耗,通過 PCB 導體從源傳輸到負載的信號會經歷信號衰減或能量損失。在高頻下,信號衰減要高得多,需要事先考慮設計來處理這個問題。

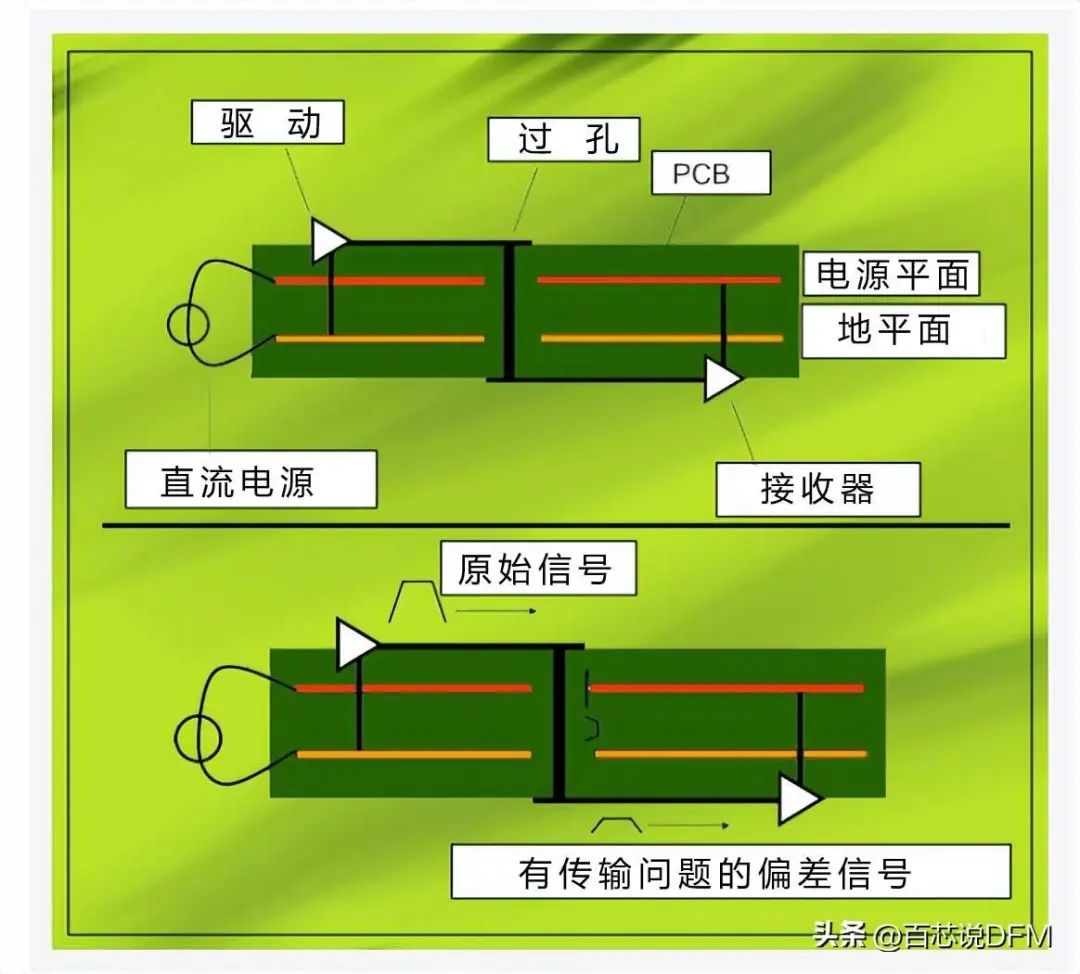

- 傳播延遲和信號偏斜

PCB 走線上的信號傳播延遲是該特定信號從源傳輸到負載所需的時間。它取決于 PCB 介電常數和走線幾何形狀。當存在延遲失配時,一組信號中會出現信號偏移。它顯著影響電路設計中時鐘和數據信號的性能。

- 接地反彈或同時開關噪聲

當 PCB 上的多個組件同時在高低狀態之間切換時,電源和接地路徑中的電壓會下降。這導致組件的電源和接地引腳上的電壓降低。噪聲容限也會降低,這可能會導致電路的錯誤切換。

PCB 信號完整性指南

線路阻抗的不連續性會導致上述大多數信號完整性問題。在走線分支、返回信號路徑中的分裂以及路徑中的過孔或短截線等情況下路由信號時會出現這種阻抗不連續性。

減少因阻抗不匹配導致的信號失真的指南如下:

- 在源頭提供正確的終端電阻。

- 使用較小的微通孔可顯著減少通孔和短截線造成的信號失真。

- 保持短線的最小走線長度。

- 避免跟蹤分支并使用適當的路由拓撲。

減少串擾效應的設計指南如下:

- 在適用的設計部分使用差分信號將消除串擾效應。

- 最小化并行路由信號的長度。

- 根據路由指南,在允許的最大距離上隔開相鄰信號。

- 確保傳輸線與接地層足夠接近,以避免相鄰信號發生任何不必要的耦合。

- 相鄰平面中信號的正交路由可以在很大程度上幫助避免串擾。

以下是減少信號衰減問題的設計指南:

- 選擇低損耗介電材料和最佳電阻走線,以減少信號衰減誤差。

- 在設計中使用放大器和中繼器有助于提高信號強度。

以下是減少傳播延遲和信號偏移的設計指南:

- 避免使用具有較大介電常數的基板,以幫助減少信號的傳播延遲。

- 通過正確的走線長度匹配,可以最小化信號總線的偏移。

下面列出了減少接地反彈和開關噪聲問題的設計指南:

- 在決定電路板層的疊層時,將電源層和接地層彼此靠近放置。

- 去耦電容不是可選的,必須在本地接地上實現。

- 最好將去耦帽放置在元件引腳附近,并盡可能使用短引線的器件封裝。

- 添加必要的限流電阻以避免短路或過載。

本文展示了PCB 設計指南如何幫助提高電路板的信號完整性。它涉及一系列步驟,例如基板選擇、疊層設計、組件考慮和布局設計。此外,還有多種仿真工具可用于分析 PCB 的信號完整性問題。因此,仔細遵循所有這些指導方針將導致 PCB 具有改進的信號完整性和持久的性能。

Ken Ghadia是Technotronix的銷售工程師。

-

pcb

+關注

關注

4324文章

23139瀏覽量

398902 -

信號完整性

+關注

關注

68文章

1412瀏覽量

95546

發布評論請先 登錄

相關推薦

基于PCB信號完整性的反射設計

如何提高PCB中的信號完整性

如何提高PCB中的信號完整性

評論